1、參考https://forums.xilinx.com/t5/%E5%B5%8C%E5%85%A5%E5%BC%8F-%E7%A1%AC%E4%BB...

按照官方說明,copy數據速率基本為系統ddr的帶寬。

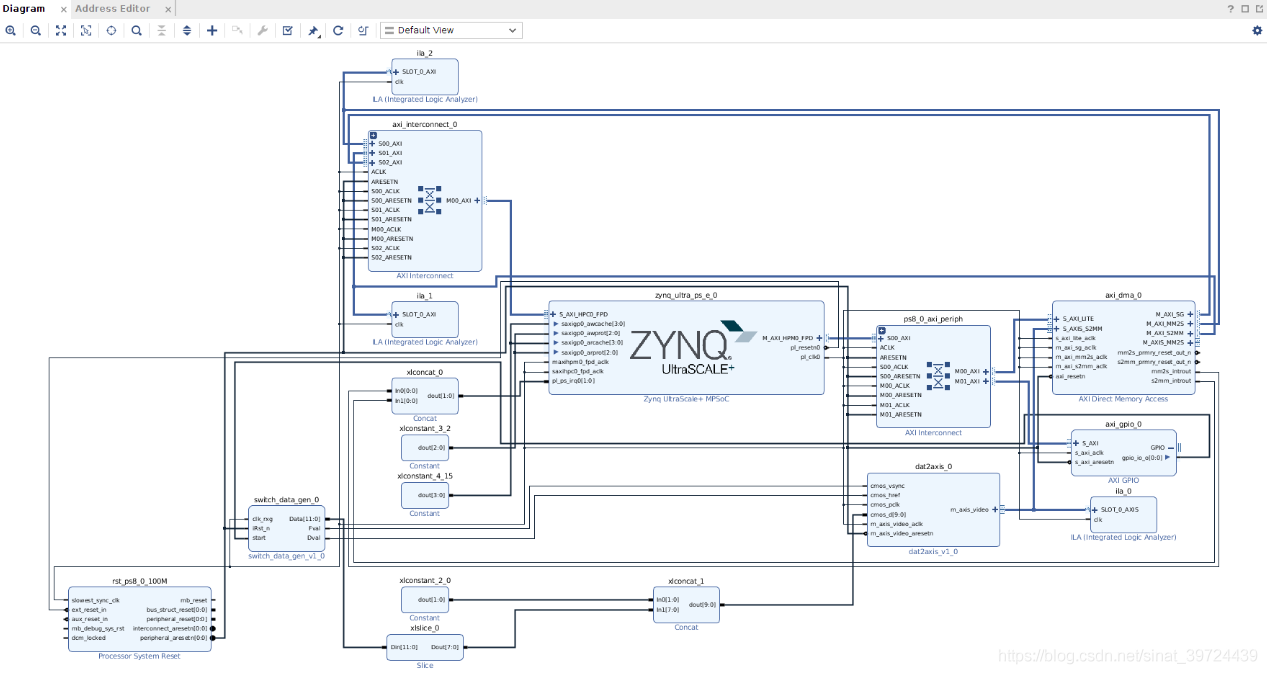

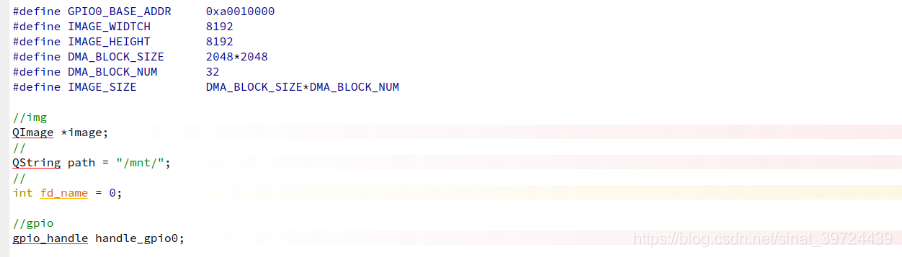

2、工程 生成數據大小2048X2048 4MB 也就是一次dma數據大小,一次dma數據的大小與axi-dma核中buffer lenght registr有關,長度最大26,也就是2^26個字節,為64MB,工程中加入ila核用來調試。

3、生成bit后,導出xsa文件。

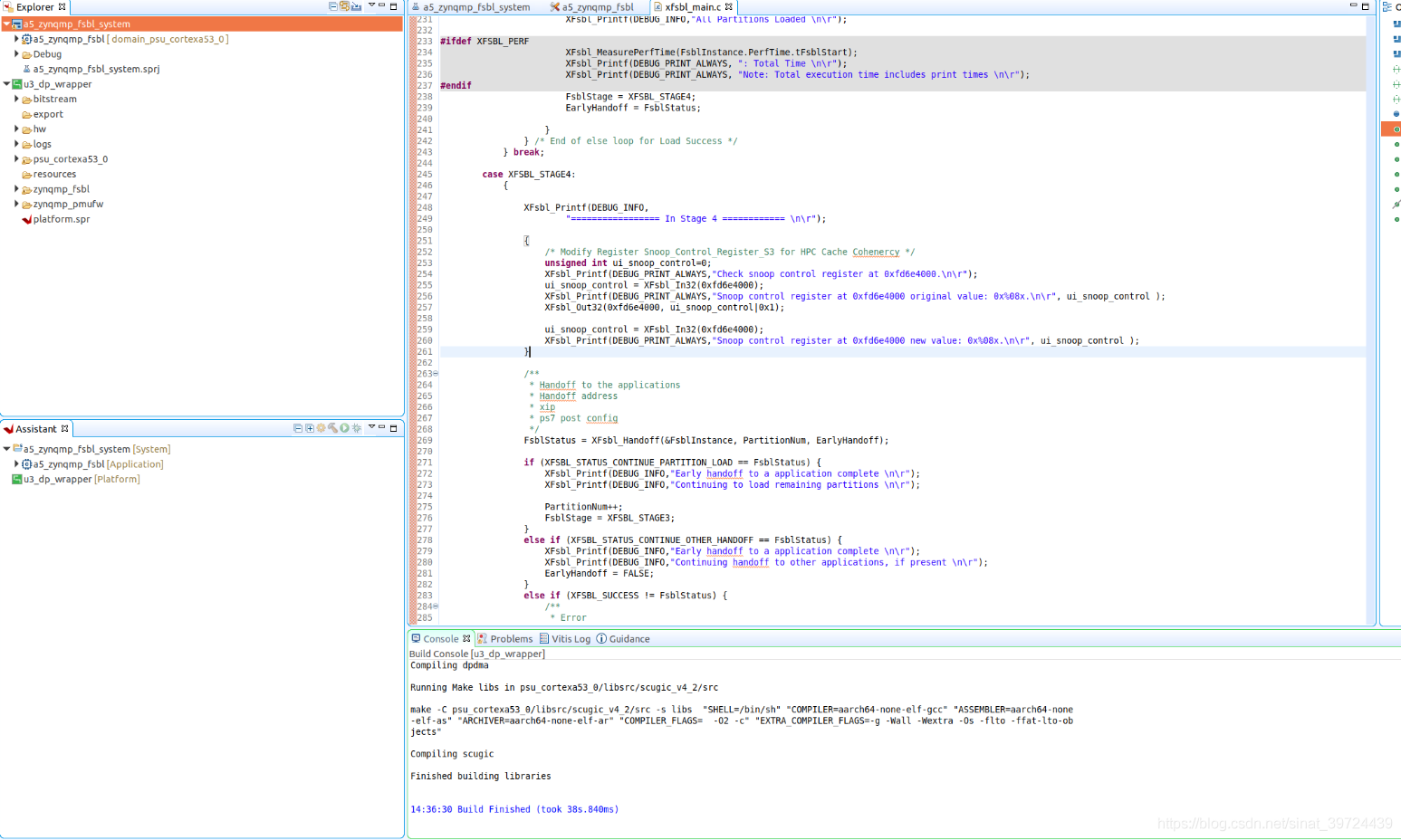

4、在vitis中應用xsa文件,新建a5_zynqmp_fsbl工程,按照官方說明,修改sfsbl_main.c,并編譯,在debug文件夾中可以找到a5_zynqmp_fsbl.elf文件。

5、在petalinux環境中新建工程,參考以前的博客,直到petalinux-build。

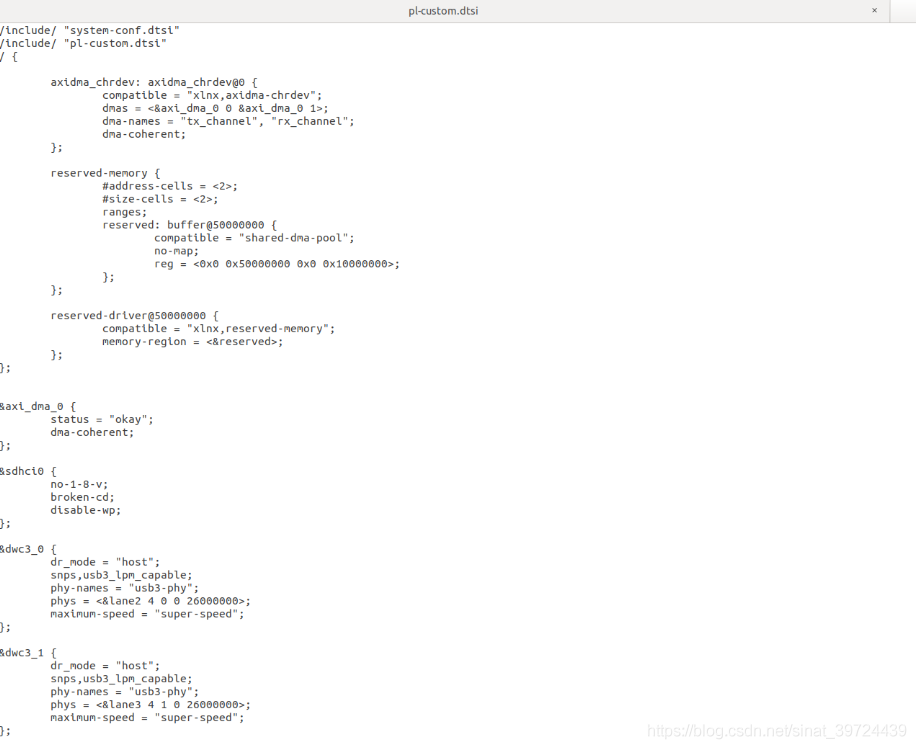

6、修改設備樹

7、重新petalinux-build。

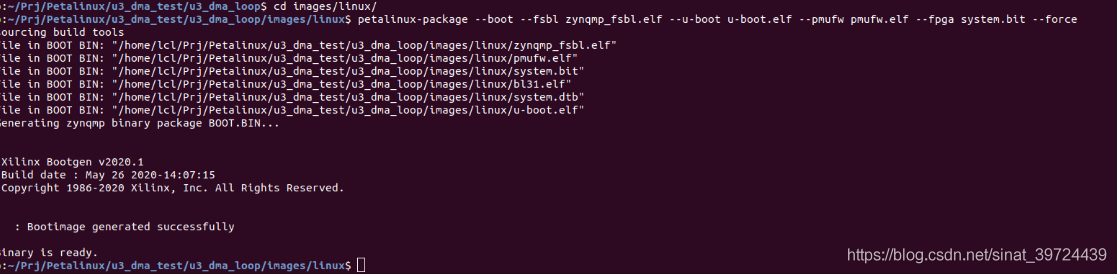

8、在image/linux文件夾下

9、拷貝出bl31.elf boot.scr image.ub pmufw.elf system.bit system.dtb u-boot.elf 七個文件,以及vitis中生成的a5_zynqmp_fsbl.elf共8個文件,到linux_dma_test.

10、在petalinux工程中,build文件夾中拷貝bootgen.bif文件,并修改成如下

11、新建regs.init

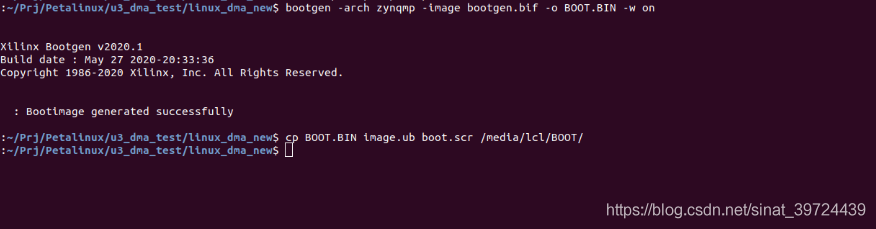

12、生成BOOT.BIN,然后一起將BOOT.BIN image.ub和boot.scr復制到sd卡。

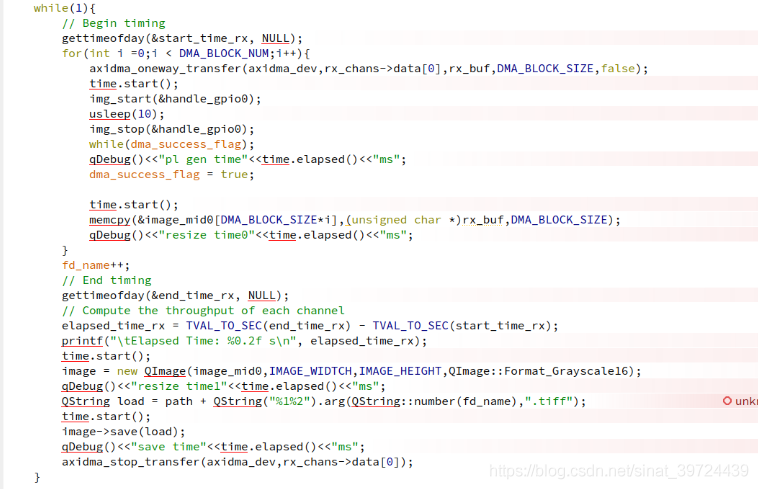

13、測試

14、上電開機,加載axi-dma的驅動,將3.0U盤掛在到mnt下

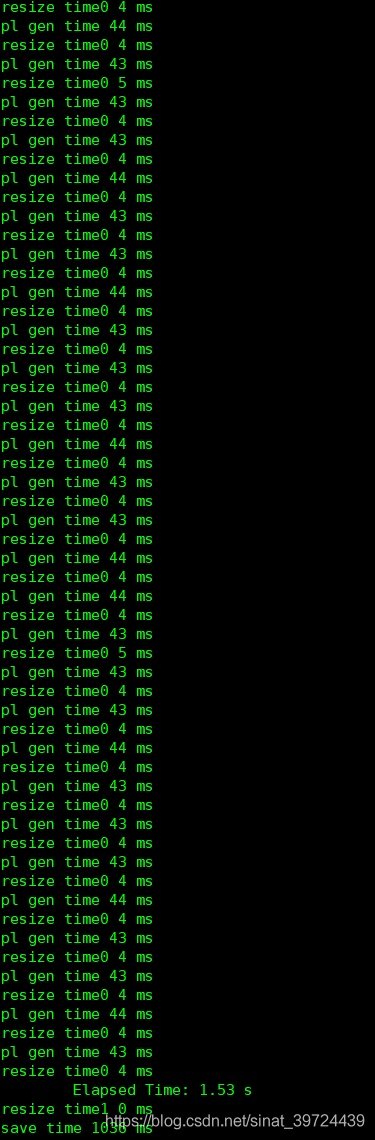

由以上可以看出,pl生成一張4MB的數據耗時43ms,將4MB數據由dma讀緩沖區copy到內核緩沖區耗時4ms,基本接近ddr的帶寬。整個鏈路中的帶寬完全受限于U盤的存儲速度。

15、U盤中的圖片,大小128MB,數據正確。

審核編輯:符乾江

-

文件

+關注

關注

1文章

565瀏覽量

24729 -

編譯

+關注

關注

0文章

657瀏覽量

32852

發布評論請先 登錄

相關推薦

單片機中的幾種環形緩沖區的分析和實現

ESP8266有雙緩沖區嗎?

創建DMA通道時,能否將DMA緩沖區的大小指定為8字節,并將DMA緩沖區的編號指定為1?

如何確保在負載量小于或大于DMA緩沖區大小的情況下完全提交數據?

FX3多通道DMA在切換DMA緩沖區時仍會丟失數據,為什么?

stm32野火開發板上做USB通信,PC端USB的緩沖區和串口緩沖區的大小是多少?

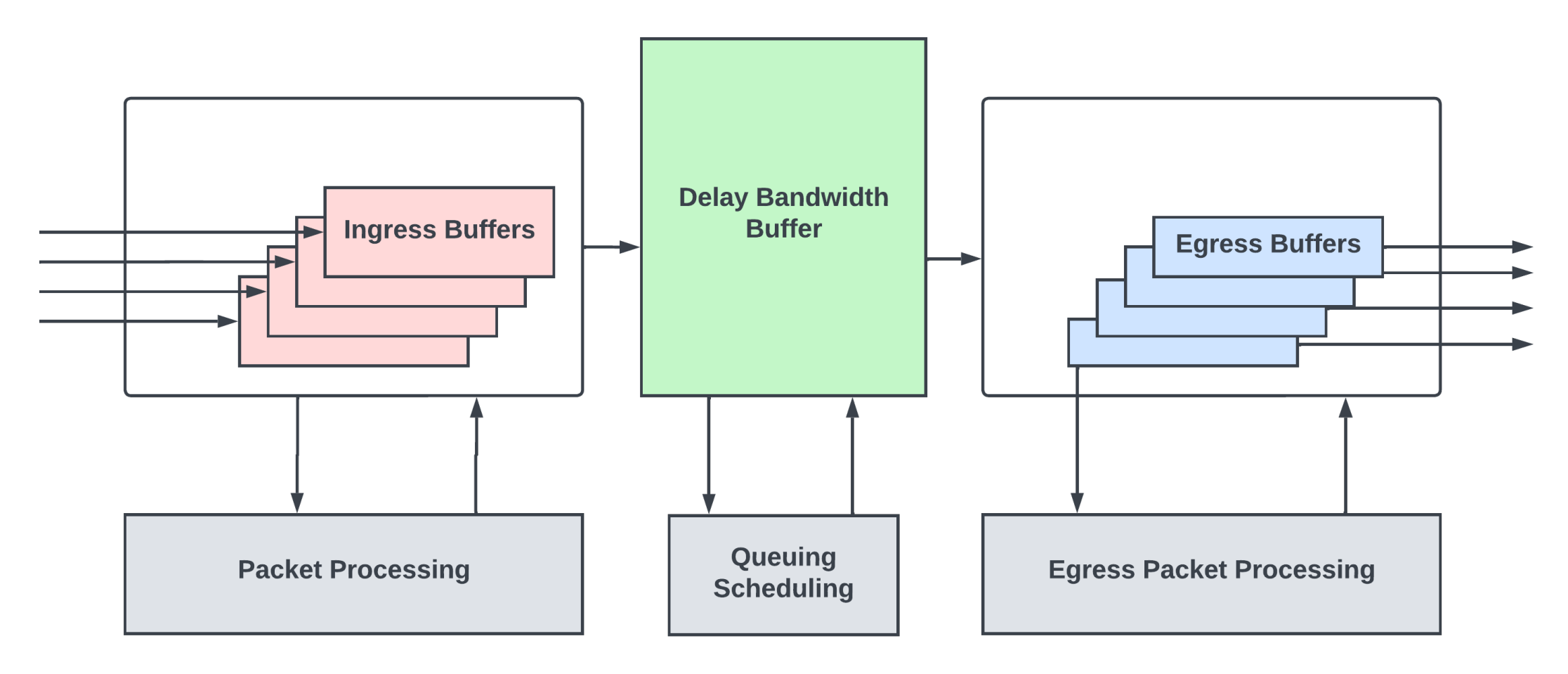

交換機與路由器緩沖區:尋找完美大小

Petalinux加速axi-dma內核驅動緩沖區讀過程

Petalinux加速axi-dma內核驅動緩沖區讀過程

評論