1、參考

https://cas.tudelft.nl/fpga_tdc/TDC_basic.html

2、原理

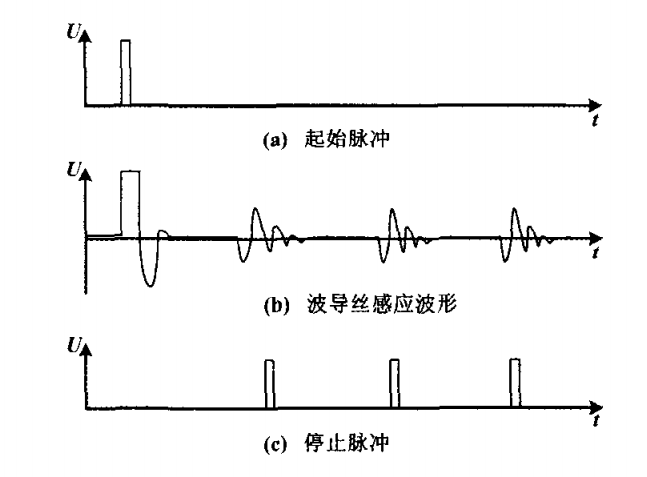

采用FPGA的CARRY4進位單元,每個CARRY4的COUT連接到下一個CARRY4的CIN,這樣級聯(lián)起來,形成延時鏈;每個COUT做為抽頭輸出到觸發(fā)器,通過本地時鐘進行數(shù)據(jù)采樣。假定每個延時鏈的延時是固定的(最后需要標定),可通過采樣值大致估算所測信號與本地時鐘上升沿之間的間隔,當?shù)玫竭m當?shù)臉硕ê螅色@得較高的精度。

3、當前測試的芯片是XC7K325TFFG900 -2

仿真中的carry4 除第一級外,其他的carry4輸出到輸入延遲固定都是53ps,但是這是4個進位的延遲時間,只是vivado仿真工具有限制,且需要后仿真。

4、源代碼

頂層

tdc_top.v

module tdc_top#(

parameter STAGE = 200,

parameter GAP_BITS = 8

)(

input wire sg_start,

input wire clk_sys,

input wire reset ,

output wire cs_gap,

output wire [GAP_BITS-1:0] value_gap

);

wire clk_bufg;

clk_wiz_0 clk_wiz_0_inst(

.clk_out1(clk_bufg),

.clk_in1(clk_sys)

);

wire valid_pre;

wire valid;

wire [STAGE-1:0] value_latch;

wire bin_cs;

wire [GAP_BITS-1:0] bin;

wire sg_bufr;

BUFR #(

.BUFR_DIVIDE("BYPASS"), // Values: "BYPASS, 1, 2, 3, 4, 5, 6, 7, 8"

.SIM_DEVICE("7SERIES") // Must be set to "7SERIES"

)

BUFR_INST (

.O(sg_bufr), // 1-bit output: Clock output port

.CE(1'b1), // 1-bit input: Active high, clock enable (Divided modes only)

.CLR(1'b0), // 1-bit input: Active high, asynchronous clear (Divided modes only)

.I(sg_start) // 1-bit input: Clock buffer input driven by an IBUF, MMCM or local interconnect

);

FDCE #(

.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)

)

FDCE_INST2 (

.Q(valid_pre), // 1-bit Data output

.C(clk_bufg), // 1-bit Clock input

.CE(1'b1), // 1-bit Clock enable input

.CLR(1'b0), // 1-bit Asynchronous clear input

.D(sg_bufr) // 1-bit Data input

);

FDCE #(

.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)

)

FDCE_INST3 (

.Q(valid), // 1-bit Data output

.C(clk_bufg), // 1-bit Clock input

.CE(1'b1), // 1-bit Clock enable input

.CLR(1'b0), // 1-bit Asynchronous clear input

.D(valid_pre) // 1-bit Data input

);

line_tdc#(

.STAGE (STAGE)

) line_tdc_inst(

.sg_start (sg_bufr),

.clk_bufg (clk_bufg),

.reset (reset),

.value_latch (value_latch)

);

latch2bin#(

.GAP_BITS (GAP_BITS)

) latch2bin_inst(

.clk_bufg (clk_bufg),

.reset (reset),

.valid (valid),

.value_latch (value_latch),

.bin_cs (cs_gap),

.bin (value_gap)

);

延遲線代碼

line_tdc.v

module line_tdc#(

parameter STAGE = 256

)(

input wire sg_start,

input wire clk_bufg,

input wire reset,

output wire [STAGE - 1:0] value_latch

);

wire [STAGE - 1:0] dat_reg0;

wire [STAGE - 1:0] dat_reg1;

genvar i;

generate

for (i = 0; i if(i == 0) begin :carry4_first

CARRY4 CARRY4_INST (

.CO (dat_reg0[3:0]), // 4-bit carry out

.O (), // 4-bit carry chain XOR data out

.CI (1'b0), // 1-bit carry cascade input

.CYINIT (sg_start), // 1-bit carry initialization

.DI (4'b0000), // 4-bit carry-MUX data in

.S (4'b1111) // 4-bit carry-MUX select input

);

end

if (i > 0) begin :carry4_others

CARRY4 CARRY4_OTHERS (

.CO (dat_reg0[4*(i+1)-1:4*i]), // 4-bit carry out

.O (), // 4-bit carry chain XOR data out

.CI (dat_reg0[4*i-1]), // 1-bit carry cascade input

.CYINIT (1'b0), // 1-bit carry initialization

.DI (4'b0000), // 4-bit carry-MUX data in

.S (4'b1111) // 4-bit carry-MUX select input

);

end

end

endgenerate

genvar j;

generate

for (j = 0; j FDRE #(

.INIT (1'b0) // Initial value of register (1'b0 or 1'b1)

) FDRE_INST0 (

.Q (dat_reg1[j]), // 1-bit Data output

.C (clk_bufg), // 1-bit Clock input

.CE (1'b1), // 1-bit Clock enable input

.R (reset), // 1-bit Synchronous reset input

.D (dat_reg0[j]) // 1-bit Data input

);

FDRE #(

.INIT (1'b0) // Initial value of register (1'b0 or 1'b1)

) FDRE_INST1 (

.Q (value_latch[j]), // 1-bit Data output

.C (clk_bufg), // 1-bit Clock input

.CE (1'b1), // 1-bit Clock enable input

.R (reset), // 1-bit Synchronous reset input

.D (dat_reg1[j]) // 1-bit Data input

);

end

endgenerate

endmodule

延遲線數(shù)字碼轉(zhuǎn)換二進制輸出

latch2bin.v

module latch2bin#(

parameter GAP_BITS = 8

)(

input wire clk_bufg,

input wire reset,

input wire valid,

input wire [(2**GAP_BITS)-1:0] value_latch,

output reg bin_cs,

output reg [GAP_BITS-1:0] bin

);

(* *)reg [(2**GAP_BITS)-2:0] decoding [0:GAP_BITS-4];

(* *)reg [GAP_BITS:0] binary [0:GAP_BITS-3];

(* *)reg [GAP_BITS-2:0] data_valid;

(* *)reg [15:0] decode_final;

(* *)reg [GAP_BITS-1:0] bin_final;

(* *)reg [3:0] ones;

(* *)reg [GAP_BITS:0] binary_r;

always@(*) begin

decoding[0] = value_latch[(2**GAP_BITS)-2:0];

data_valid[0] end

genvar i;

generate

for (i = 0; i always@(posedge clk_bufg) begin

if(reset) begin

decoding[i+1] binary[i+1] data_valid[i+1] end

else begin

binary[i+1][GAP_BITS:GAP_BITS-1-i] data_valid[i+1] if(decoding[i][((2**(GAP_BITS-i))-2)/2]==1'b1) begin

decoding[i+1][((2**(GAP_BITS-i))-2)/2-1:0] end

else begin

decoding[i+1][((2**(GAP_BITS-i))-2)/2-1:0] end

end

end

end

endgenerate

always@(posedge clk_bufg) begin

if(reset) begin

ones data_valid[GAP_BITS-3] binary[GAP_BITS-3] bin_final end

else begin

ones decoding[GAP_BITS-4][0] + decoding[GAP_BITS-4][1] + decoding[GAP_BITS-4][2] + decoding[GAP_BITS-4][3] +

decoding[GAP_BITS-4][4] + decoding[GAP_BITS-4][5] + decoding[GAP_BITS-4][6] + decoding[GAP_BITS-4][7] +

decoding[GAP_BITS-4][8] + decoding[GAP_BITS-4][9] + decoding[GAP_BITS-4][10] + decoding[GAP_BITS-4][11] +

decoding[GAP_BITS-4][12] + decoding[GAP_BITS-4][13] + decoding[GAP_BITS-4][14] + decoding[GAP_BITS-4][15];

data_valid[GAP_BITS-3] binary[GAP_BITS-3]

data_valid[GAP_BITS-2] bin_final end

end

always@(posedge clk_bufg) begin

if(reset) begin

bin_cs bin end

else begin

if(data_valid[GAP_BITS-2] == 1'b1) begin

bin_cs bin end

else begin

bin_cs bin end

end

end

endmodule

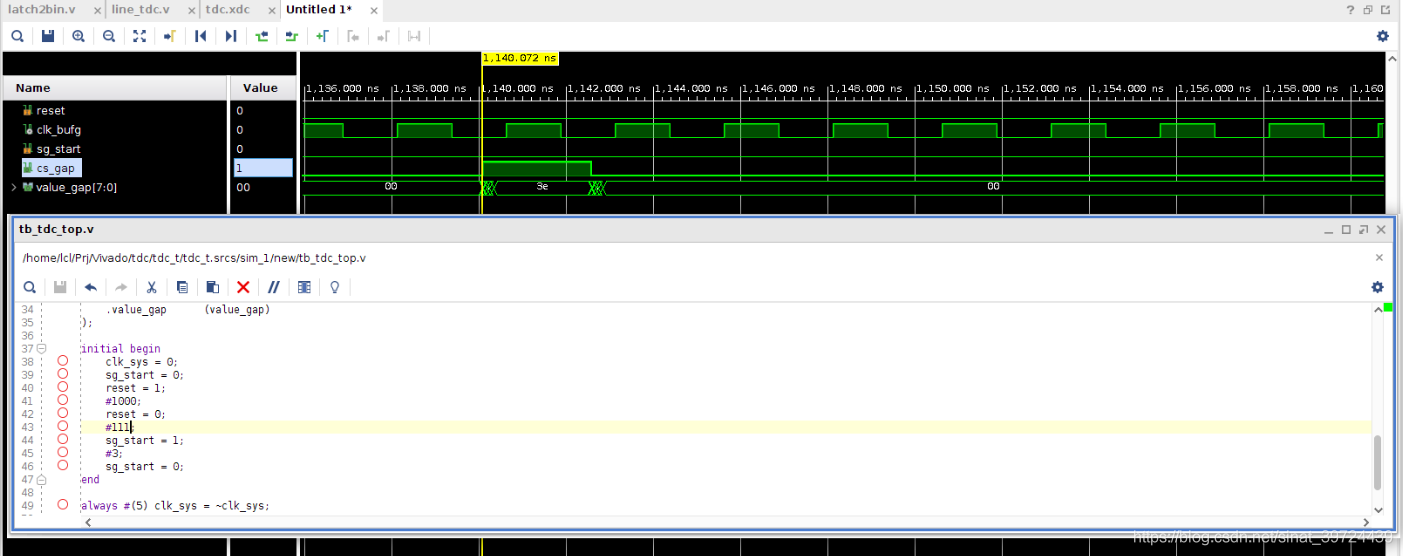

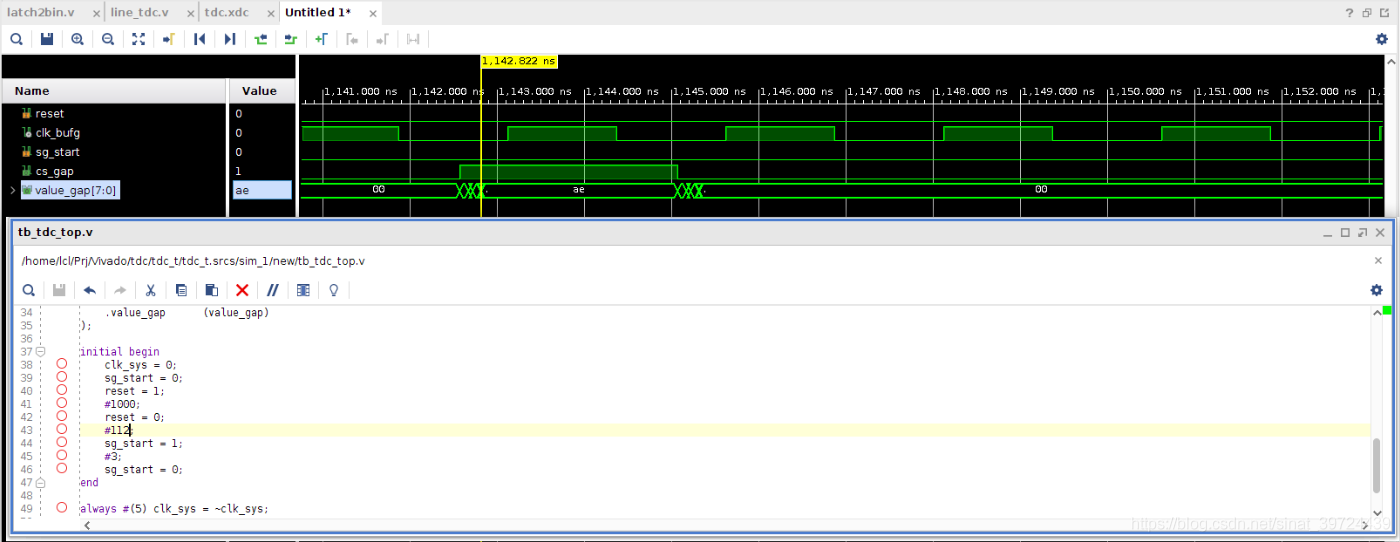

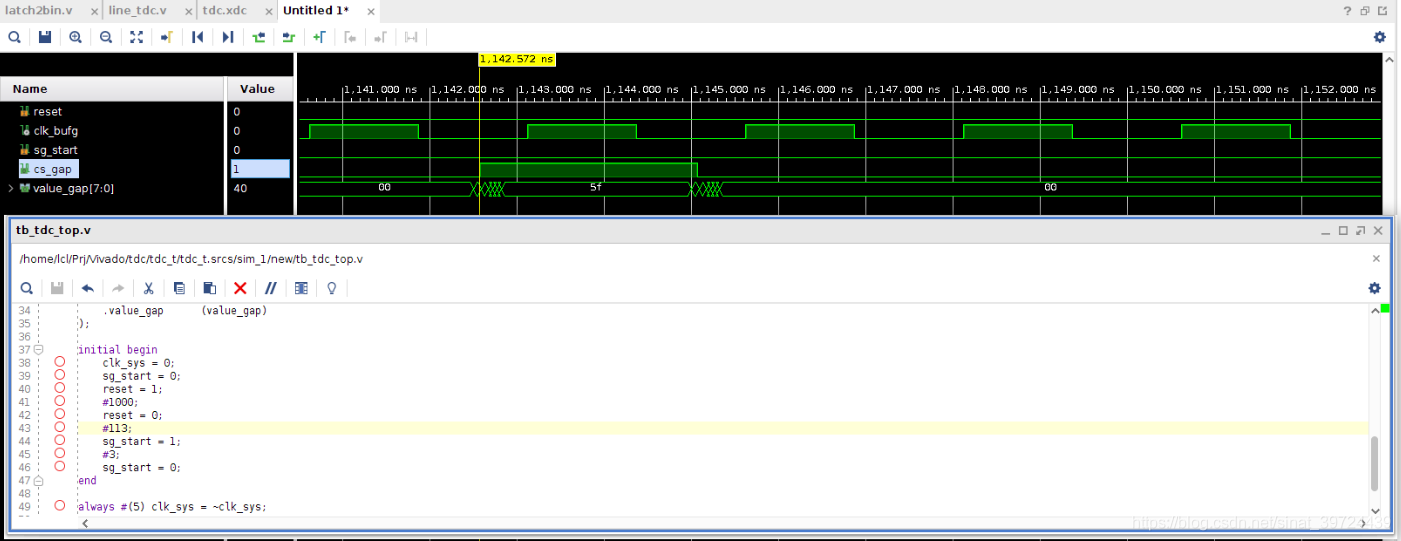

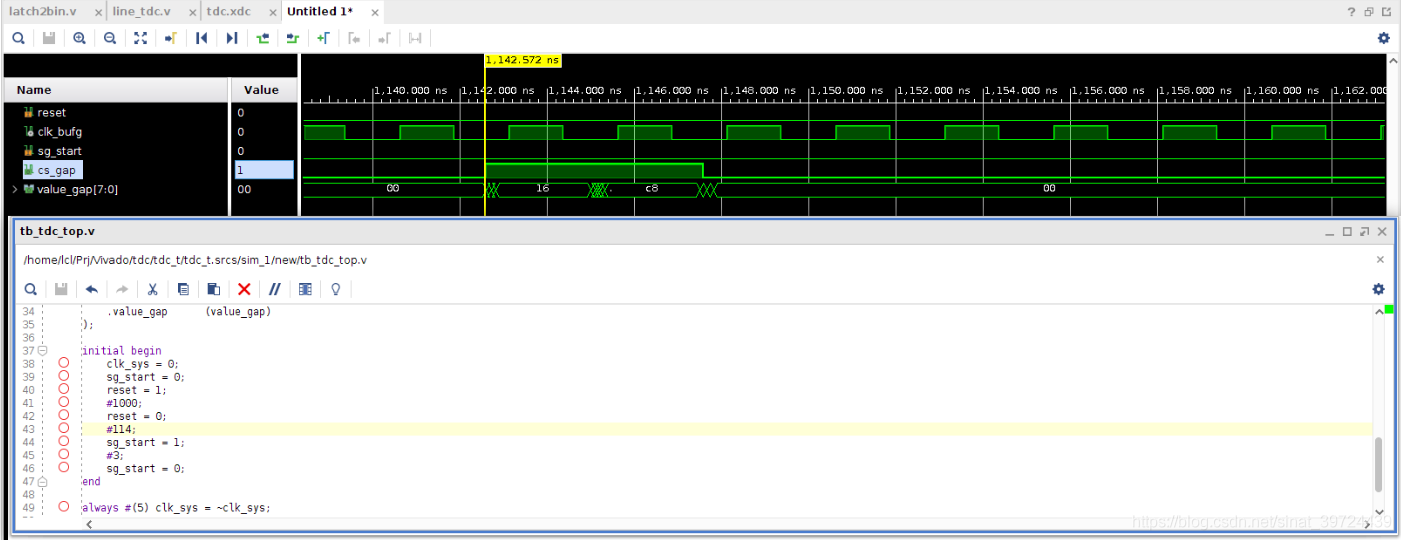

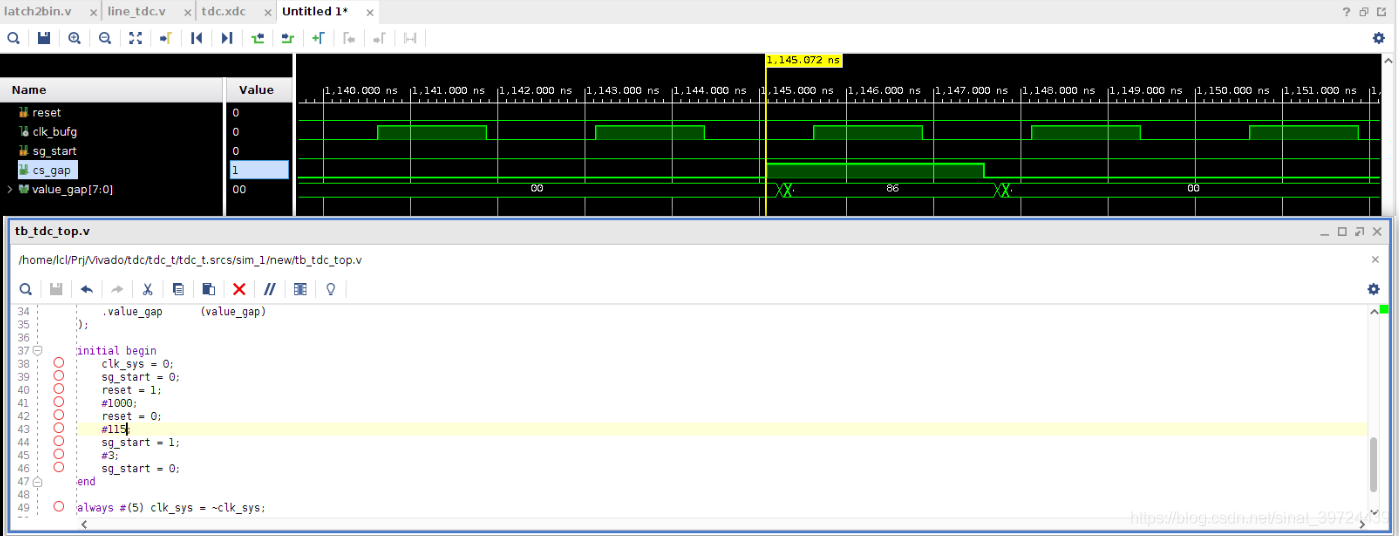

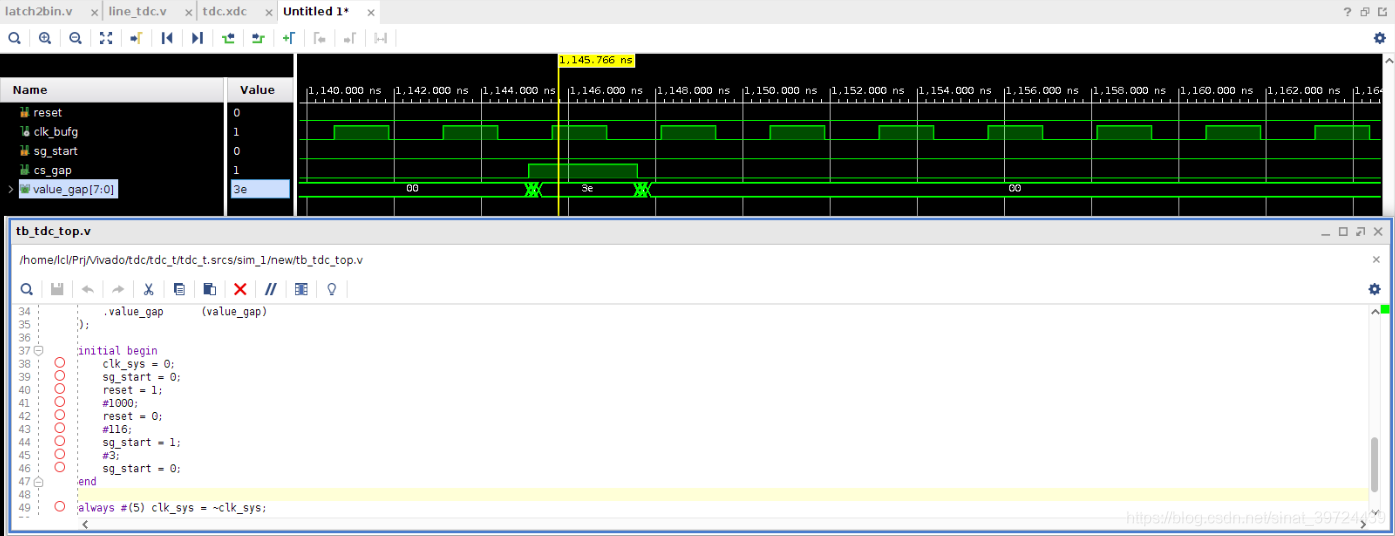

測試

tb_tdc_top.v

module tb_tdc_top;

reg clk_sys;

reg sg_start;

reg reset;

wire [7:0] value_gap;

tdc_top tdc_top_inst(

.sg_start (sg_start),

.clk_sys (clk_sys),

.reset (reset),

.value_gap (value_gap)

);

initial begin

clk_sys = 0;

sg_start = 0;

reset = 1;

#1000;

reset = 0;

#116;

sg_start = 1;

#3;

sg_start = 0;

end

always #(5) clk_sys = ~clk_sys;

endmodule

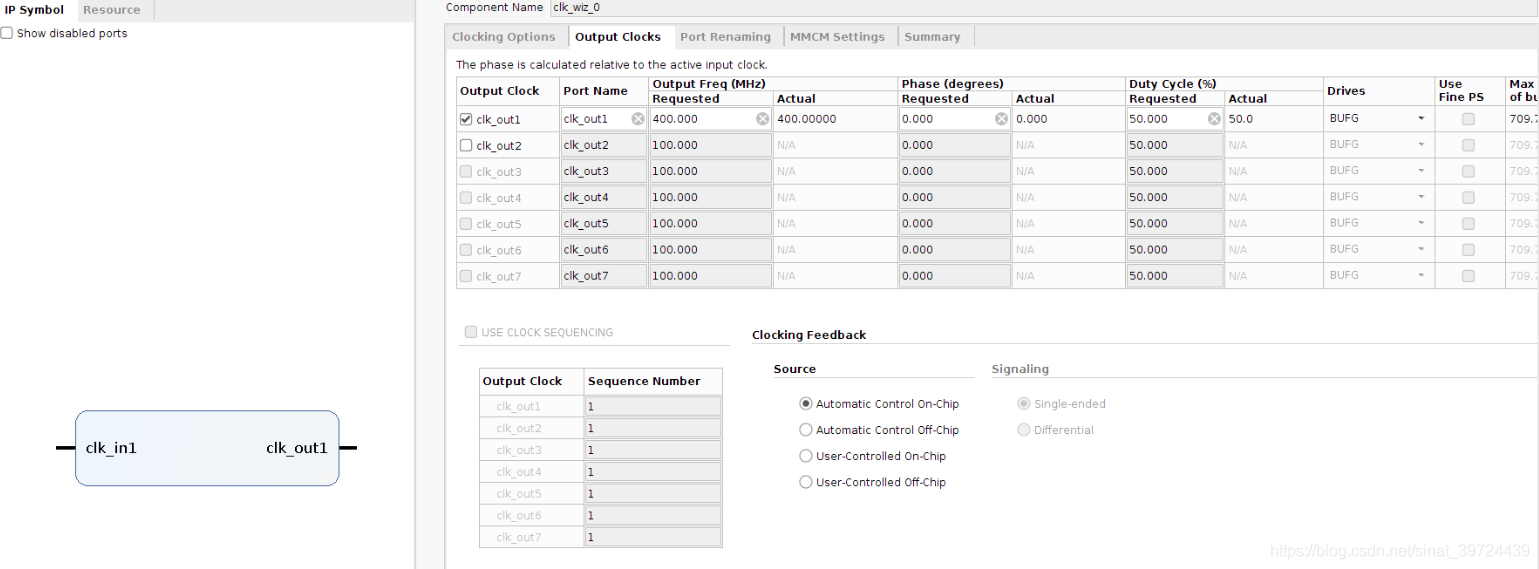

時鐘模塊100M輸入,400M輸出,并經(jīng)過BUFG資源。

由于每個carry4的延遲時間是53ps,每個時鐘周期是2.5ns,最多需要50個carry4級聯(lián)即可。

5、約束

手冊上有寫,對于carry4的第一級約束后,下一級的carry4會以最鄰近的擺放。tdc.xdc

set_property PACKAGE_PIN AD21 [get_ports reset]

set_property PACKAGE_PIN AE23 [get_ports sg_start]

set_property PACKAGE_PIN AD23 [get_ports clk_sys]

set_property IOSTANDARD LVCMOS33 [get_ports {value_gap[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {value_gap[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {value_gap[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {value_gap[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {value_gap[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {value_gap[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {value_gap[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {value_gap[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports cs_gap]

set_property IOSTANDARD LVCMOS33 [get_ports reset]

set_property IOSTANDARD LVCMOS33 [get_ports sg_start]

set_property IOSTANDARD LVCMOS33 [get_ports clk_sys]

set_property LOC SLICE_X0Y0 [get_cells line_tdc_inst/genblk1[0].carry4_first.CARRY4_INST]

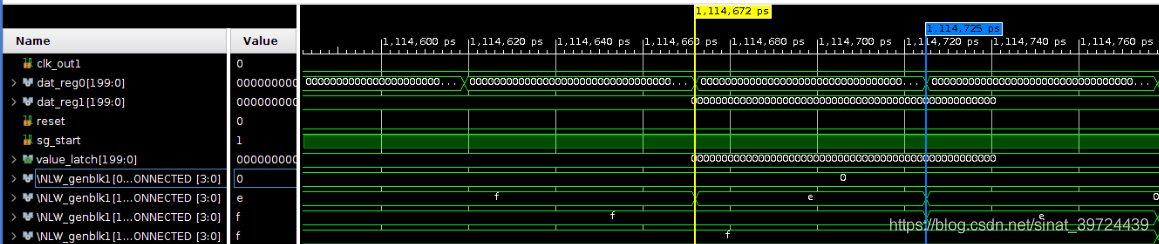

6、后仿真測試結(jié)果

審核編輯:湯梓紅

-

FPGA

+關注

關注

1646文章

22059瀏覽量

619160 -

觸發(fā)器

+關注

關注

14文章

2039瀏覽量

62190 -

TDC

+關注

關注

0文章

40瀏覽量

13995

發(fā)布評論請先 登錄

通過什么方法能獲得關于Ethercat方面的設計方案和設計資料

基于FPGA的AM調(diào)制系統(tǒng)設計方案

TDC1000-TDC7200 GUI調(diào)試工具求助

電磁環(huán)境模擬系統(tǒng)設計方案

TDC1000能否用于多普勒測流?

TDC1000是否對超聲換能器有要求?

求助,關于TDC1000和TDC7200測試溫度遇到的疑問求解

TDC1000-TDC7200EVM外接START和STOP信號時如何不受TDC1000的信號影響?

使用TDC去測量pwm兩個波形相位延時時間,如何去設計TDC7201的外圍電路?

TDC芯片數(shù)據(jù)手冊及官方參考例程

FPGA延時Verilog HDL實現(xiàn)

LM4890采用差分設計方案,為什么沒有聲音?怎么解決?

MS1205N——激光測距用高精度時間測量(TDC)電路

評論