閱讀本文前,請(qǐng)先閱讀:

(1)【教程】Xilinx Vivado/Vitis 2020.1創(chuàng)建最簡(jiǎn)單的MicroBlaze工程運(yùn)行Hello World C語(yǔ)言程序(不使用外部DDR3內(nèi)存),并固化到SPI Flash

https://blog.csdn.net/ZLK1214/article/details/111824576

(2)Xilinx 2020.1 MIG核讀寫(xiě)DDR3內(nèi)存,新建工程時(shí)配置MIG核的完整步驟

https://blog.csdn.net/ZLK1214/article/details/111349678

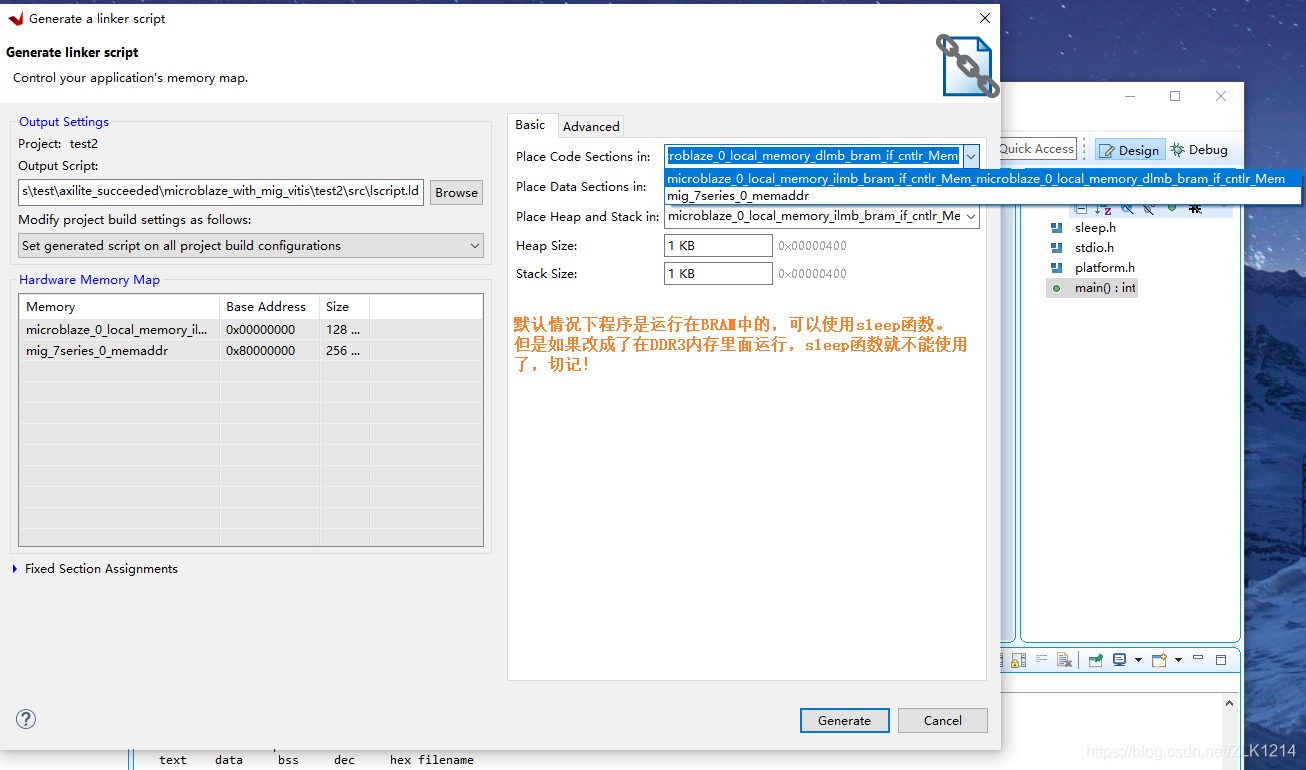

添加了DDR3內(nèi)存以后,程序既可以運(yùn)行在BRAM里面,也可以運(yùn)行在DDR3內(nèi)存里面。但如果運(yùn)行在DDR3內(nèi)存里面,固化起來(lái)會(huì)比較麻煩,需要借助SREC SPI Bootloader。

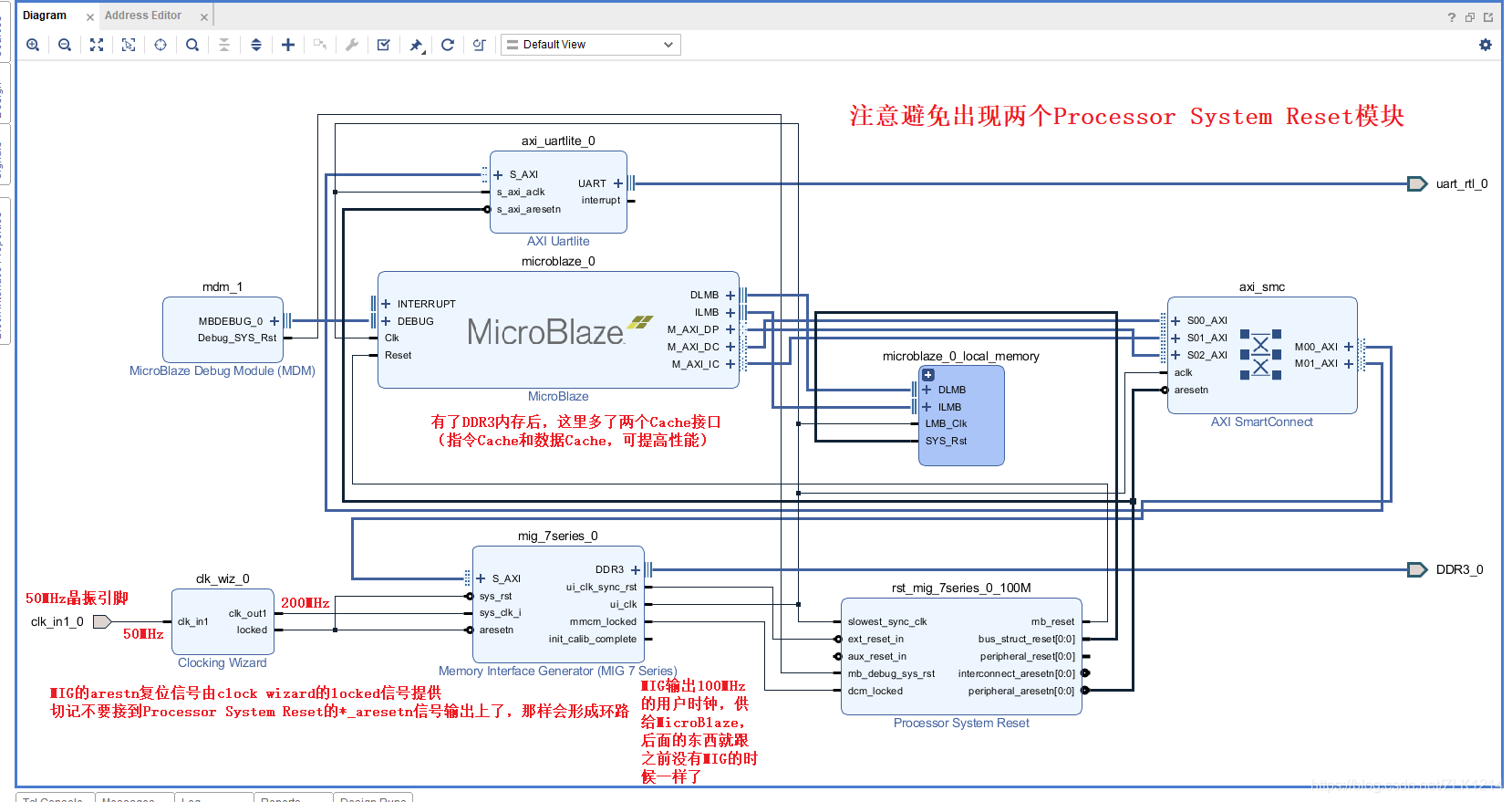

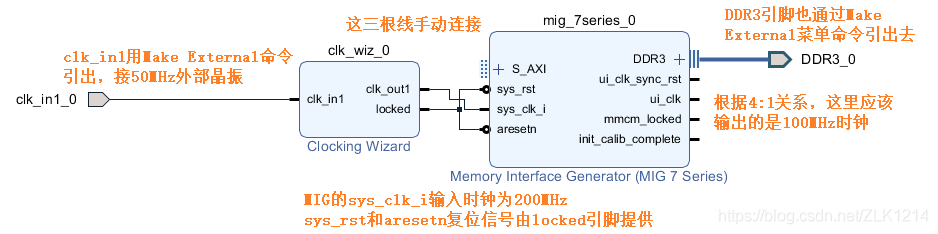

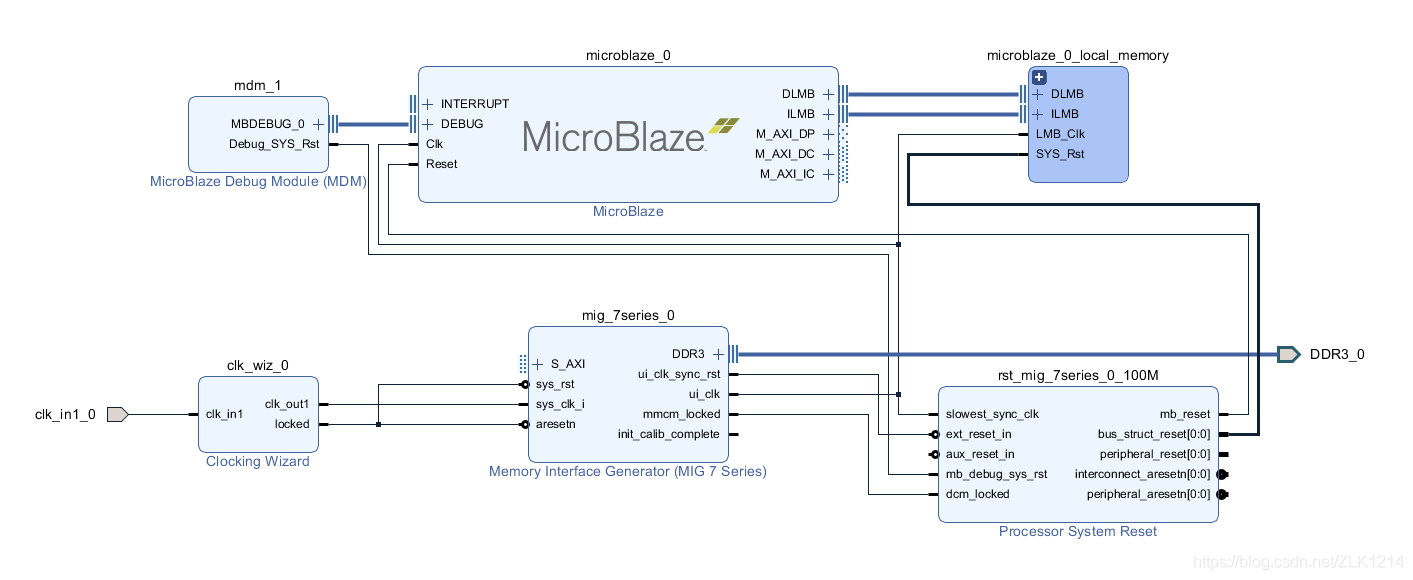

建立帶DDR3內(nèi)存的MicroBlaze工程的方法很簡(jiǎn)單:以不帶DDR3的工程(1)為基礎(chǔ),只需要在Clocking Wizard和Processor System Reset之間插入一個(gè)MIG IP核就可以了。

原本,Clocking Wizard輸出的時(shí)鐘是100MHz,是直接接到Processor System Reset上的。

修改后,兩者中間插入了一個(gè)MIG。Clocking Wizard的時(shí)鐘輸出變成了200MHz,給MIG提供時(shí)鐘。在MIG的內(nèi)部由PLL倍頻到400MHz驅(qū)動(dòng)外部DDR3內(nèi)存,然后再分頻到100MHz從ui_clk引腳輸出出來(lái),給Processor System Reset提供時(shí)鐘。

修改后,MicroBlaze的運(yùn)行頻率沒(méi)有變,仍然是100MHz。

建立工程的時(shí)候一定要小心使用Vivado的自動(dòng)連線的功能,操作不當(dāng)?shù)脑捄苋菀桩a(chǎn)生兩個(gè)Processor System Reset。

下面詳細(xì)說(shuō)明一下工程的建立步驟。

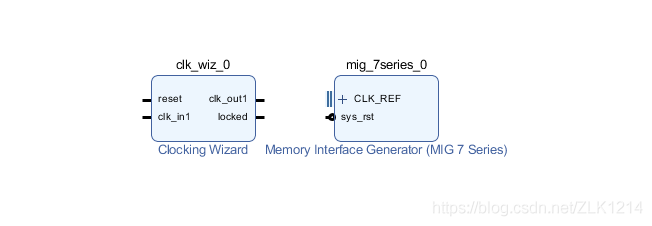

首先在空白Block Design里面添加Clocking Wizard和MIG IP核:

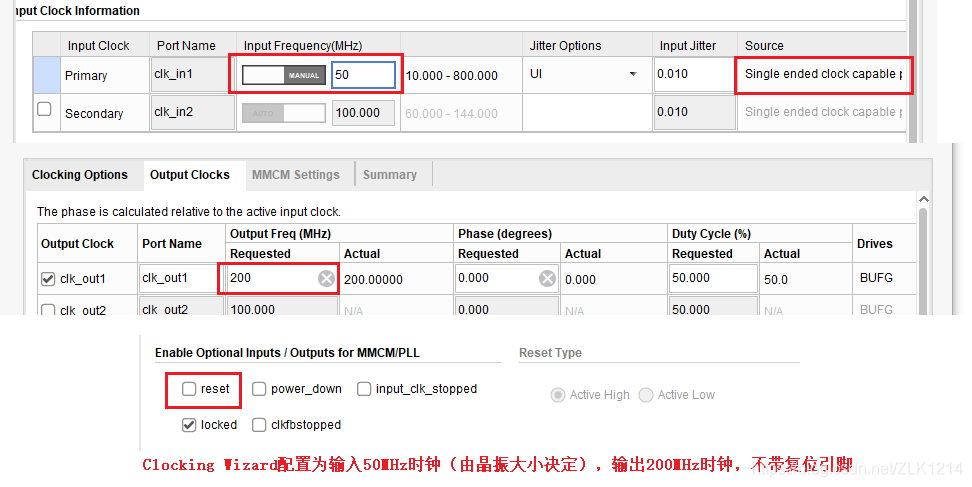

修改Clocking Wizard的配置:

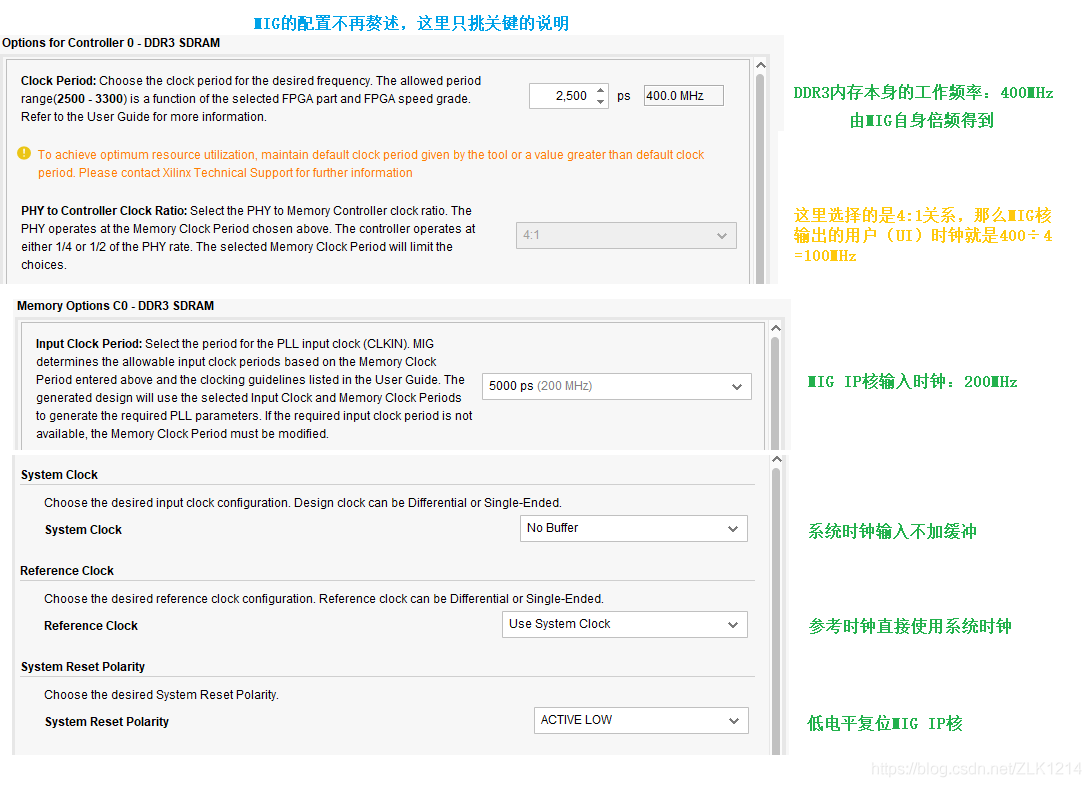

MIG的詳細(xì)配置請(qǐng)參考上面的文章(2),關(guān)鍵配置單獨(dú)挑出來(lái)說(shuō)明一下:

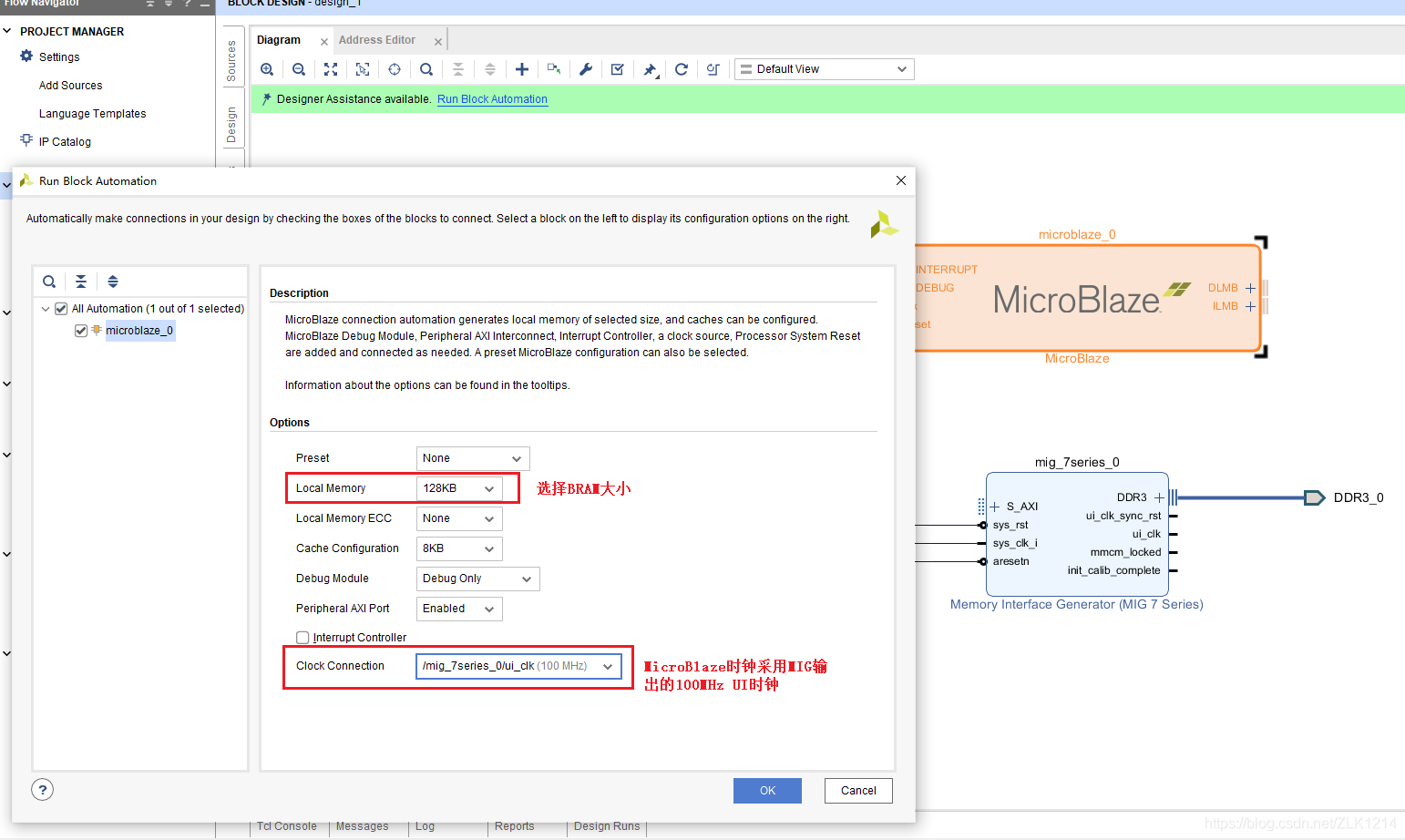

現(xiàn)在可以添加MicroBlaze核了,添加后點(diǎn)擊Run Block Automation,請(qǐng)注意時(shí)鐘的選擇:

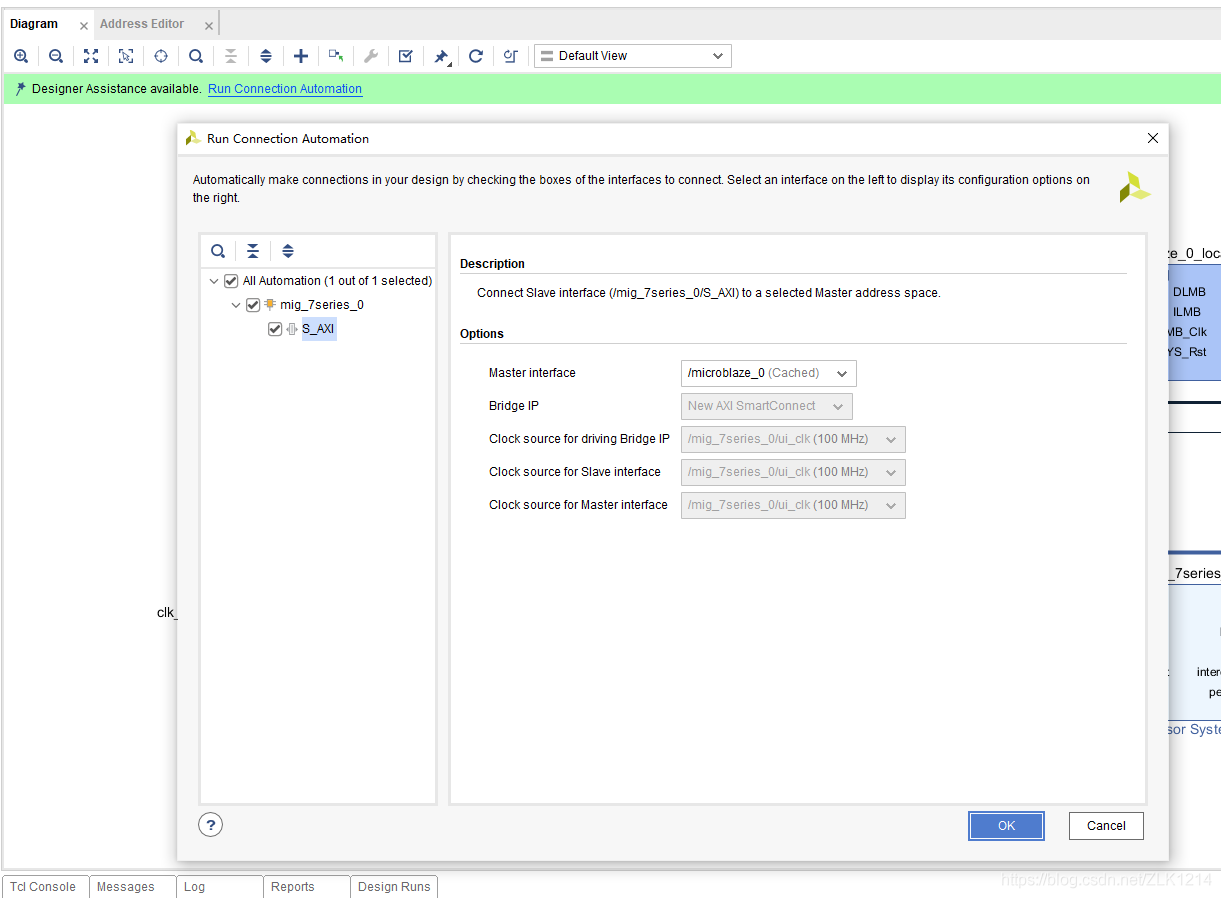

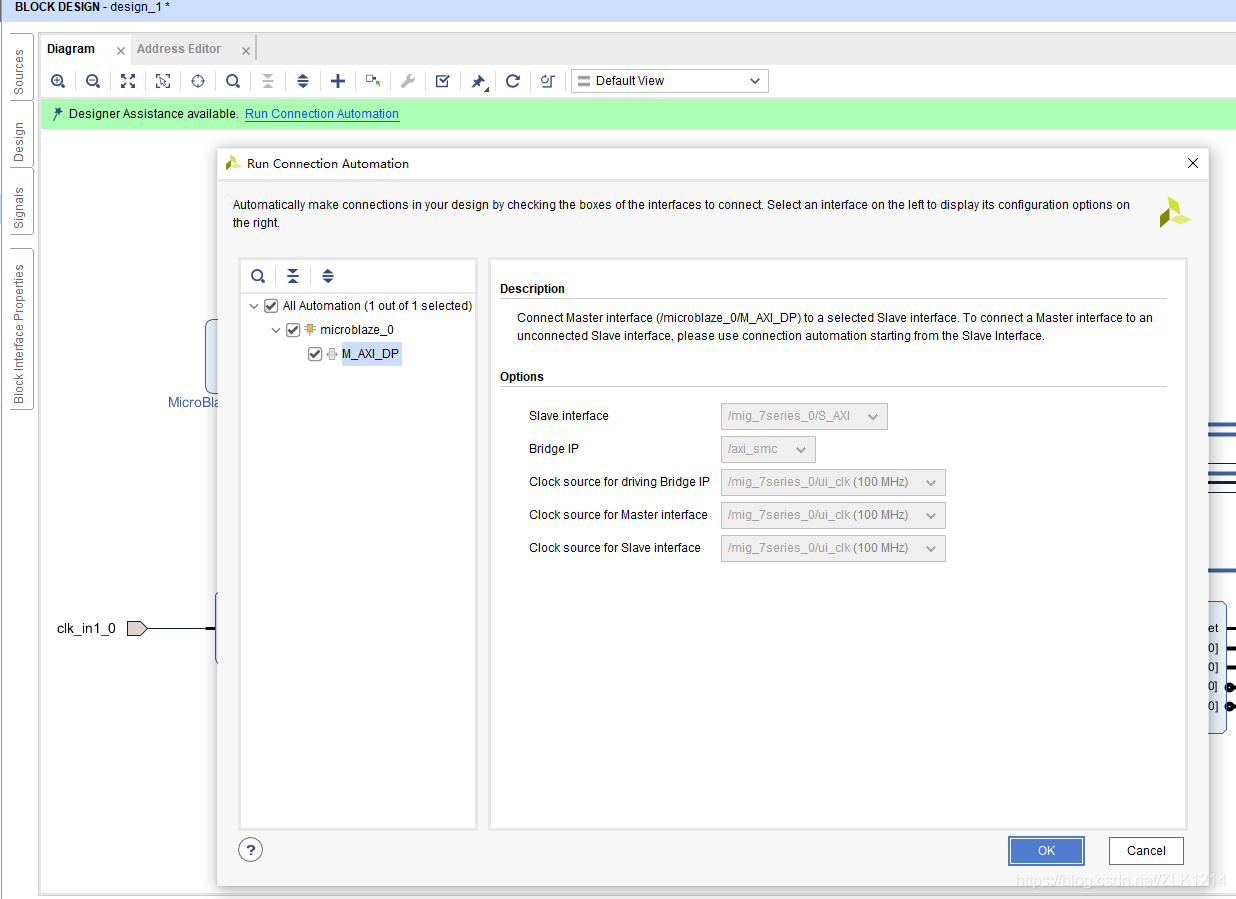

點(diǎn)擊Run Connection Automation,通過(guò)一個(gè)新建的AXI SmartConnect將MIG的S_AXI和MicroBlaze連接起來(lái):

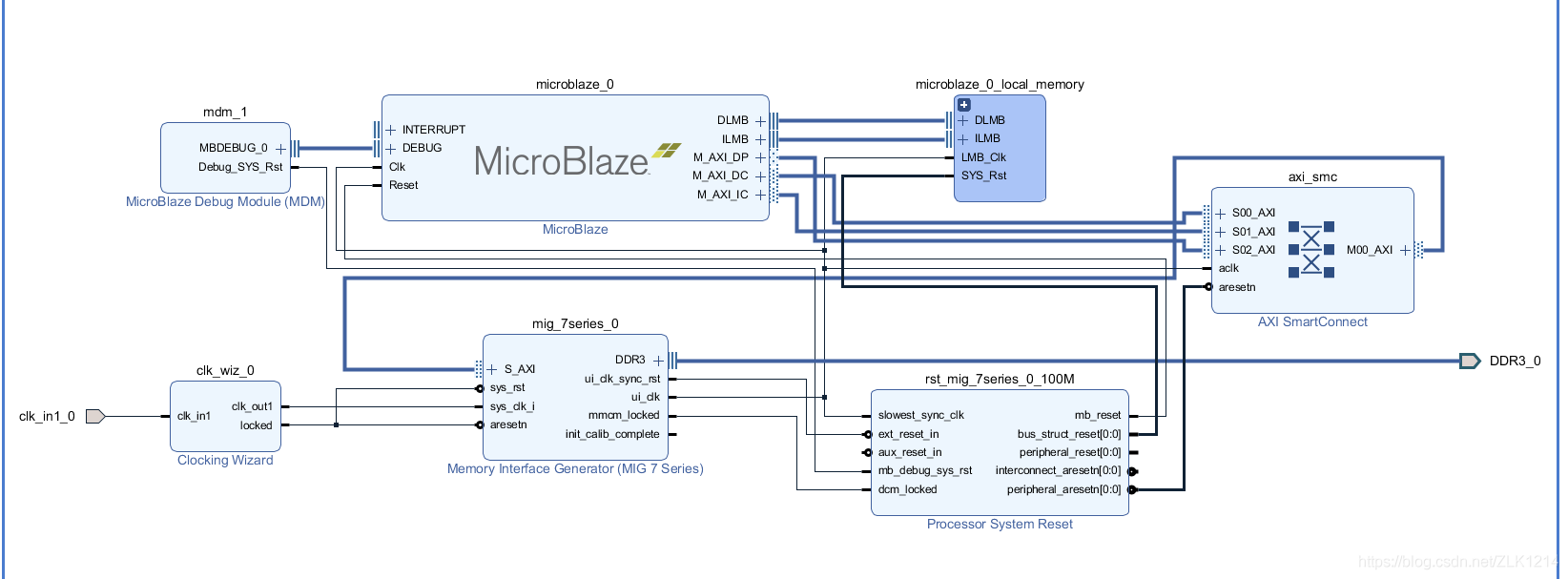

自動(dòng)連接剩余的接口:

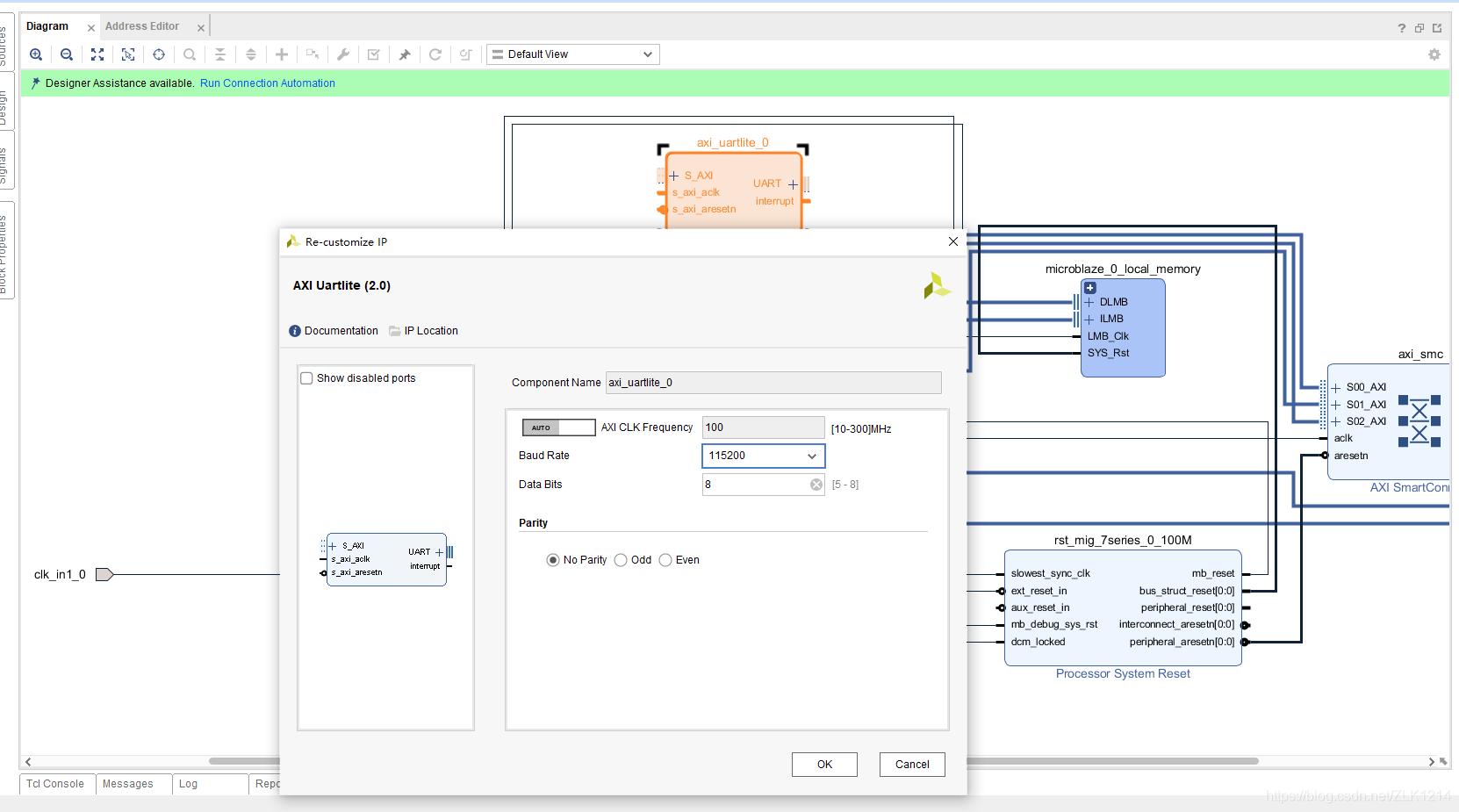

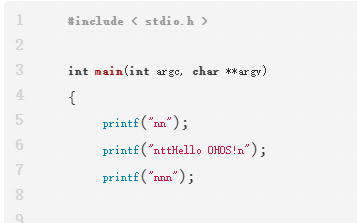

添加AXI Uartlite串口,用于printf打印:

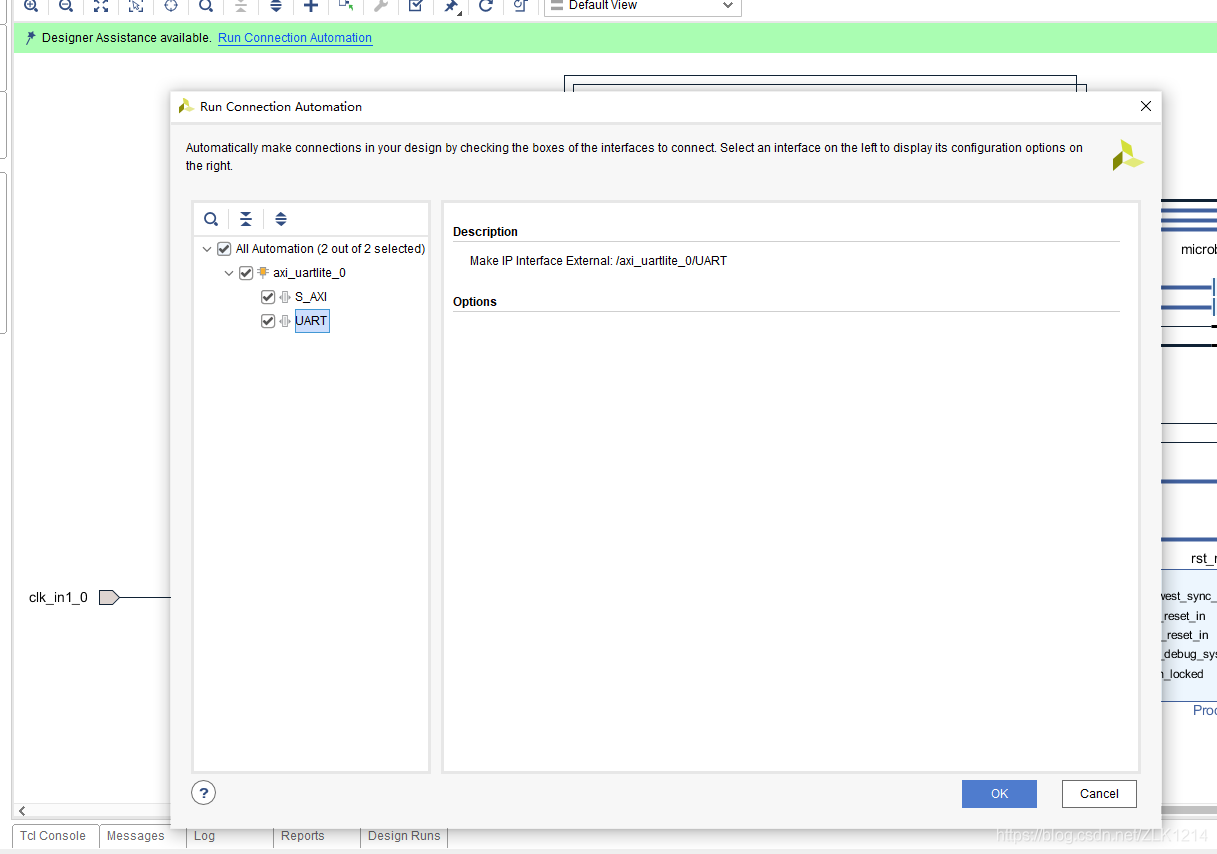

Run Connection Automation,將Uartlite與MicroBlaze連在一起:

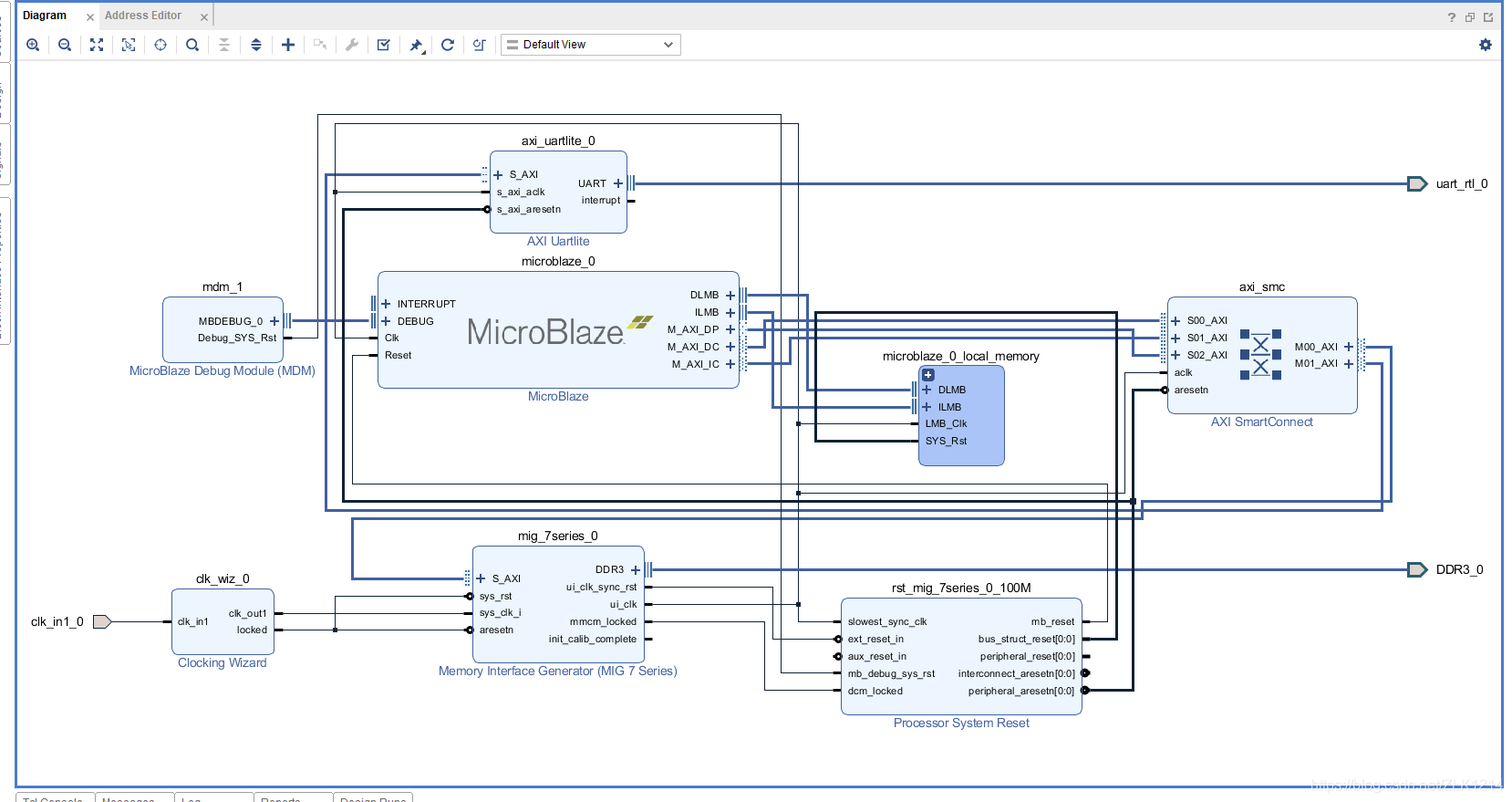

最終連線結(jié)果:

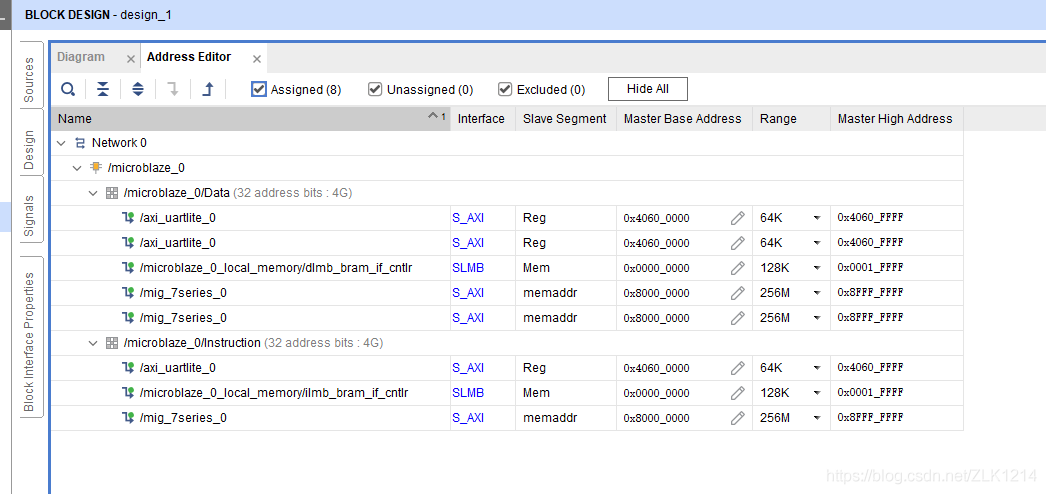

地址分配:

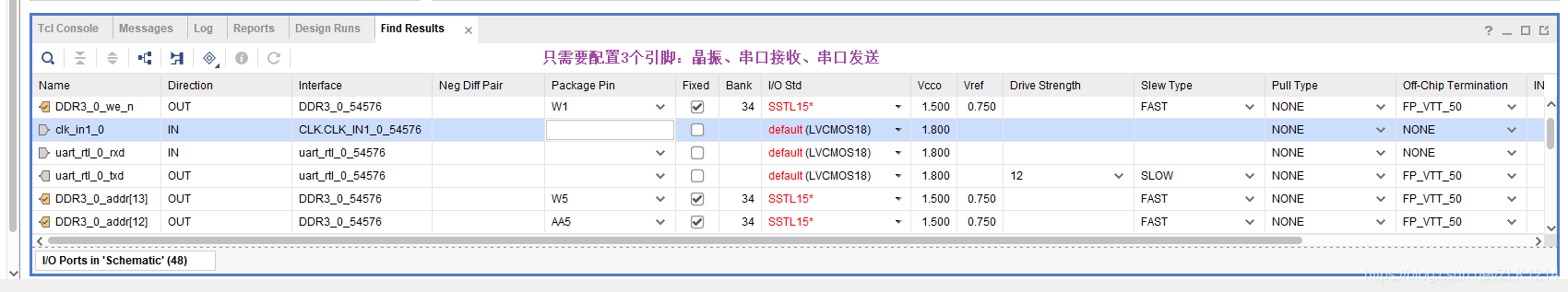

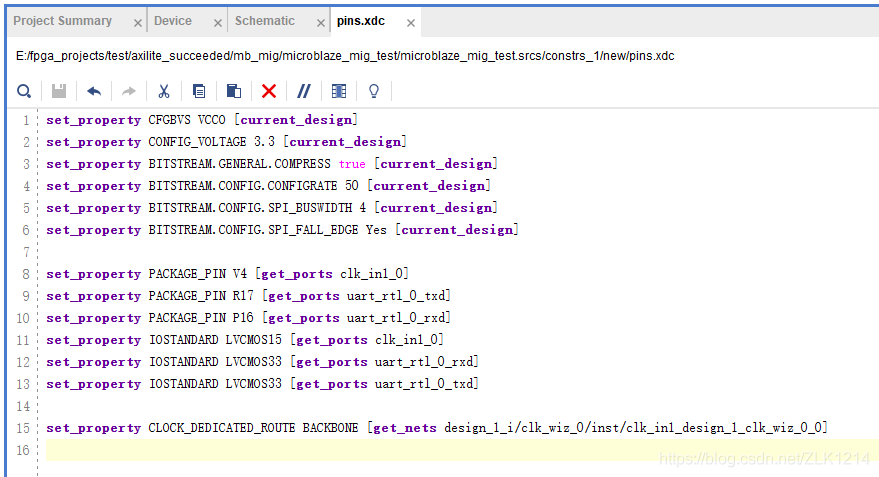

引腳配置:

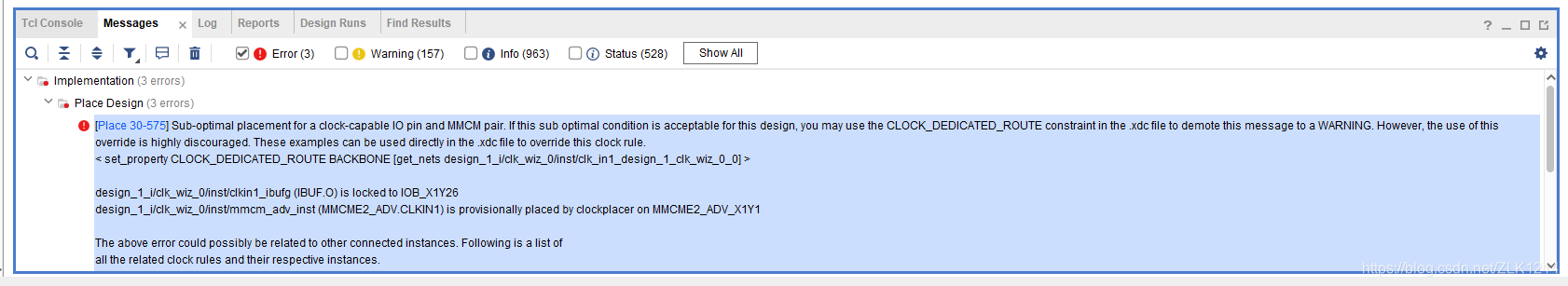

綜合時(shí)會(huì)提示BANKBONE錯(cuò)誤:

[Place 30-575] Sub-optimal placement for a clock-capable IO pin and MMCM pair. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

design_1_i/clk_wiz_0/inst/clkin1_ibufg (IBUF.O) is locked to IOB_X1Y26

design_1_i/clk_wiz_0/inst/mmcm_adv_inst (MMCME2_ADV.CLKIN1) is provisionally placed by clockplacer on MMCME2_ADV_X1Y1

The above error could possibly be related to other connected instances. Following is a list of

all the related clock rules and their respective instances.

Clock Rule: rule_mmcm_bufg

Status: PASS

Rule Description: An MMCM driving a BUFG must be placed on the same half side (top/bottom) of the device

design_1_i/clk_wiz_0/inst/mmcm_adv_inst (MMCME2_ADV.CLKFBOUT) is provisionally placed by clockplacer on MMCME2_ADV_X1Y1

and design_1_i/clk_wiz_0/inst/clkf_buf (BUFG.I) is provisionally placed by clockplacer on BUFGCTRL_X0Y31

將錯(cuò)誤信息中提示的代碼加入xdc文件就可以屏蔽掉此錯(cuò)誤:

審核編輯:符乾江

-

DDR3

+關(guān)注

關(guān)注

2文章

276瀏覽量

42256 -

MicroBlaze

+關(guān)注

關(guān)注

3文章

68瀏覽量

21553

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Xilinx_Vivado_SDK的安裝教程

C語(yǔ)言中的socket編程基礎(chǔ)

使用Vivado通過(guò)AXI Quad SPI實(shí)現(xiàn)XIP功能

如何在i2c中將hello world發(fā)送到LCD屏幕?

esp32運(yùn)行make flash燒寫(xiě)hello world遇到的疑問(wèn)求解

鴻蒙OpenHarmony【輕量系統(tǒng) 編寫(xiě)“Hello World”程序】 (基于Hi3861開(kāi)發(fā)板)

鴻蒙OpenHarmony【小型系統(tǒng) 編寫(xiě)“Hello World”程序】 (基于Hi3516開(kāi)發(fā)板)

鴻蒙OpenHarmony【標(biāo)準(zhǔn)系統(tǒng) 編寫(xiě)“Hello World”程序】(基于RK3568開(kāi)發(fā)板)

鴻蒙OpenHarmony【標(biāo)準(zhǔn)系統(tǒng)編寫(xiě)“Hello World”程序】 (基于RK3568開(kāi)發(fā)板)

鴻蒙OpenHarmony【小型系統(tǒng)編寫(xiě)“Hello World”程序】 (基于Hi3516開(kāi)發(fā)板)

鴻蒙OpenHarmony【輕量系統(tǒng)編寫(xiě)“Hello World”程序】 (基于Hi3861開(kāi)發(fā)板)

【從0開(kāi)始創(chuàng)建AWTK應(yīng)用程序】編譯應(yīng)用到RTOS平臺(tái)

全志D1s開(kāi)發(fā)板軟件入門之Hello World演示

用于EK-RA8D1 MIPI LCD顯示器的GUIX Hello World

Xilinx Vivado創(chuàng)建MicroBlaze工程運(yùn)行Hello World C語(yǔ)言程序

Xilinx Vivado創(chuàng)建MicroBlaze工程運(yùn)行Hello World C語(yǔ)言程序

評(píng)論