注:本文轉自賽靈思中文社區論壇,源文鏈接在此。本文原作者為XILINX工程師。

以下為個人譯文,僅供參考,如有疏漏之處,還請不吝賜教。

本篇博文是面向希望學習 Xilinx System Generator for DSP 入門知識的新手的系列博文第一講。

其中提供了有關執行下列操作的分步操作方法指南:

- 使用 Xilinx System Generator 塊集合對用戶算法進行建模

- 對設計進行仿真并以可視化方式直觀展示輸入/輸出以驗證設計

- 為設計生成測試激勵文件、測試矢量和 RTL (VHDL/Verilog) 代碼

Xilinx System Generator for DSP 可為基于模型的設計與系統集成平臺提供模塊框圖環境,以支持將 DSP 系統的 RTL、Simulink?、MATLAB? 和 C/C++ 組件整合到面向賽靈思 FPGA 器件的單一仿真和實現環境中。

它包含一個已預定義并預優化的開箱即用的塊集合,可用于對算法進行建模、仿真和分析,并生成測試激勵文件、測試矢量以及 HDL 代碼,從而加速 FPGA 開發。

System Generator 支持針對以下編譯目標生成自動代碼 (Automatic Code):

- HDL 網表

- IP 目錄

- 已綜合的檢查點

- 硬件協同仿真

配置 MATLAB

首先,我們需要安裝 MATLAB 并對 MATLAB 進行相應配置,確保它可配合 Vivado Design Suite 一起使用。

具體操作如下:

在 Windows 上:

以管理員身份打開“開始 >(所有)程序 > Xilinx Design Tools > Vivado 2019.x > System Generator > System Generator 2019.x MATLAB Configurator”。

出現 MATLAB 配置窗口后,勾選相應版本的 MATLAB 對應的復選框。

單擊“Apply”,然后單擊“OK”。

在 Linux 上:

請確保可在 Linux 系統的 $PATH 環境變量中找到 MATLAB 可執行文件。

Linux 下的 System Generator 是使用名為“sysgen”的 shell 腳本處理的,此腳本位于 /bin 目錄中。

本實踐教程操作步驟如下:

本篇博文是面向希望學習 Xilinx System Generator for DSP 入門知識的新手的系列博文第一講。

其中提供了有關執行下列操作的分步操作方法指南:

1. 使用 Xilinx System Generator 塊集合對用戶算法進行建模

2. 對設計進行仿真并以可視化方式直觀展示輸入/輸出以驗證設計

3. 為設計生成測試激勵文件、測試矢量和 RTL (VHDL/Verilog) 代碼

實踐教程將按以上指定的編譯目標順序予以展示。

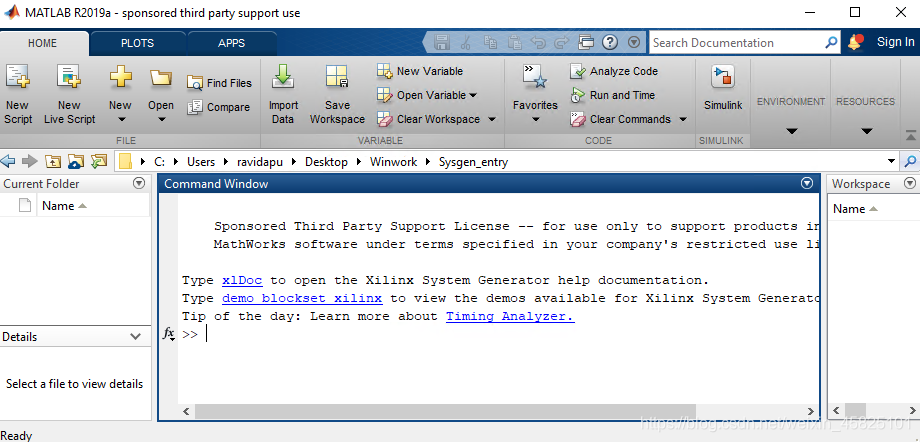

步驟 1:遵循以下對應于您的操作系統的步驟調用 System Generator:

- 在 Windows 系統上,選擇“開始 >(所有)程序 > Xilinx Design Tools > Vivado 2019.x >System Generator > System Generator 2019.x”

- 在 Linux 系統上的命令提示符處輸入 sysgen

此步驟將打開包含 System Generator 塊集合的 MATLAB 會話。

如以下截屏所示:

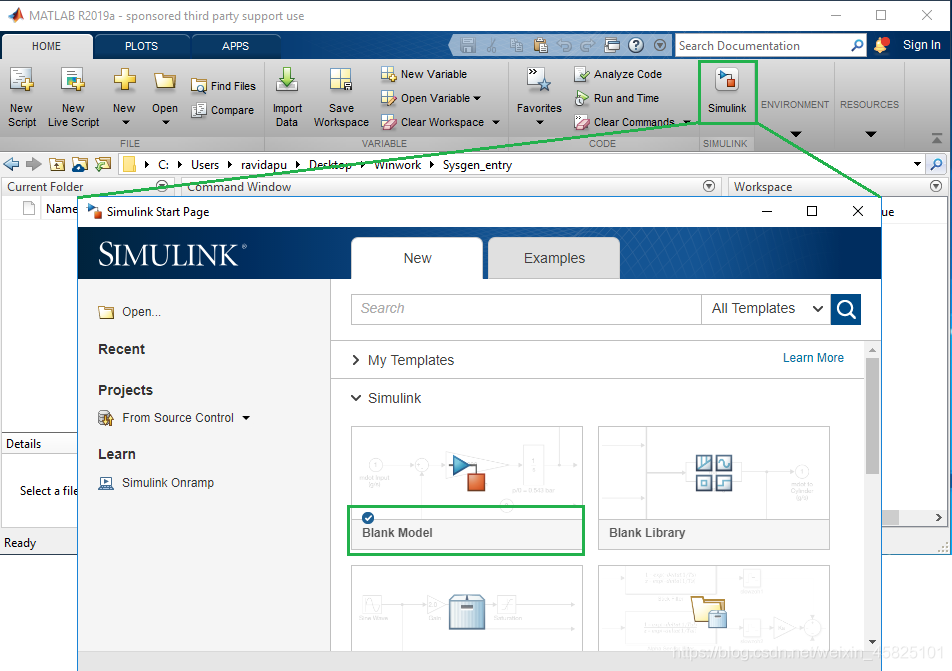

步驟 2:將工作目錄更改為包含創建的 Sysgen 模型的任意本地目錄。

單擊位于 MATLAB 窗口右上角的 Simulink 圖標。

這樣將打開 Simulink Start Page:

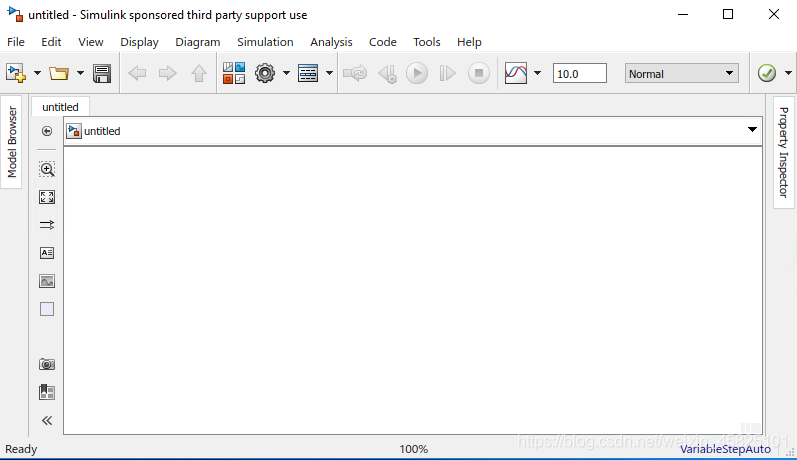

步驟 3:單擊 Simulink 下拉選項的“Blank model”圖標。

這樣將打開空白或“Untitled”模型,其中包含空白的模型畫布。

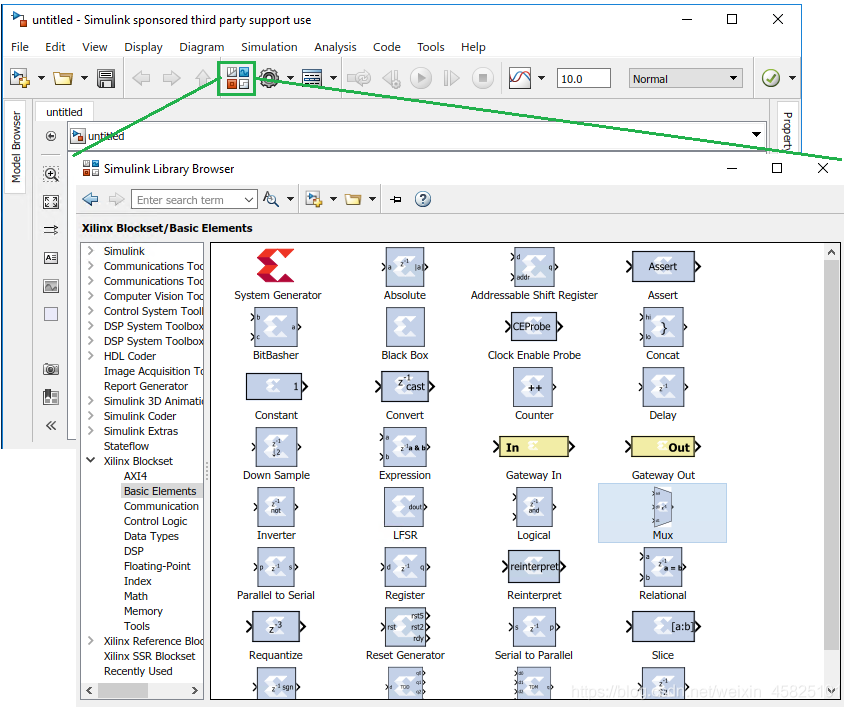

步驟 4:單擊“Untitled”模型窗口中的“Library browser”圖標以便在“Simulink Library Browser”窗口中查看賽靈思塊集合。

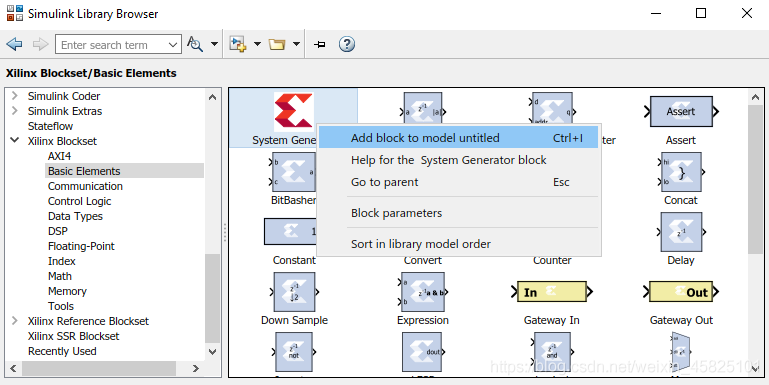

單擊并展開“Xilinx Blockset”菜單,以查看不同類別的塊。單擊“Basic elements”類別,以查看基本 sysgen 塊,如下所示:

步驟 5:右鍵單擊并選擇“Add block to model”(Ctrl+I) 選項將 System Generator 標識塊添加到模型中以定義 FPGA 技術。

以同樣方式添加“Gateway In”和“Gateway Out”塊,以定義設計的 System Generator 部分與 Simulink 部分之間的界限。

注:任何模型都必須包含這些必需的塊。每個模型都必須至少包含 1 個 System Generator 塊,可包含多個“Gateway In”和“Gateway Out”塊,具體取決于設計的輸入和輸出。

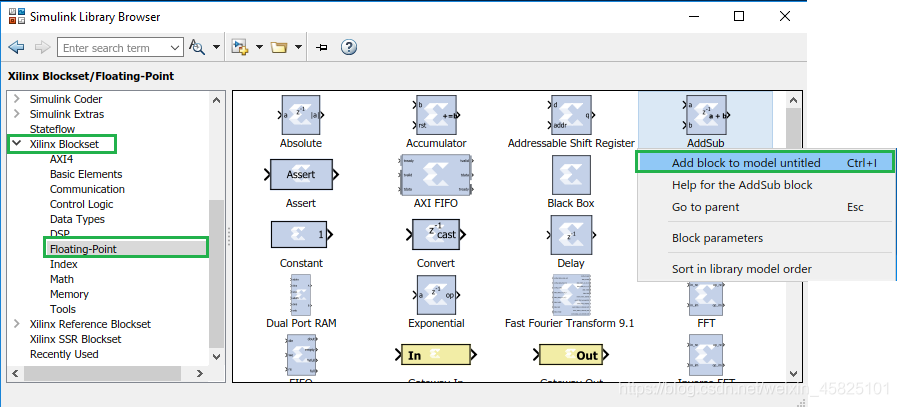

此處演示的是添加乘累加 (Mult-add) 運算的建模過程,因此我們需要將“Mult”、“AddSub”和“Delay”塊添加到模型中。

步驟 6:選中“Xilinx Blockset”下的“Floating-Point”類別中的“AddSub”塊,右鍵單擊,然后單擊“Add block to model”選項。

步驟 7:以同樣方式選中“Xilinx Blockset”下的“Floating-Point”類別中的“Mult”塊和“Basic Elements”類別下的“Delay”塊,并將這兩個塊添加到模型中。

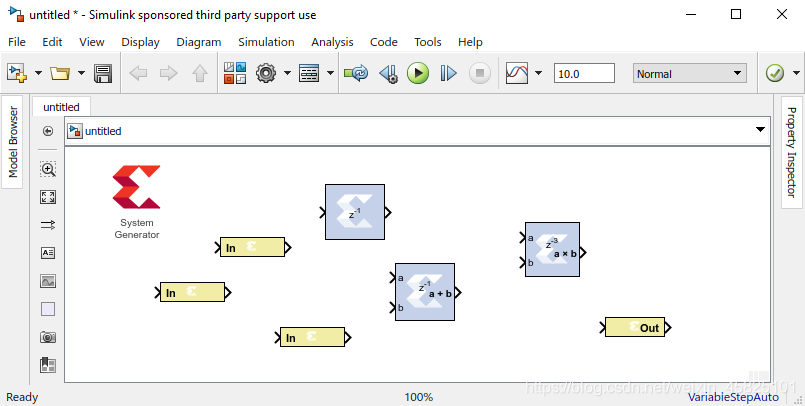

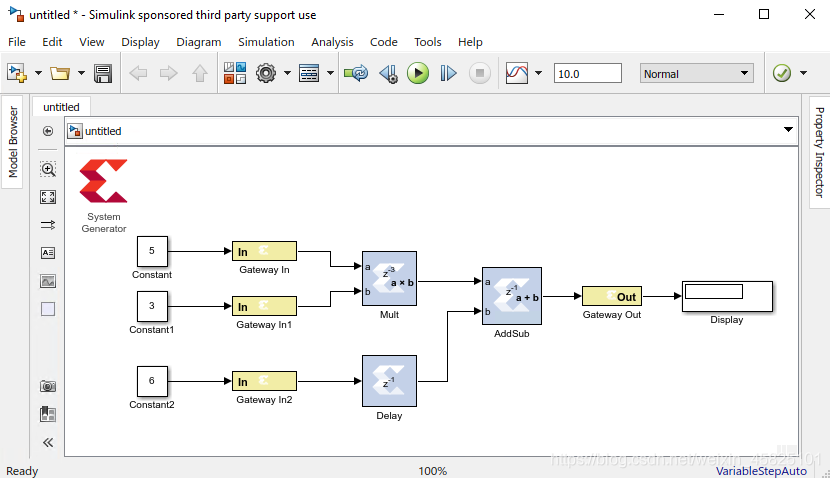

這樣模型將如下圖所示:

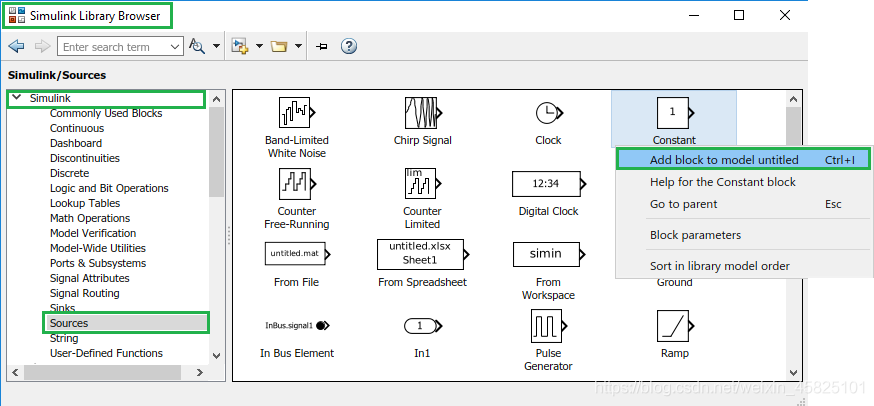

步驟 8:現在,添加 3 個“Constant”塊實例,此“Constant”塊可在“Simulink Library Browser”的“Simulink”塊集合下的“Sources”類別中找到:

以同樣方式添加來自“Simulink”塊集合下的“Sinks”類別的“Display”塊。

這些塊用作為 System Generator 設計的激勵塊。

步驟 9:按住鼠標左鍵并繪制一條從源端口到目標端口的線,以將塊連接在一起。

完整的模型將如下所示:

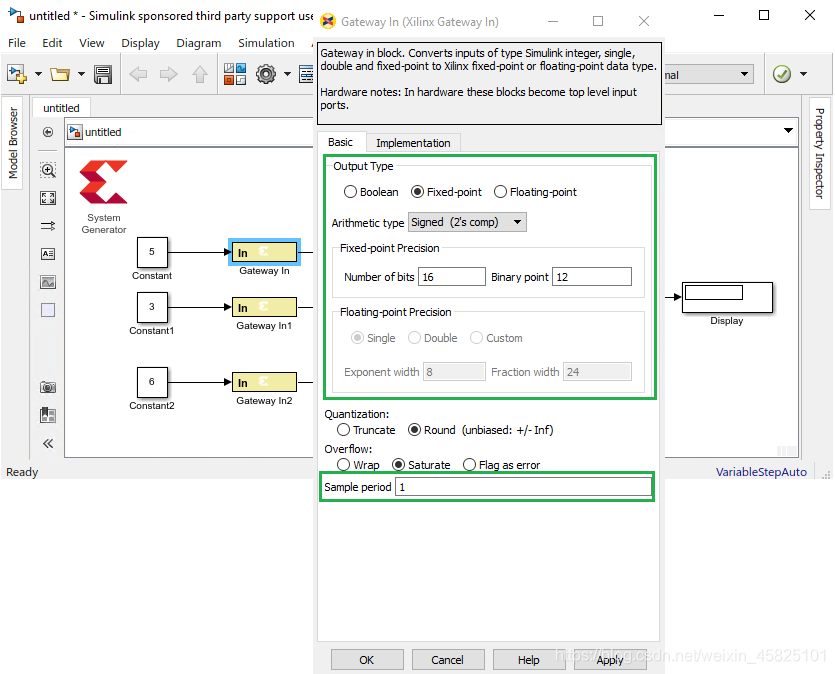

步驟 10:雙擊“Gateway In”塊以打開“Properties Editor”,根據塊 GUI 中的“Output type”和“Sample period”下的輸入值來設置輸入數據類型,然后單擊“OK”。

針對其他輸入重復該過程:

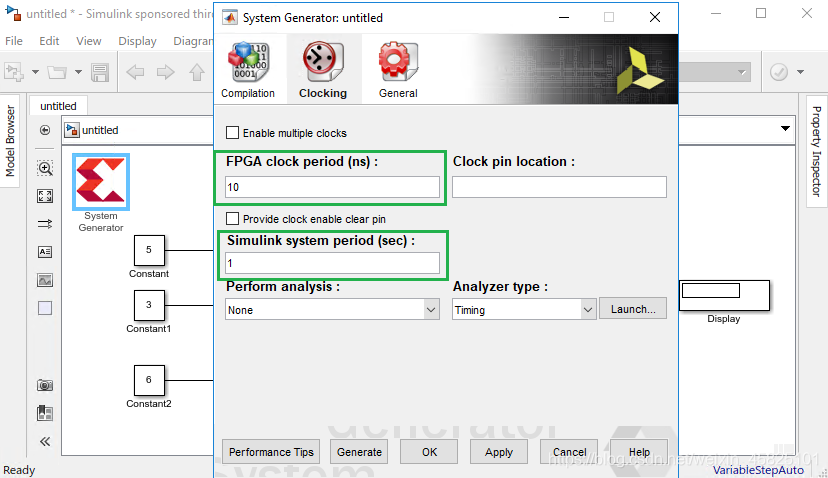

步驟 11:雙擊 System Generator 標識以更改系統和仿真參數。

確保“clocking”選項卡下的“Simulink system period”與“Gateway In”塊的樣本周期相同。

“FPGA clock period”應為“Simulink system period”的整數倍。

單擊“OK”。

步驟 12:單擊模型工具欄上的保存按鈕、為其提供有效的名稱,然后單擊“Save”以保存設計(在步驟 3-9 間可隨時執行此步驟)。

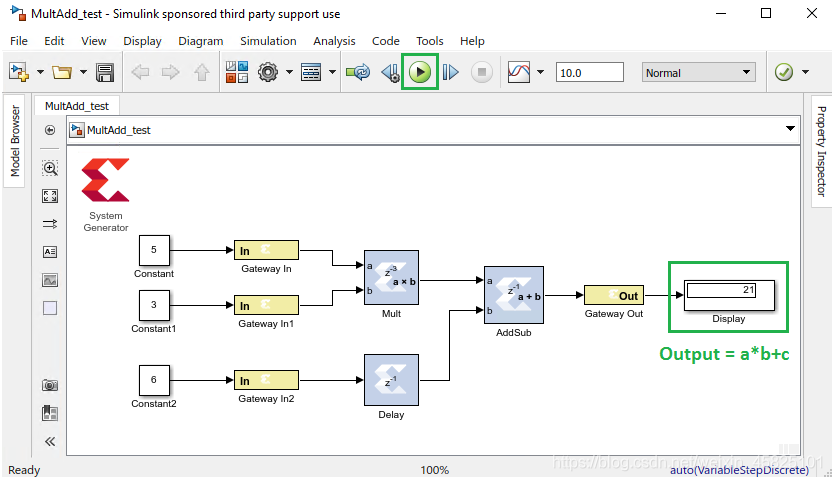

步驟 13:單擊“Run”按鈕以對模型進行仿真并驗證輸出:

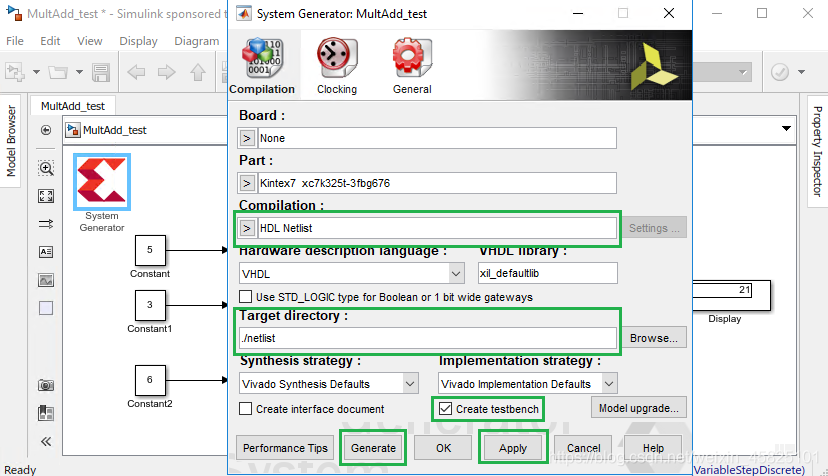

步驟 14:雙擊 System Generator 標識,確保:

- “Compilation”已設置為“HDL Netlist”

- “Target directory”選項設置為包含所生成 RTL 代碼的任意有效目錄(在此示例中目錄為 netlist)

- 已選中“Compilation”選項卡上的“Create testbench”選項

對于其他選項,保留默認設置。

現在,單擊“Apply”,然后單擊“Generate”按鈕。

注:System Generator 標識充當用于控制系統和仿真參數的控制面板,并且還可用于調用代碼生成器。

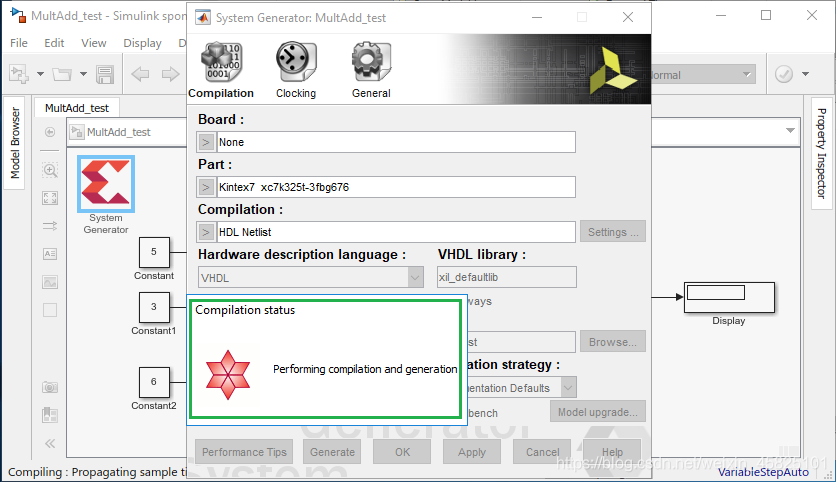

步驟 15:代碼生成過程開始后,就會彈出狀態窗口,如下所示:

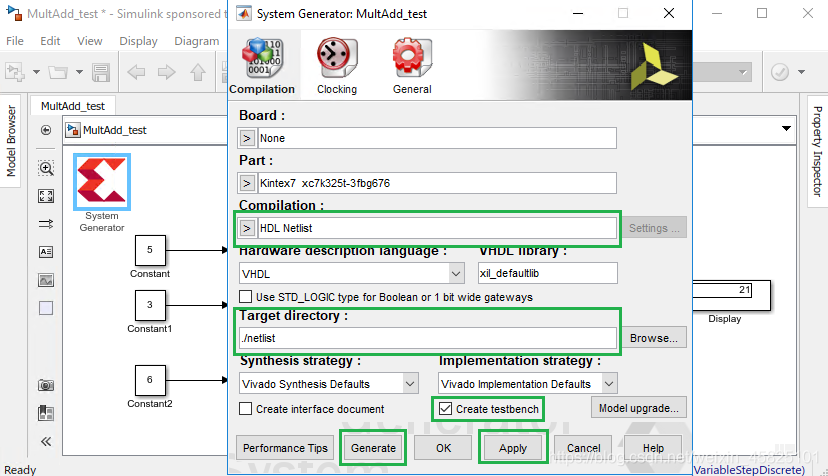

步驟 16:代碼生成完成后,狀態窗口將通知您代碼生成過程已完成。

在此處截屏中所示的示例中,System Generator 已成功生成 Kintex-7 xc7k325t-3fbg676 器件的 VHDL RTL 設計,包括測試矢量和測試激勵文件。

現在,請啟動 Vivado,打開“netlist/hdl_netlist/Multadd_test.xpr”文件,然后按下文中詳述的步驟運行 Vivado 流程:

Vivado 設計輸入紀事 - RTL 設計輸入

審核編輯:符乾江

-

dsp

+關注

關注

555文章

8142瀏覽量

355277 -

RTL

+關注

關注

1文章

388瀏覽量

60679

發布評論請先 登錄

Xilinx Shift RAM IP概述和主要功能

智多晶FIFO_Generator IP介紹

Vivado HLS設計流程

英諾達推出RTL功耗優化工具

SRIO介紹及xilinx的vivado 2017.4中生成srio例程代碼解釋

Xilinx_Vivado_SDK的安裝教程

FIFO Generator的Xilinx官方手冊

評論