摘要

嵌入式硅鍺在最近的技術節點中被應用于互補金屬氧化物半導體中,以提高器件性能并實現擴展。本文發現硅鍺表面相對于溝道的位置對功率因數校正閾值電壓和器件可變性有顯著影響。因此,嵌入式硅鍺的凹槽蝕刻和沉積必須得到很好的控制。我們展示了器件對填充工藝的敏感性,并描述了用于優化外延控制的前饋和反饋技術。

介紹

在進入制造業的最新CMOS技術節點,由于傳統的柵極長度和厚度縮放不再提供在較低漏極電壓(Vd)下較高飽和電流(Id,sat)所需的增益,因此越來越需要添加技術元素來提升器件性能。這里我們指的是諸如應力工程、激光退火、高k電介質和金屬柵極等技術。在本文中,我們討論了嵌入式硅鍺(eSiGe)的應用,它是應力工程的一種形式,也是提高pFET器件性能的一種非常有效的方法。我們表明,應該很好地控制凹槽反應離子蝕刻(RIE)和外延層厚度,以避免pFET閾值電壓(Vth)可變性的顯著增加。

技術描述

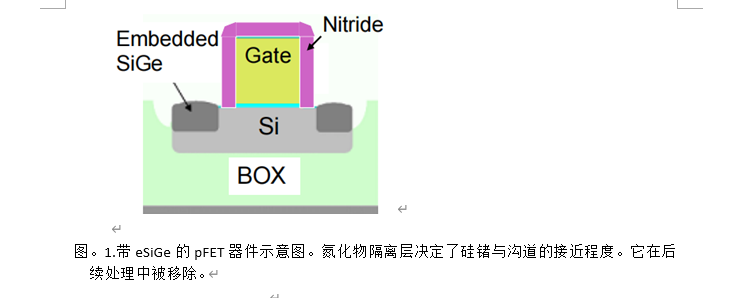

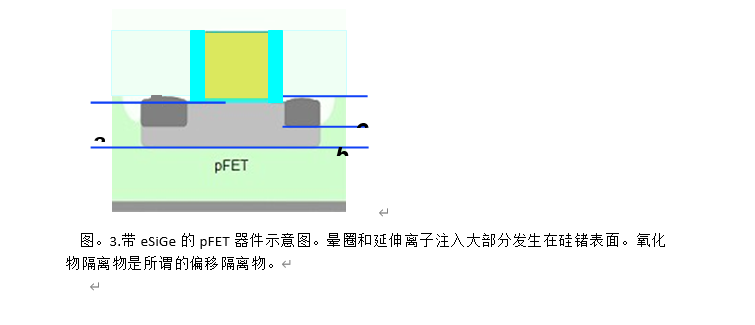

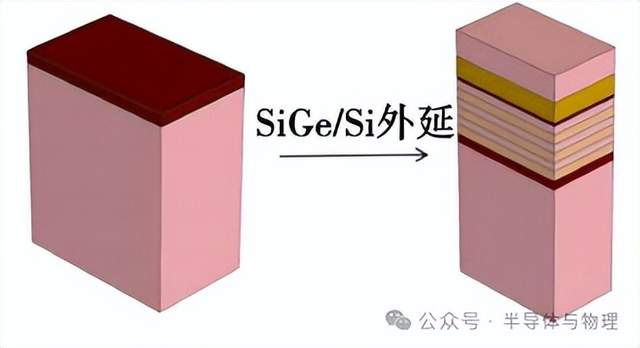

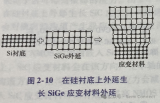

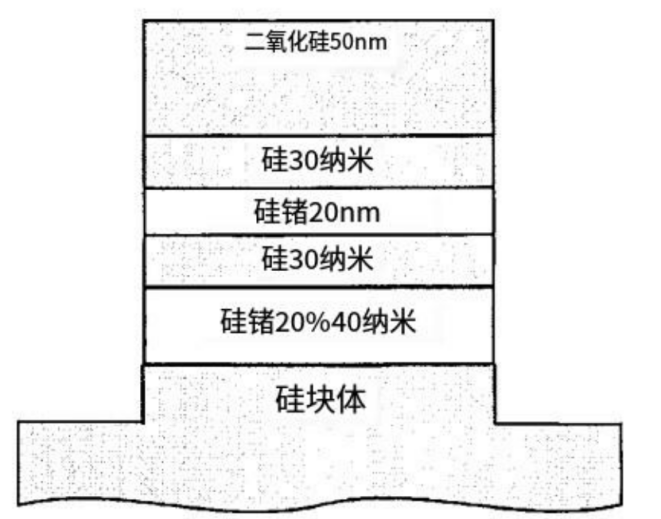

在SOI技術中,活性硅位于所謂的掩埋氧化層上,而氧化層又位于硅片上。在定義柵極之后沉積硅鍺。首先,用氮化物層覆蓋表面,該氮化物層在pFET器件的源極/漏極區上方開口。隨后,我們將開口區域中的硅蝕刻到指定的深度,然后選擇性地沉積硅鍺。我們使用使用硅烷的傳統技術,其中硅鍺不在氮化物上生長。氮化物還充當限定硅鍺接近溝道的隔離物。 在硅鍺外延之后,氮化物被選擇性地去除,并且處理按照常規繼續,在本例中,這意味著柵極-側壁間隔物以及n和p暈圈和延伸注入的序列。在SiGe沉積之后,但是在去除氮化物隔離物之前,器件的橫截面顯示在圖1中。

設備靈敏度

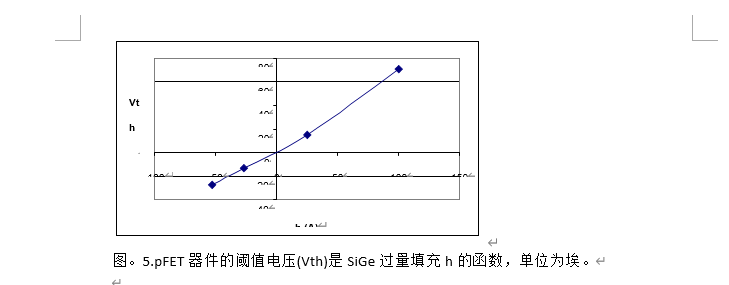

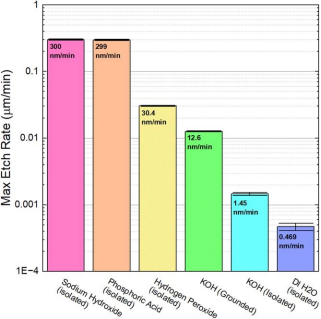

圖4顯示了在確定硅鍺表面相對于溝道的位置時要考慮的尺寸。過量填充h是硅鍺表面的高度和溝道的高度之差。當我們談論過滿h時,我們通常指的是在線計量所用寬墊片上測量的高度。器件靈敏度如圖2所示。5.此處顯示的數據來自分割批次,其中通過改變沉積時間,硅鍺沉積厚度在15納米范圍內變化。正如預期的那樣,閾值電壓隨著硅鍺高度的增加而增加,在我們的情況下約為每納米6 mV。

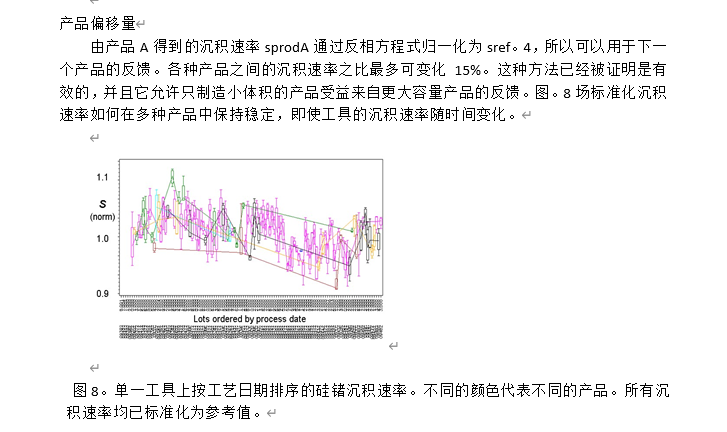

如上所述,這種先進過程控制(APC)方法,通過其反饋和前饋的結合,將改善填充控制。如果我們比較兩種技術,使用相同的工具進行RIE和外延,其中一種使用傳統的工具控制,沒有運行到運行的反饋其次,使用上述方法,我們發現一個顯著的差異。與常規控制工藝相比,使用反饋,沉積層的標準偏差降低了30%。

結論

本文發現功率場效應晶體管的閾值電壓強烈依賴于嵌入硅鍺的沉積厚度。這既是因為硅鍺接近溝道,也是因為它對離子注入的影響。為了最小化器件可變性,我們采用前饋和反饋技術,使硅鍺表面與輸入SOI厚度緊密匹配。所用的APC技術應用于多種產品,通過包含沉積速率之間的已知比率來說明差異。

審核編輯:湯梓紅

-

CMOS

+關注

關注

58文章

5722瀏覽量

235614 -

電流

+關注

關注

40文章

6880瀏覽量

132277 -

半導體

+關注

關注

334文章

27432瀏覽量

219298

發布評論請先 登錄

相關推薦

芯片濕法蝕刻工藝

SiGe與Si選擇性刻蝕技術

選擇性沉積技術介紹

一文詳解半導體薄膜沉積工藝

濕法蝕刻的發展

源漏嵌入SiGe應變技術簡介

基于光譜共焦技術的PCB蝕刻檢測

通信——通過表面電荷操縱控制鍺的蝕刻

關于兩種蝕刻方式介紹

流量控制器在半導體加工工藝化學氣相沉積(CVD)的應用

影響pcb蝕刻性能的五大因素有哪些?

鍺化硅(SiGe)和硅(Si)之間的各向同性和選擇性蝕刻機制

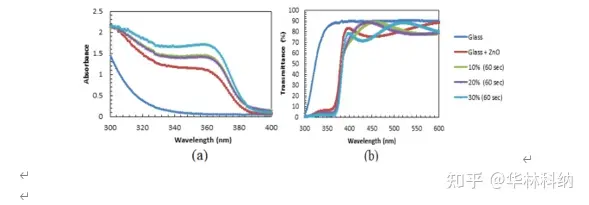

半導體資料丨氧化鋅、晶體硅/鈣鈦礦、表面化學蝕刻的 MOCVD GaN

詳解SiGe的蝕刻和沉積控制

詳解SiGe的蝕刻和沉積控制

評論