沒有任何寄存器邏輯,RTL設計是不完整的。RTL是寄存器傳輸級或邏輯,用于描述依賴于當前輸入和過去輸出的數(shù)字邏輯。

在異步計數(shù)器中,時鐘信號不由公共時鐘源驅(qū)動。如果LSB觸發(fā)器的輸出作為后續(xù)觸發(fā)器的輸入,則設計是異步的。異步設計的主要問題是由于級聯(lián),觸發(fā)器的累積時鐘到q延遲。由于存在小故障或尖峰問題,ASIC/FPGA設計中不建議使用異步計數(shù)器,甚至此類設計的時序分析也非常復雜。

所以接下來只介紹一種計數(shù)器

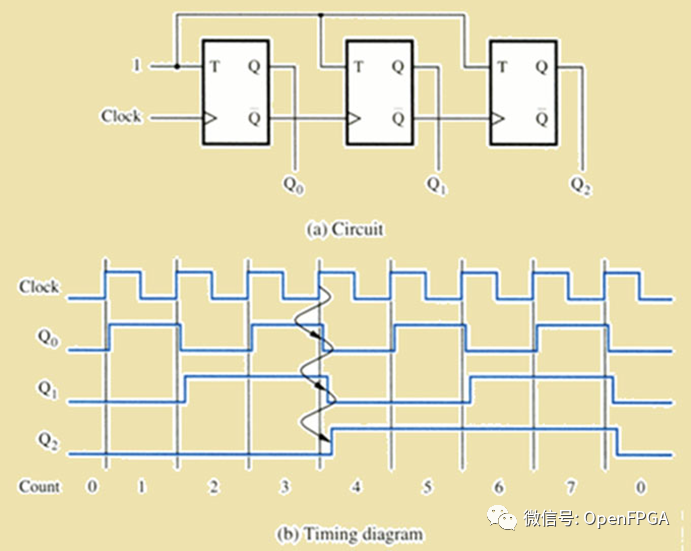

紋波計數(shù)器是一個異步計數(shù)器,如圖5.33所示。如邏輯圖所示,所有觸發(fā)器均為正邊緣觸發(fā),LSB寄存器從主時鐘源接收時鐘。LSB觸發(fā)器的輸出作為下一級的時鐘輸入。

圖5.33三位紋波計數(shù)器邏輯圖

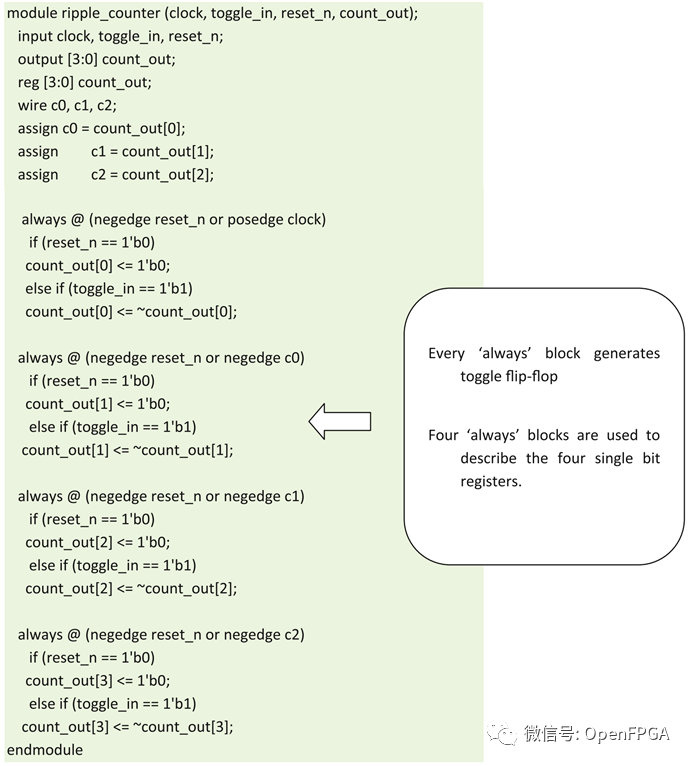

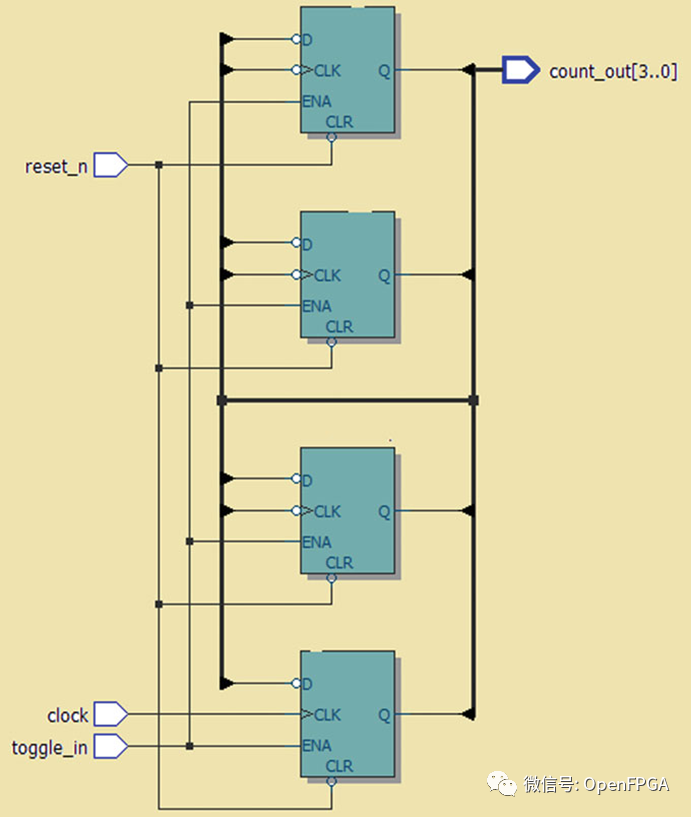

四位紋波遞增計數(shù)器的Verilog RTL如例5.18所示。綜合邏輯如圖5.34所示。

示例5.18四位紋波遞增計數(shù)器的Verilog RTL

圖5.34四位紋波遞增計數(shù)器的綜合邏輯

內(nèi)存模塊設計

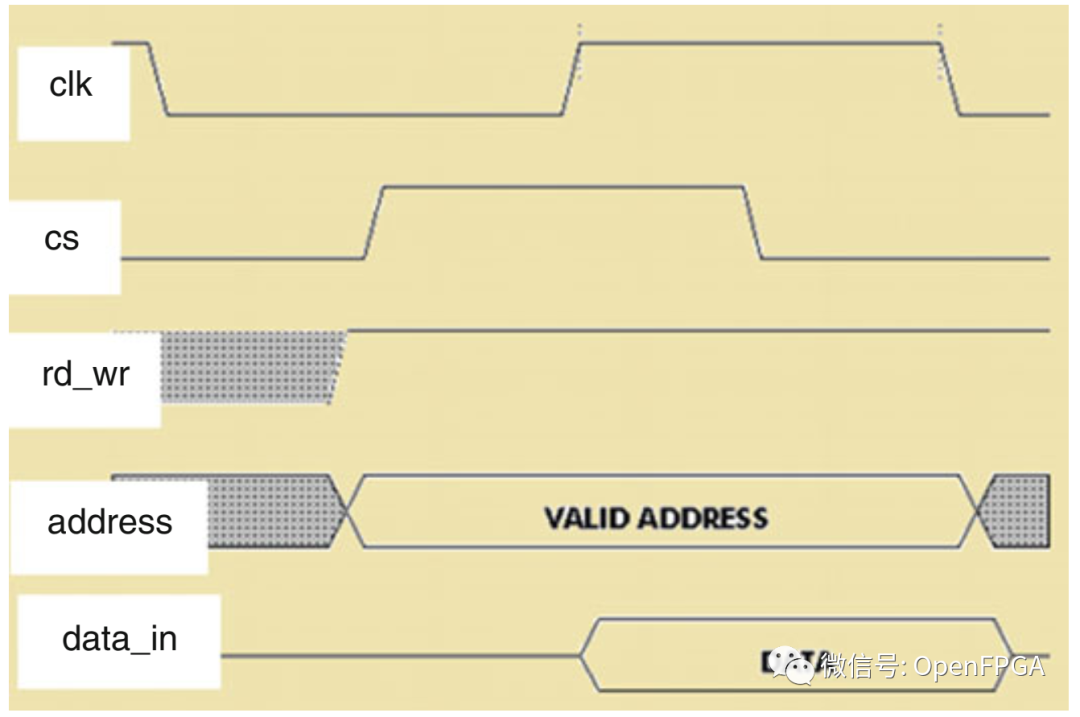

在大多數(shù)ASIC/FPGA設計和基于SoC的設計中,存儲器用于存儲二進制數(shù)據(jù)。存儲器可以是ROM、RAM、單端口或雙端口類型。本節(jié)的目的是描述基本的單端口讀寫存儲器。時序如圖5.35所示。

如時序所示,讀寫操作由“rd_wr”控制,如果“cs”為高電平,則在時鐘信號“clk”的正邊緣對數(shù)據(jù)進行采樣。地址輸入由總線“address”描述。

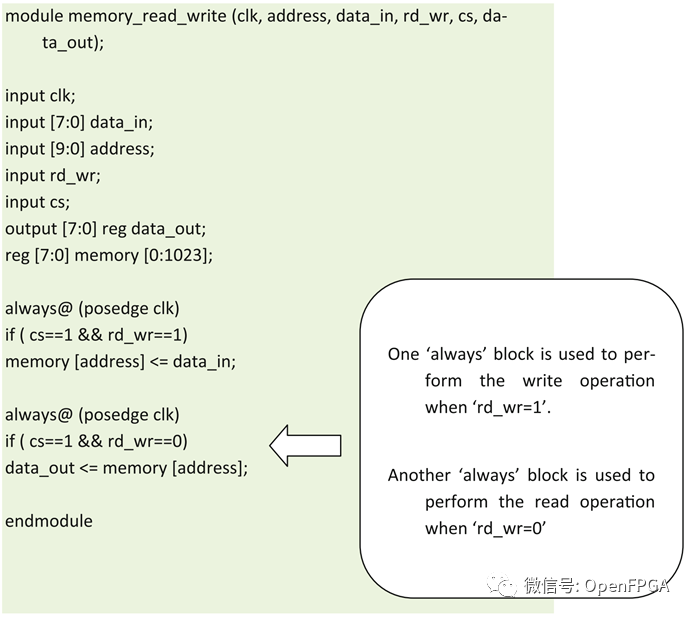

單端口讀寫存儲器的Verilog RTL如例5.19所示。

圖5.35存儲器的時序

示例5.19讀寫存儲器的Verilog RTL

審核編輯:‘’

-

寄存器

+關注

關注

31文章

5355瀏覽量

120513 -

計數(shù)器

+關注

關注

32文章

2256瀏覽量

94635 -

觸發(fā)器

+關注

關注

14文章

2000瀏覽量

61185

原文標題:Verilog時序邏輯硬件建模設計(五)異步計數(shù)器&總結(jié)

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

什么是時序分析?教你掌握FPGA時序約束

FPGA設計中的時序分析及異步設計注意事項

verilog描述異步置0,異步置1功能的D觸發(fā)器

Cadence高速PCB的時序分析

異步時序邏輯電路

ASIC中的異步時序設計

Verilog HDL語言實現(xiàn)時序邏輯電路

如何使用Verilog-HDL做CPLD設計的時序邏輯電路的實現(xiàn)

FPGA之何為異步時序

靜態(tài)時序分析:如何編寫有效地時序約束(一)

什么是同步時序電路和異步時序電路,同步和異步電路的區(qū)別?

異步設計之Verilog時序分析

異步設計之Verilog時序分析

評論