一、概述

在大規模ASIC或FPGA設計中,多時鐘系統往往是不可避免的,這樣就產生了不同時鐘域數據傳輸的問題,其中一個比較好的解決方案就是使用異步FIFO來作不同時鐘域數據傳輸的緩沖區,這樣既可以使相異時鐘域數據傳輸的時序要求變得寬松,也提高了它們之間的傳輸效率。此文內容就是闡述異步FIFO的設計。

二、設計原理

2.1結構框圖

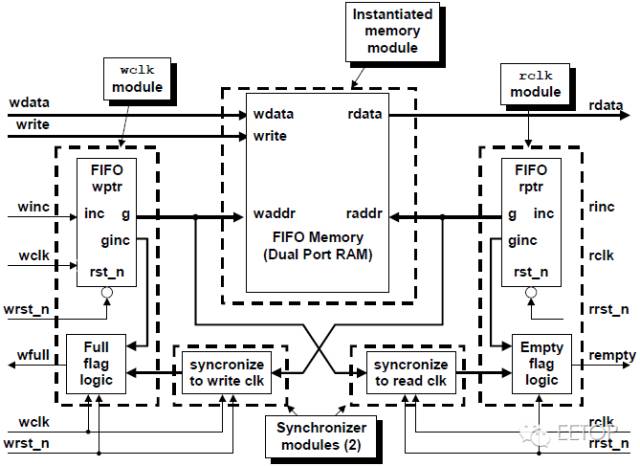

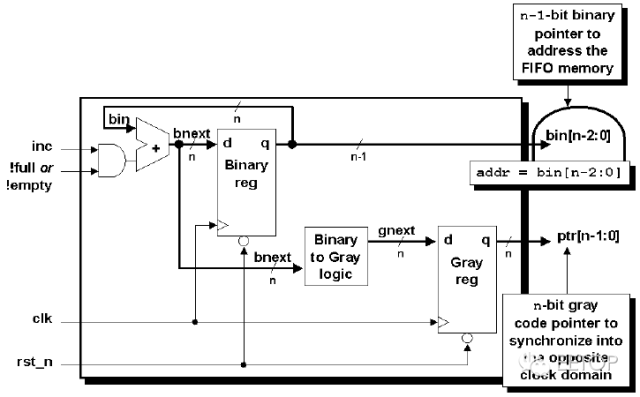

Fig. 2.1.1

如上圖所示的同步模塊synchronize to write clk,其作用是把讀時鐘域的讀指針rd_ptr采集到寫時鐘(wr_clk)域,然后和寫指針wr_ptr進行比較從而產生或撤消寫滿標志位wr_full;類似地,同步模塊synchronize to read clk的作用是把寫時鐘域的寫指針wr_ptr采集到讀時鐘域,然后和讀指針rd_ptr進行比較從而產生或撤消讀空標志位rd_empty。

另外還有寫指針wr_ptr和寫滿標志位wr_full產生模塊,讀指針rd_ptr和讀空標志位rd_empty產生模塊,以及雙端口存儲RAM模塊。

2.2二進制計數器存在的問題

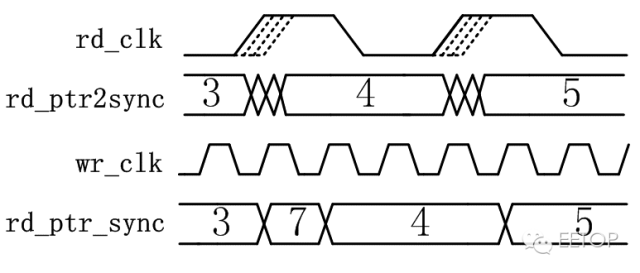

異步FIFO讀寫指針需要在數學上的操作和比較才能產生準確的空滿標志位,但由于讀寫指針屬于不同的時鐘域及讀寫時鐘相位關系的不確定性,同步模塊采集另一時鐘域的指針時,此指針有可能正處在跳變的過程中,如圖Fig.2.2.1所示,那么采集到的值很有可能是不期望的值,當然,不期望的錯誤結果也會隨之發生。

Fig. 2.2.1

上圖中,rd_ptr2sync 3和4以及4和5之間的中間態是由于到各寄存器的時鐘rd_clk存在偏差而引起的。二進制的遞增操作,在大多數情況下都會有兩位或者兩以上的bit位在同一個遞增操作內發生變化,但由于實際電路中會存在時鐘偏差和不同的路徑延時,二進制計數器在自增時會不可避免地產生錯誤的中間結果,如圖Fig.2.2.2。

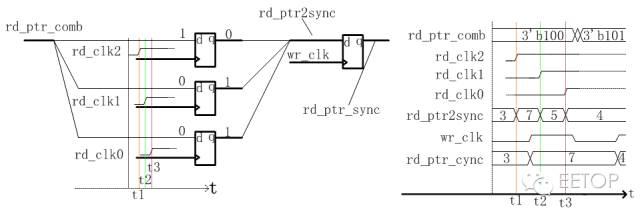

Fig.2.2.2

上圖是Fig.2.2.1的電路原型以及局部波形的放大。由于rd_clk上升沿到達三寄存器的時間各不相同,這就導致了rd_ptr2sync的值從3’b011跳變3’b100的過程中經歷了3’b111和3’b101,直到最后一個時鐘(rd_clk0)沿的到來后rd_ptr2sync才跳變到正確結果3’b100。中間結果的持續的時間雖然相對短暫,但是這些不正確的中間結果完全有可能被其它時鐘域的同步模塊采集到而產生錯誤的動作,見上圖。

由此可見,要避免中間結果的產生,其中一個可行的方案就是使被同步模塊采集的數據遞變時,每次只有一個bit位發生改變。格雷碼計數器就是一個不錯的選擇。

2.3格雷碼計數器的實現

2.3.1格雷碼的表現形式

格雷碼一個最大的特點就是在遞增或遞減的過程中,每次只變化一位,這是它最大的優點。同時它也有自己的局限性,那就是循環計數深度必須是2的n次冪,否則就失去了每次只變化一位的特性。深度為16的二進制及格雷碼遞變表如下:

Binary Gray

0 0000 0000

1 0001 0001

2 0010 0011

3 0011 0010

4 0100 0110

5 0101 0111

6 0110 0101

7 0111 0100

8 1000 1100

9 1001 1101

10 1010 1111

11 1011 1110

12 1100 1010

13 1101 1011

14 1110 1001

15 1111 1000

0 0000 0000

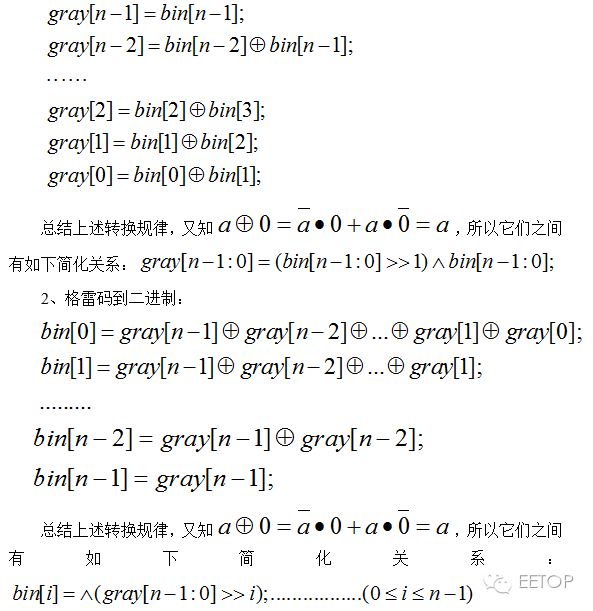

2.3.2二進制和格雷碼的相互轉換

1、二進制到格雷碼:

2.3.3格雷碼計數器的實現

如下圖fig.2.3.1所示,指向存儲器的地址指針由二進制計數器產生,而用于跨時鐘域傳播的格雷碼指針是對二進制指針的實時轉換并用寄存器采集獲得的。這里要注意的是,計數器的位寬比實際所需的位寬要多出一位,這樣做的目的是方便判斷FIFO的空或滿,這一點下文中將會介紹。

Fig.2.3.1格雷碼計數器結構圖

2.4空滿標志位的產生

異步FIFO最核心的部分就是精確產生空滿標志位,這直接關系到設計的成敗。本文采用比較讀寫指針來判斷FIFO的空滿,如果FIFO的深度是n-1位線所能訪問到的地址空間,那么此設計所要用的指針位寬就比實際多出一位,也就是n位,這樣做有助于判斷FIFO是空還是滿。

2.4.1讀空標志位的產生

當讀地址rd_ptr趕上寫地址wr_ptr,也就是rd_ptr完全等于wr_ptr時,可以斷定,FIFO里的數據已被讀空,而且只有在兩種情況下,FIFO才會為空:第一種是系統復位,讀寫指針全部清零;另一種情況是在FIFO不為空時,數據讀出的速率快于數據寫入的速率,讀地址趕上寫地址時FIFO為空。空標志位的產生需要在讀時鐘域里完成,這樣不至于發生FIFO已經為空了而空標志位還沒有產生的情況,但是可能會發生FIFO里已經有數據了而空標志位還沒有撤消的情況,不過就算是在最壞情況下,空標志位撤消的滯后也只有三個時鐘周期,這個問題不會引起傳輸錯誤;還有一種情況就是空標志比較邏輯檢測到讀地址和寫地址相同后緊接著系統產生了寫操作,寫地址增加,FIFO內有了新數據,由于同步模塊的滯后性,用于比較的寫地址不能及時更新,這樣,一個本不應該有的空標志信號就產生了,不過這種情況也不會導致錯誤的發生,像這種FIFO非空而產生空標志信號的情況稱為“虛空”。

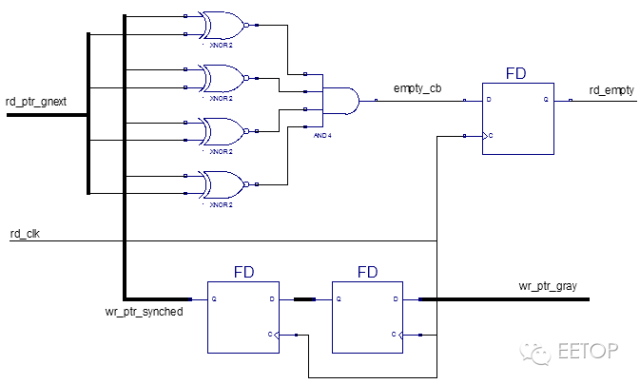

Fig. 2.4.1.1空標志產生邏輯

如圖Fig. 2.4.1.1空標志產生邏輯,寫時鐘域的寫指針通過兩級寄存被同步到讀時鐘域之后與讀指針進行比較,如果完全相等,則會產生空標志信號;同步模塊用兩級寄存器來實現是為了消除可能的亞穩態,正如前面所述,因為wr_ptr_gray是用格雷碼實現的,即使同步模塊是在wr_ptr_gray跳變的時刻進行采集,其采集到的所有可能值也只有兩個,一個是跳變之前的值,一個是跳變之后的值,它們只相差1,最壞情況也只是產生了“虛空”信號,而這不會引起錯誤傳輸。

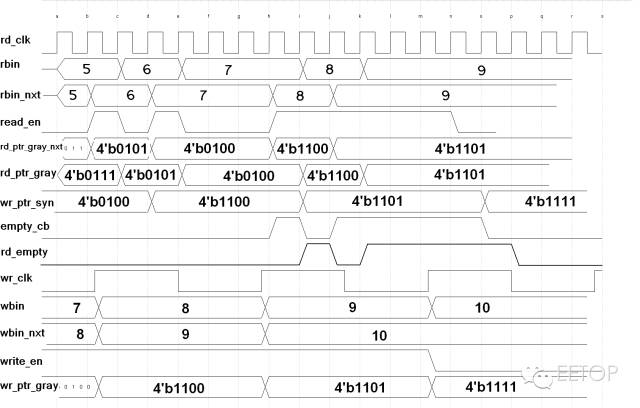

Fig. 2.4.1.2空標志產生時序

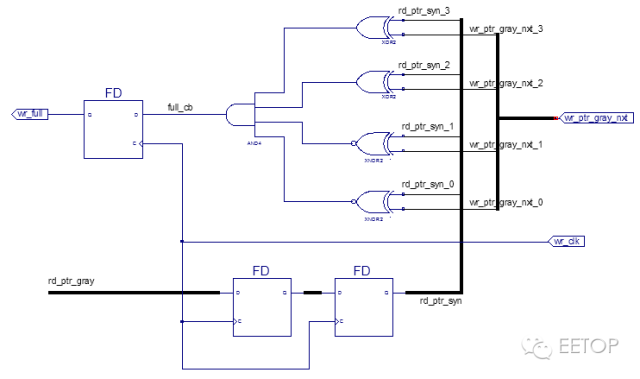

2.4.2寫滿標志位的產生

和讀空標志位產生機制一樣,寫滿標志位也是通過比較讀寫地址產生的。讀寫指針的關系就好比A,B兩個田徑運動員在一環形跑道上賽跑一樣,當B運動員領先A并整整超前一圈時,A,B兩人的地點相同,此種情況對應于讀寫指針指向了同一地址,但寫指針超前整整一圈,FIFO被寫滿。和讀空標志產生一樣,寫滿標志也是讀寫指針相同時產生。但是如果地址的寬度和FIFO實際深度所需的寬度相等,某一時刻讀寫地址相同了,那FIFO是空還是滿就難以判斷了。所以讀寫指針需要增加一位來標記寫地址是否超前讀地址(在系統正確工作的前提下,讀地址不可能超前于寫地址),比如FIFO的深度為8,我們需要用寬度為4的指針。

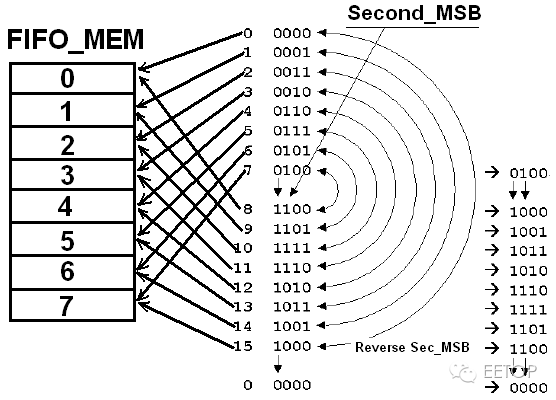

Fig. 2.4.2.1格雷碼指針和存儲空間的映射關系

如果讀指針的最高位為0,而寫指針的最高位為1,說明寫指針超前于讀指針,這時如果讀寫指針指向同一存儲空間,參照Fig. 2.4.2.1 , 則可判斷為FIFO被寫滿。寫滿標志位產生邏輯只需關心格雷碼指針最高位不同(寫超前于讀)且它們指向同一存儲空間的情況,那么怎么通過比較兩格雷碼指針來判斷這種情況的發生呢?首先,最高位相異(因為讀指針不可能超前于寫指針,所以只可能是寫指針超前于讀指針);其次,如果把最高位為1的所有格雷碼指針的次高位均取反后,除去最高位不看,則指向同一存儲空間的兩指針相同,從而得出第二個條件是:次高也相異。

Fig. 2.4.2.2寫滿標志位產生邏輯

三、總結

前文講述了異步FIFO的應用需要、實現原理,并重點闡述了空滿標志信號的產生方法以及可能會發生的“虛空”和“虛滿”現象。理解了這些關鍵信號的產生原理,設計一個異步FIFO也就不難了。

審核編輯:郭婷

-

FPGA

+關注

關注

1643文章

21944瀏覽量

613369 -

asic

+關注

關注

34文章

1242瀏覽量

121906 -

fifo

+關注

關注

3文章

400瀏覽量

44566

原文標題:異步FIFO設計(非常詳細,圖文并茂,值得一看!)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于FPGA的異步FIFO的實現

關于異步fifo的安全問題:

異步FIFO結構及FPGA設計

高速異步FIFO的設計與實現

Camera Link接口的異步FIFO設計與實現

異步FIFO結構及FPGA設計

異步FIFO的設計分析及詳細代碼

基于FPGA的異步FIFO設計方法詳解

基于異步FIFO結構原理

評論