硬件開源編程利器MyHDL簡介

Verilog缺點

自從1995年Verilog HDL 1364-1995標準發布至今已經20多年了,說他經久不衰并不恰當,主要是沒有新的語言可以替代,現今數字電路高速發展,Verilog的一些缺點暴露的越來越多,下面總結一下:

借用知乎上“馬車”的觀點:

例化不方便:有人會說,有輔助插件幫你完成 (確實有很多好的插件,emacs verilog-mode , vim 的autoinst) 即便這樣,但是對帶參數的模塊例化, 一對多例化同樣需要手動處理,非常不方便

大量的重復聲明:無休止的變量聲明,無休止的位寬聲明,容易出錯, 作為一門上古時期的語言,對編譯器不能要求太高

函數不能帶參數:verilog中函數的使用只能是零零星星,哪怕是一個位寬的變化都要重寫函數, 作為一門語言函數不能廣泛使用,實為雞肋

參數化實在是笨:雖然支持參數化,parameter 也只能做一些簡單的加減左移操作, 沒有基本math包。利用宏做參數化,對于變量比較多的設計,非常復雜,并且也不好維護

錯誤檢測很弱:編譯工具對錯誤的處理比較保守, 這種保守可能也源于語言本身,以及編譯器的能力不及。

以下問題需要工程師自己處理

位寬不匹配

input/output端口寫反

飽和截位弄錯

跨時鐘域問題鎖存器檢查組合邏輯環自己查....

基于前仿的編譯,會遺漏大量的錯誤,必須要Lint, 綜合檢查, 費時費力又費錢。

重構、增減信號,Bist/DFT邏輯插入麻煩

需要手動處理, 編寫腳本, 即便是腳本也不通用

(內容來源:https://www.zhihu.com/question/440688150 作者:溫戈 公眾號:OpenIC)

基于以上各種各樣的缺點,一些基于Verilog語言的第三方語言(本質仍然是HDL)陸續出現,像SpinalHDL,Chisel和本文的主角MyHDL都是這類語言,關于SpinalHDL,Chisel請查看(https://www.zhihu.com/question/440688150)

MyHDL介紹

你能想象有一天能用Python編寫“硬件”嗎?

(本系列基于MyHDL 0.10.0 版 on Python3)

譯自 http://docs.myhdl.org/en/stable/manual/intro.html

MyHDL項目的目標是通過python語言的優雅和簡潔性來增強硬件設計者的能力。

MyHDL是一種免費、開源的軟件包,用于使用python作為硬件描述和驗證語言。python是一種非常高級的語言,硬件設計者可以利用它的全部力量來建模和仿真他們的設計。此外,可以將設計轉換為verilog或vhdl語言。這提供了一個融入傳統設計流程的切入口。

建模

python的強大和清晰性使MyHDL成為高層次建模的理想解決方案。python以為復雜建模問題提供優雅解決方案而聞名。此外,python對于快速應用程序開發和試驗是非常優秀的。

MyHDL背后的關鍵思想是使用python生成器來建模硬件并發性。生成器最好被描述為可(從暫停狀態中)恢復函數。MyHDL生成器類似于verilog的always塊和vhdl中的過程。

一個硬件模塊(MyHDL術語中的塊)建模為返回生成器的函數。這種方法使支持諸如任意層次結構、命名端口關聯、實例數組和條件實例化等特性變得簡單明了。此外,MyHDL提供了實現傳統硬件描述概念的類。它提供了一個信號類來支持生成器之間的通信、支持面向位操作的類以及枚舉類型類。

仿真與驗證

內置仿真器運行在python解釋器的頂部。它支持通過觀看波形來跟蹤vcd文件中的信號變化。

使用MyHDL,python單元測試框架可以用于硬件設計。雖然單元測試是一種流行的現代軟件驗證技術,但在硬件設計領域還是比較少見的。

MyHDL還可以作為verilog設計的硬件驗證語言,通過與傳統的hdl模擬器進行仿真。

轉換為Verilog語言與VHDL語言

遵從一定的限制后,可將MyHDL設計轉換為verilog語言或vhdl語言,這是切入傳統設計流程的一條路徑,包括綜合和實現。可轉換子集受到限制,但比標準可綜合子集要寬得多。它包括可用于高層次建模和test benches的功能。

轉換器處理一個已完全解析的設計實例。因此,原有的設計結構可以任意復雜。此外,轉換限制僅適用于生成器內部的代碼。除了外部生成器,python的能力可以充分釋放,而不影響可轉換性。

最后,轉換器自動地實現了許多用verilog或vhdl編寫困難的任務。一個顯著點是自動處理有符號算術問題。

-

Verilog

+關注

關注

29文章

1367瀏覽量

112365 -

HDL

+關注

關注

8文章

330瀏覽量

48098 -

編譯

+關注

關注

0文章

679瀏覽量

34118

原文標題:硬件開源編程利器MyHDL簡介

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

火爆開發中 | 開源FPGA硬件板卡,硬件第一期發布

火爆開發中|開源FPGA硬件板卡,硬件第一期發布

微軟開源GitHub Copilot Chat,AI編程迎來新突破

開源FPGA硬件,核心開發者招募中......

【開源分享】:開源小巧的FPGA開發板——Icepi Zero

開源鴻蒙硬件生態分論壇圓滿舉辦

開源鴻蒙開發新體驗,開鴻Bot系列今日開啟預售!

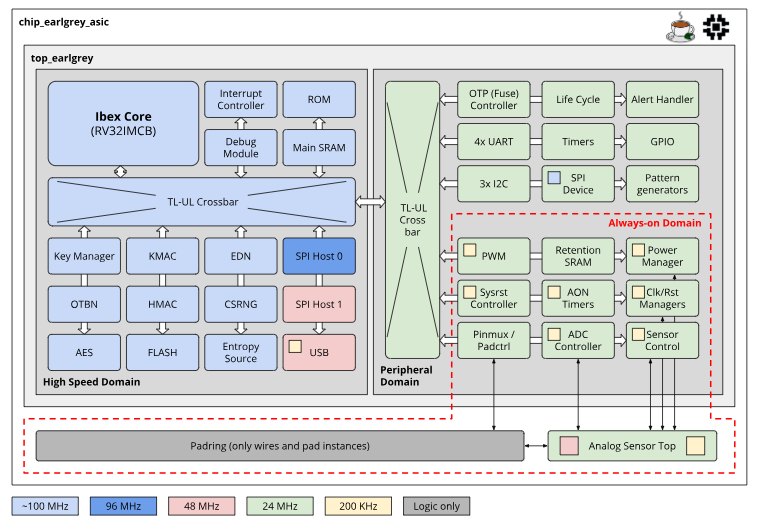

RISC V 開源芯片項目:OpenTitan 詳細解讀

明晚開播 | 開源芯片系列講座第27期:RISC-V AI指令集的標準化與開源實現

直播預約 | 開源芯片系列講座第27期:RISC-V AI指令集的標準化與開源實現

RT-Thread睿賽德出席中國工博會科技論壇,共話開源硬件與新工業革命

評論