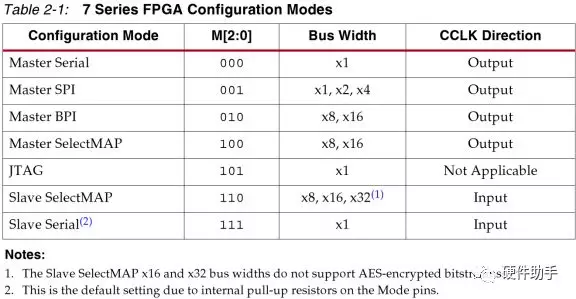

總結Xilinx FPGA的上電模式可以分為以下4類型:

主模式

從模式

JTAG模式(調試模式)

系統模式(多片配置模式)

主模式

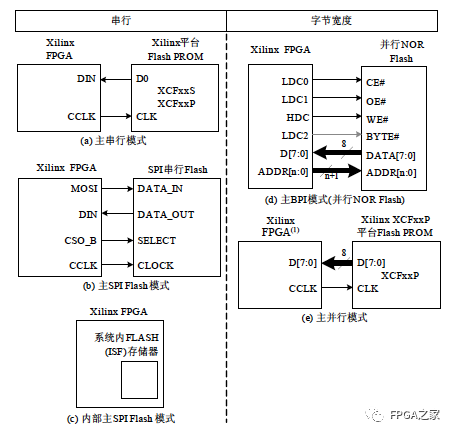

典型的主模式都是加載片外非易失( 斷電不丟數據) 性存儲器中的配置比特流,配置所需的時鐘信號( 稱為CCLK) 由FPGA內部產生,且FPGA控制整個配置過程。

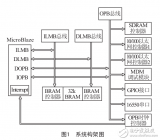

在主模式下,FPGA上電后,自動將配置數據從相應的外存儲器讀入到SRAM中,實現內部結構映射;主模式根據比特流的位寬又可以分為:串行模式( 單比特流) 和并行模式( 字節寬度比特流) 兩大類。如:主串行模式、主SPI Flash 串行模式、主并行模式等

從模式

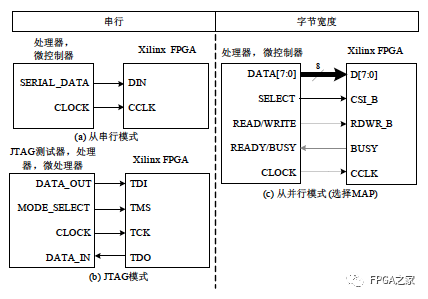

從模式需要外部的主智能終端( 如處理器、微控制器或者DSP等) 將數據下載到FPGA中,其最大的優點就是FPGA 的配置數據可以放在系統的任何存儲部位,包括:Flash、硬盤、網絡,甚至在其余處理器的運行代碼中。

在從模式下,FPGA 作為從屬器件,由相應的控制電路或微處理器提供配置所需的時序,實現配置數據的下載。從模式也根據比特流的位寬不同分為串、并模式兩類。

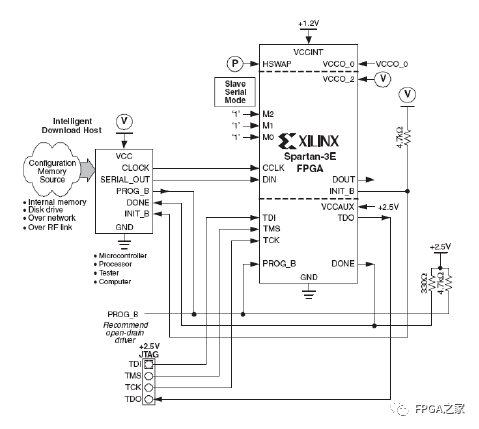

JTAG模式(調試模式)

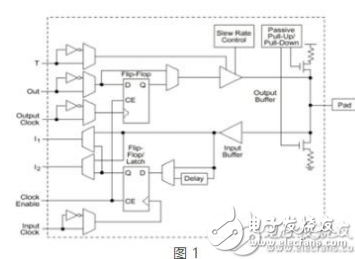

JTAG 模式為調試模式,可將PC 中的比特文件流下載到FPGA中,斷電即丟失。賽靈思公司的FPGA芯片具有IEEE 1149.1/1532協議所規定的JTAG接口,只要FPGA上電,不論模式選擇管腳M[2:0] 的電平,都可用采用該配置模式。但是將模式配置管腳設置為JTAG模式,即M[2:0]=3’b101時,FPGA芯片上電后或者PROG_B管腳有低脈沖出現后,只能通過JTAG模式配置。

在JTAG模式中,PC和FPGA通信的時鐘為JTAG接口的TCLK,數據直接從TDI進入FPGA,完成相應功能的配置。

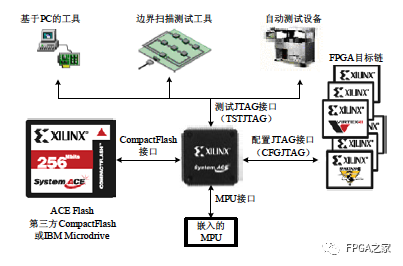

系統模式(多片配置模式)

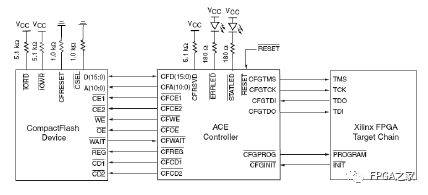

為了解決大規模FPGA的配置問題,賽靈思公司推出了系統級的System ACE(Advanced Configuration Environment) 解決方案。System ACE可在一個系統內,甚至在多個板上,對賽靈思的所有FPGA進行配置,使用Flash存儲卡或微硬盤保存配置數據,通過System ACE控制器把數據配置到FPGA中。

附:System ACE的CF(Compact Flash) 模式

System ACE CF存儲設備包括賽靈思的ACE Flash卡或其它廠家的Compact Flash卡以及IBM的微硬盤。Compact Flash卡的容量為32MB~4GB,微硬盤的容量為2GB~6GB,至少可配置數百片FPGA芯片。

System ACE CF控制器提供了存儲單元和FPGA器件之間的接口,PC和存儲器的標準JTAG接口。控制器芯片默認的配置模式也是通過邊界掃描的方式將數據配置到FPGA 鏈中,同樣可由邊界掃描鏈的測試和編程接口來輔助進行系統原形的調試。

原文標題:Xilinx FPGA的上電配置過程——進階篇

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

微控制器

+關注

關注

48文章

7542瀏覽量

151316 -

FPGA

+關注

關注

1629文章

21729瀏覽量

603008 -

Xilinx FPGA

+關注

關注

1文章

29瀏覽量

7182

原文標題:Xilinx FPGA的上電配置過程——進階篇

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Xilinx FPGA的GTx的參考時鐘

基于SRAM的FPGA分類介紹

基于TCP/IP通信技術在Xilinx FPGA上的實現

不同場景的FPGA外圍電路的上電時序分析與設計

FPGA上電后IO的默認狀態

Xilinx FPGA如何通過深度學習圖像分類加速機器學習

Xilinx FPGA之間的25Gbps傳輸數據模式介紹

Xilinx FPGA的電源設計詳解

xilinx7系列FPGA的7種邏輯代碼配置模式

Xilinx FPGA的上電模式的四種類型

XILINX FPGA簡介-型號系列分類參考

Xilinx FPGA的上電模式類型分類

Xilinx FPGA的上電模式類型分類

評論