每個 Slice 有 8 個 FF 。四個可以配置為 D 型觸發器或電平敏感鎖存器,另外四個只能配置為 D 型觸發器,但是需要記得是:當原來的四個 FF 配置為鎖存器時,不能使用這四個 FF 。

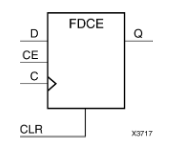

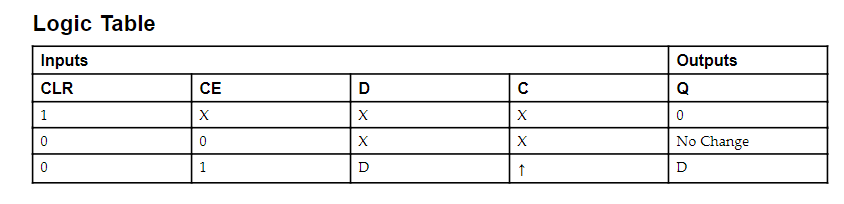

FDCE

簡介

帶有時鐘使能和異步清零的 D 觸發器

-

當時鐘使能(CE)為高并且異步清零信號 CLR 為低時,該 D 觸發器將數據輸入 D 端傳遞到輸出 Q 端。

-

當CLR為高,不管輸入是什么,輸出 Q 端值為 0。

原語

FDCE #(.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDCE_inst (.Q(Q), // 1-bit Data output.C(C), // 1-bit Clock input.CE(CE), // 1-bit Clock enable input.CLR(CLR), // 1-bit Asynchronous clear input.D(D) // 1-bit Data input);

真值表

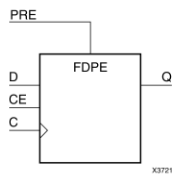

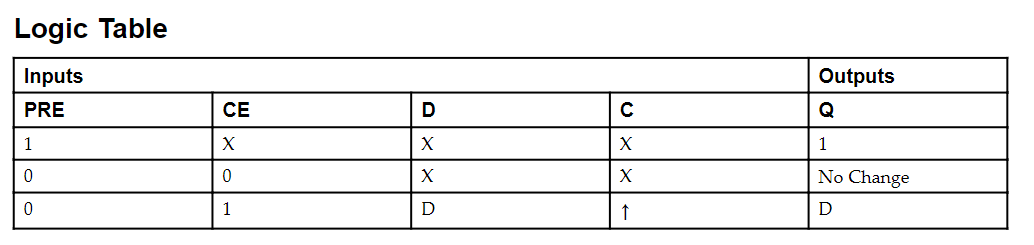

FDPE

簡介

帶有時鐘使能和異步置位的 D 觸發器

-

當時鐘使能(CE)為高并且異步置位信號 PRE 為低時,該 D 觸發器將數據輸入 D 端傳遞到輸出 Q 端。

-

當 PRE 為高,不管輸入是什么,輸出 Q 端值為 1。

原語

FDPE #(.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDPE_inst (.Q(Q), // 1-bit Data output.C(C), // 1-bit Clock input.CE(CE), // 1-bit Clock enable input.PRE(PRE), // 1-bit Asynchronous preset input.D(D) // 1-bit Data input);

真值表

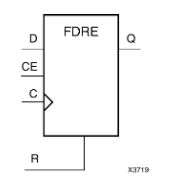

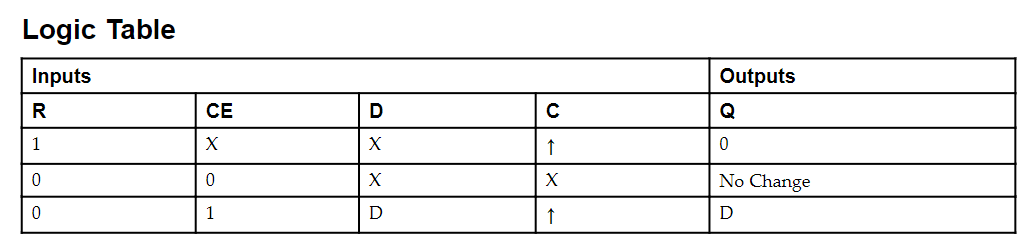

FDRE

簡介

帶有時鐘使能和同步清零的 D 觸發器

-

當時鐘使能(CE)為高并且同步清零信號 R 為低時,該 D 觸發器在時鐘上升沿將數據輸入 D 端傳遞到輸出 Q 端。

-

當 R 為高,不管輸入是什么,輸出 Q 端值為 0。

原語

FDRE #(.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDRE_inst (.Q(Q), // 1-bit Data output.C(C), // 1-bit Clock input.CE(CE), // 1-bit Clock enable input.R(R), // 1-bit Synchronous reset input.D(D) // 1-bit Data input);

真值表

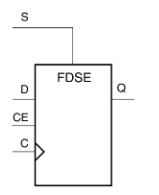

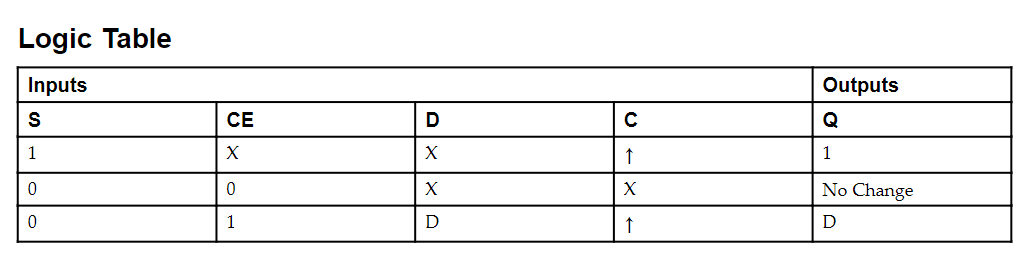

FDSE

簡介

帶有時鐘使能和同步置位的 D 觸發器

-

當時鐘使能(CE)為高并且同步置位信號 S 為低時,該 D 觸發器在時鐘上升沿將數據輸入 D 端傳遞到輸出 Q 端。

-

當 S 為高,不管輸入是什么,輸出 Q 端值為 1。

原語

FDSE #(.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDSE_inst (.Q(Q), // 1-bit Data output.C(C), // 1-bit Clock input.CE(CE), // 1-bit Clock enable input.S(S), // 1-bit Synchronous set input.D(D) // 1-bit Data input);

真值表

原文標題:參考鏈接

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

時鐘

+關注

關注

10文章

1733瀏覽量

131447 -

鎖存器

+關注

關注

8文章

906瀏覽量

41496 -

觸發器

+關注

關注

14文章

2000瀏覽量

61132

原文標題:參考鏈接

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FDCE/FDPE/FDRE/FDSE觸發器簡介

FDCE/FDPE/FDRE/FDSE觸發器簡介

評論