- 在于規(guī)范整個設計流程,實現(xiàn)開發(fā)的合理性、一致性、高效性。

- 形成風格良好和完整的文檔。

- 實現(xiàn)在FPGA不同廠家之間以及從FPGA到ASIC的順利移植。

- 便于新員工快速掌握本部門FPGA的設計流程。

由于目前所用到的FPGA器件以Altera的為主,所以下面的例子也以Altera為例,工具組合為 modelsim + Leonardo Spectrum / FPGA CompilerII + Quartus,但原則和方法對于其他廠家和工具也是基本適用的。

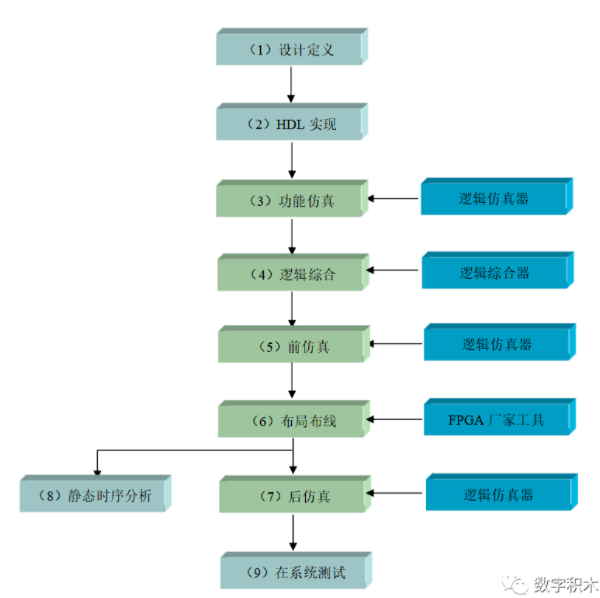

1. 設計流程概述

1.1 設計流程圖

說明:

1.2 關(guān)鍵步驟的實現(xiàn)

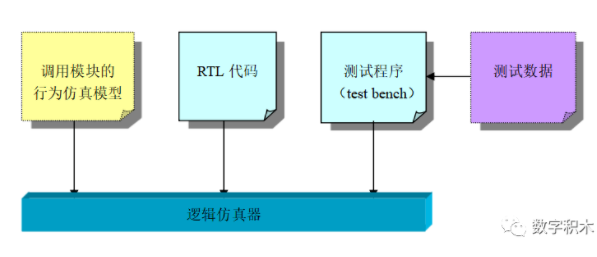

1.2.1 功能仿真

說明:

“調(diào)用模塊的行為仿真模型”指的是RTL代碼中引用的由廠家提供的宏模塊/IP,如Altera 提供的LPM庫中的乘法器、存儲器等部件的行為模型。

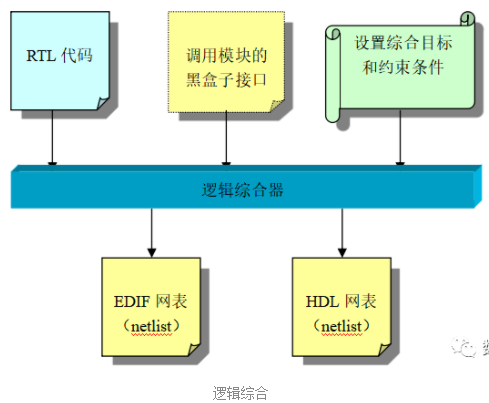

1.2.2 邏輯綜合

說明:

“調(diào)用模塊的黑盒子接口”的導入,是由于RTL代碼調(diào)用了一些外部模塊,而這些外部模塊不能被綜合或無需綜合,但邏輯綜合器需要其接口的定義來檢查邏輯并保留這些模塊的接口。

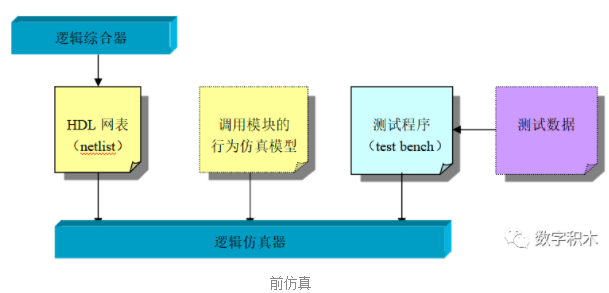

1.2.3 前仿真

一般來說,對FPGA設計這一步可以跳過不做,但可用于debug綜合有無問題。

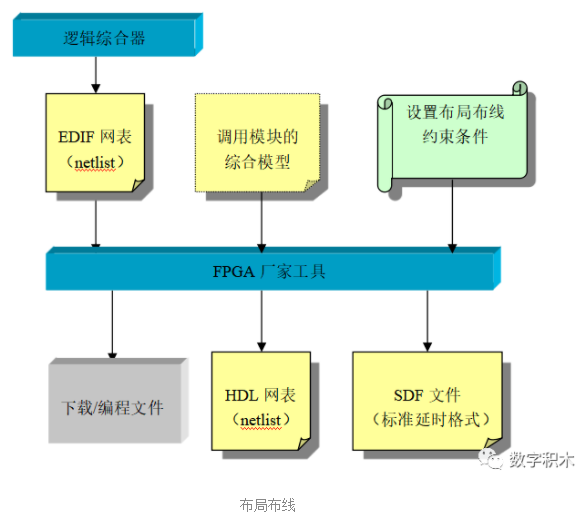

1.2.4 布局布線

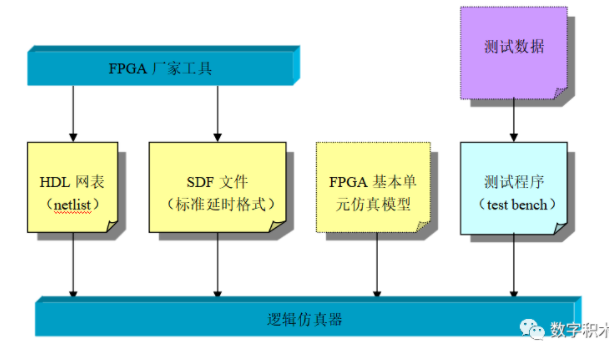

1.2.5 后仿真(時序仿真)

2. Verilog HDL設計

基于將來設計轉(zhuǎn)向ASIC的方便,本部門的設計統(tǒng)一采用Verilog HDL,但針對混合設計和混合仿真的趨勢,所有開發(fā)人員也應能讀懂VHDL。Verilog HDL的學習可參考[1][2]。

2.1 編程風格(Coding Style)要求

2.1.1 文件

(1)每個模塊(module)一般應存在于單獨的源文件中,通常源文件名與所包含模塊名相同。

(2)每個設計文件開頭應包含如下注釋內(nèi)容:

- 年份及公司名稱。

- 作者。

- 文件名。

- 所屬項目。

- 頂層模塊。

- 模塊名稱及其描述。

- 修改紀錄。

請參考標準示例程序[3]。

2.1.2 大小寫

(1)如無特別需要,模塊名和信號名一律采用小寫字母。

(2)為醒目起見,常數(shù)(`define定義)/參數(shù)(parameter定義)采用大寫字母。

2.1.3 標識符

(1)標識符采用傳統(tǒng)C語言的命名方法,即在單詞之間以“_”分開,如:max_delay、data_size等等。

(2)采用有意義的、能反映對象特征、作用和性質(zhì)的單詞命名標識符,以增強程序的可讀性。

(3)為避免標識符過于冗長,對較長單詞的應當采用適當?shù)目s寫形式,如用‘buff’代替‘buffer’,‘ena’代替‘enable’,‘addr’代替‘a(chǎn)ddress’等。

2.1.4 參數(shù)化設計

為了源代碼的可讀性和可移植性起見,不要在程序中直接寫特定數(shù)值,盡可能采用`define語句或paramater語句定義常數(shù)或參數(shù)。

2.1.5 空行和空格

(1)適當?shù)卦诖a的不同部分中插入空行,避免因程序擁擠不利閱讀。

(2)在表達式中插入空格,避免代碼擁擠,包括:

賦值符號兩邊要有空格;雙目運算符兩邊要有空格;單目運算符和操作數(shù)之間可沒有空格, 示例如下:

a <= b;c <= a + b;if (a == b) then ...a <= ~a & c;

2.1.6 對齊和縮進

- 不要使用連續(xù)的空格來進行語句的對齊。

- 采用制表符Tab對語句對齊和縮進,Tab鍵采用4個字符寬度,可在編輯器中設置。

- 各種嵌套語句尤其是if...else語句,必須嚴格的逐層縮進對齊。

2.1.7 注釋

必須加入詳細、清晰的注釋行以增強代碼的可讀性和可移植性,注釋內(nèi)容占代碼篇幅不應少于30%。

2.1.8 參考C語言的資料

要形成良好的編程風格,有許多細節(jié)需要注意,可以參考資料[4],雖然它是針對C語言的討論,但由于Verilog HDL和C語言的形式非常近似,所以里面提到的很多原則都是可以借鑒的。

2.1.9 可視化設計方法

為提高設計效率和適應協(xié)同設計的方式,可采用可視化的設計方法,Mentor Grahpics的Renoir軟件提供了非常好的設計模式。

2.2 可綜合設計

用HDL實現(xiàn)電路,設計人員對可綜合風格的RTL描述的掌握不僅會影響到仿真和綜合的一致性,也是邏輯綜合后電路可靠性和質(zhì)量好壞最主要的因素,對此應當予以充分的重視。學習可綜合的HDL請參考 [5][6] [7]。學習設計的模塊劃分請參考[8]。

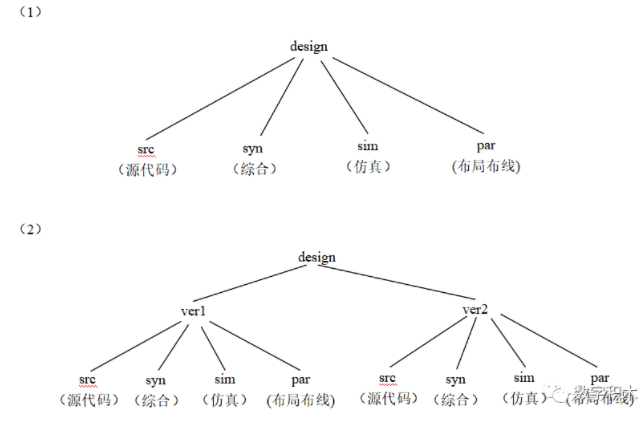

2.3 設計目錄

采用合理、條理清晰的設計目錄結(jié)構(gòu)有助于提高設計的效率、可維護性。建議采用類似下面的目錄結(jié)構(gòu):

3. 邏輯仿真

考慮到性能和易用性,首選的邏輯仿真器是Mentor Graphics的modelsim。

3.1 測試程序(test bench)

測試程序?qū)τ谠O計功能和時序的驗證有著舉足輕重的影響,測試激勵的完備性和真實性是關(guān)鍵所在,有以下原則須遵循:

(1)測試激勵輸入和響應輸出采集的時序應當兼顧功能仿真(無延時)和時序仿真(有延時)的情況。

(2)對于周期較多的測試,為提高效率,盡可能采用程序語句來判斷響應與標準結(jié)果是否一致,給出成功或出錯標志,而不是通過觀察波形來判斷。

(3)采用基于文件的測試是很好的辦法,即由matlab或spw等系統(tǒng)工具產(chǎn)生測試數(shù)據(jù),測試程序?qū)⑵渥x入產(chǎn)生激勵,再把響應結(jié)果寫入到文件,再交給上述工具進行處理或分析。

(4)仿真器支持幾乎所有的Verilog HDL語法,而不僅僅是常用的RTL的描述,應當利用這一點使測試程序盡可能簡潔、清楚,篇幅長的要盡量采用task來描述。

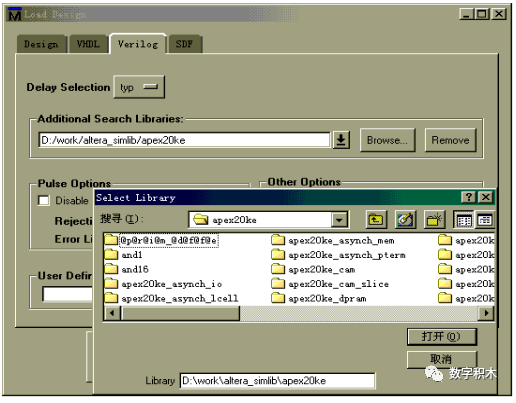

3.2 使用預編譯庫

在進行功能仿真和后仿真時都需要某些模塊的行為仿真模型和門級仿真模型,如Altera Quartus里的220model.v(LPM模塊行為仿真模型)和apex20ke_atoms.v(20KE系列門級仿真模型),為避免在不同的設計目錄中多次編譯這些模型,應當采用一次編譯,多次使用的方法。具體做法如下(以20KE門級庫為例):

1:在某個工作目錄下新建一庫名 apex20ke,將apex20ke_atoms.v編譯到其中。2:在圖形界面中的Load Design對話框中裝入仿真設計時,在Verilog 標簽下指定預編譯庫的完整路徑。(見下圖)

4. 邏輯綜合

目前可用的FPGA綜合工具有Mentor Graphics 的 Leonardo Spectrum,Synplicity 的 Synplify 和 Synopsys 的FPGA CompilerII / FPGA Express,Leonardo Spectrum由于性能和速度最好,成為我們首選的綜合器,F(xiàn)PGA CompilerII / FPGA Express由于可以和Design Compiler代碼兼容也可用。見參考[9]

4.1 邏輯綜合的一些原則

HDL代碼綜合后電路質(zhì)量的好壞主要取決于三個方面,參考[10]中有比較全面的討論。:

- RTL實現(xiàn)是否合理、

- 對廠家器件特點的理解

- 對綜合器掌握的程度。

4.1.1 關(guān)于LeonardoSpectrum

LeonardoSpectrum對綜合的控制能力比較強,但使用也略為復雜,故需要在使用前盡量熟悉其功能,才能取得較好的綜合結(jié)果。當出現(xiàn)綜合結(jié)果不能滿足約束條件時,不要急于修改設計源文件,應當通過綜合器提供的時序和面積分析命令找出關(guān)鍵所在,然后更改綜合控制或修改代碼。

在LeonardoSpectrum 2000.1b以前的版本輸出的 .v 網(wǎng)表都不能用于仿真。

4.1.2 大規(guī)模設計的綜合

分塊綜合

當設計規(guī)模很大時,綜合也會耗費很多時間。如果設計只更改某個模塊時,可以分塊綜合。如有設計 top.v 包含 a.v和b.v兩個模塊,當只修改a.v的話,可以先單獨綜合b.v,輸出其網(wǎng)表b.edf,編寫一個b模塊的黑盒子接口b_syn.v,每次修改a.v后只綜合top.v、a.v、b_syn.v,將綜合后的網(wǎng)表和b.edf送去布線,可以節(jié)約綜合b模塊的時間。

采用腳本命令

當設計規(guī)模比較大時,綜合控制也許會比較復雜,可以考慮采用腳本控制文件的方式進行綜合控制,modelsim、Leonardo Spectrum 和 Quartus 都支持TCL(Tool Command Language)語言,采用腳本控制可以提供比圖形界面更靈活和更方便的控制手段。

4.1.3 必須重視工具產(chǎn)生的警告信息

綜合工具對設計進行處理可能會產(chǎn)生各種警告信息,有些是可以忽略的,但設計者應該盡量去除,不去除必須確認每條警告的含義,避免因此使設計的實現(xiàn)產(chǎn)生隱患。這個原則對仿真和布局布線同樣適用。

4.2 調(diào)用模塊的黑盒子(Black box)方法

使用黑盒子方法的原因主要有兩點:

一是HDL代碼中調(diào)用了一些FPGA廠家提供的模塊(如Altera的LPM模塊)或第三方提供的IP,這些模塊不需要綜合,而且有些綜合器也不能綜合(如FPGA CompilerII/FPGA Express可以綜合包含LPM的代碼而LeonardoSpectrum不能)。因此須提供一個黑盒子接口給綜合器,所調(diào)用的模塊到布局布線時才進行連接。

二是方便代碼的移植,由于廠家提供的模塊或第三方提供的IP通常都是與工藝有關(guān)的,直接在代碼中調(diào)用的話將不利于修改,影響代碼移植。

下面以調(diào)用Altera的LPM庫中的乘法器為例來說明。調(diào)用這樣一個模塊需要這樣一個文件:mult8x8.v(可由Quartus的MegaWizer Plug-in Manager產(chǎn)生),代碼如下:

// mult8x8.vmodule mult8x8 (dataa, datab, result);input [7:0] dataa;input [7:0] datab;output [15:0] result;// exemplar translate_off// synopsys translate_offlpm_mult lpm_mult_component(.dataa (dataa),.datab (datab),.aclr (1'b0),.clock (1'b0),.clken (1'b0),.sum (1'b0),.result (result));defparamlpm_mult_component.lpm_widtha = 8,lpm_mult_component.lpm_widthb = 8,lpm_mult_component.lpm_widths = 16,lpm_mult_component.lpm_widthp = 16,lpm_mult_component.lpm_representation = "SIGNED",// exemplar translate_on// synopsys translate_onendmodule

注意上述的代碼有兩對編譯指示:

> // exemplar translate_off 和 // exemplar translate_on (Leonardo Spectrum 支持)> // synopsys translate_off 和 // synopsys translate_on(Leonardo Spectrum 和 FPGA CompilerII都支持)

對于相應的綜合器,在這些編譯指示中間的語句將會被忽略,那我們可以看到在綜合過程中模塊mult8x8實際變成了一個只有I/O定義的空盒子(即black box),所以該部分的代碼沒有連接,在Quartus布局布線的時候,lpm模塊的代碼才連接到整個設計,在仿真的時候,編譯指示不影響模塊的完整性。

審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

602993 -

asic

+關(guān)注

關(guān)注

34文章

1199瀏覽量

120436 -

存儲器

+關(guān)注

關(guān)注

38文章

7484瀏覽量

163763

發(fā)布評論請先 登錄

相關(guān)推薦

TCL服務技術(shù)規(guī)范

DVB條件接收同密前端系統(tǒng)結(jié)構(gòu)和同步技術(shù)規(guī)范 pdf

華為企業(yè)技術(shù)規(guī)范--防護電路設計規(guī)范

尋找irda技術(shù)規(guī)范

如何更好地理解各種抖動技術(shù)規(guī)范

LED隧道燈推薦性技術(shù)規(guī)范

電氣安全技術(shù)規(guī)范

最核心4大NFC技術(shù)規(guī)范詳解

電動汽車交流充電樁技術(shù)規(guī)范

FPGA設計流程和技術(shù)規(guī)范

FPGA設計流程和技術(shù)規(guī)范

評論