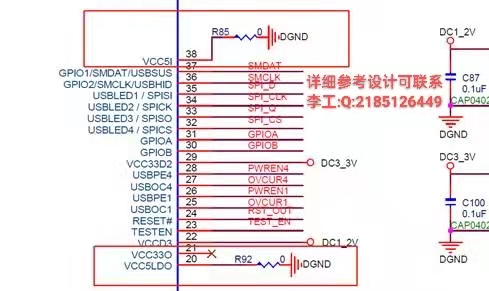

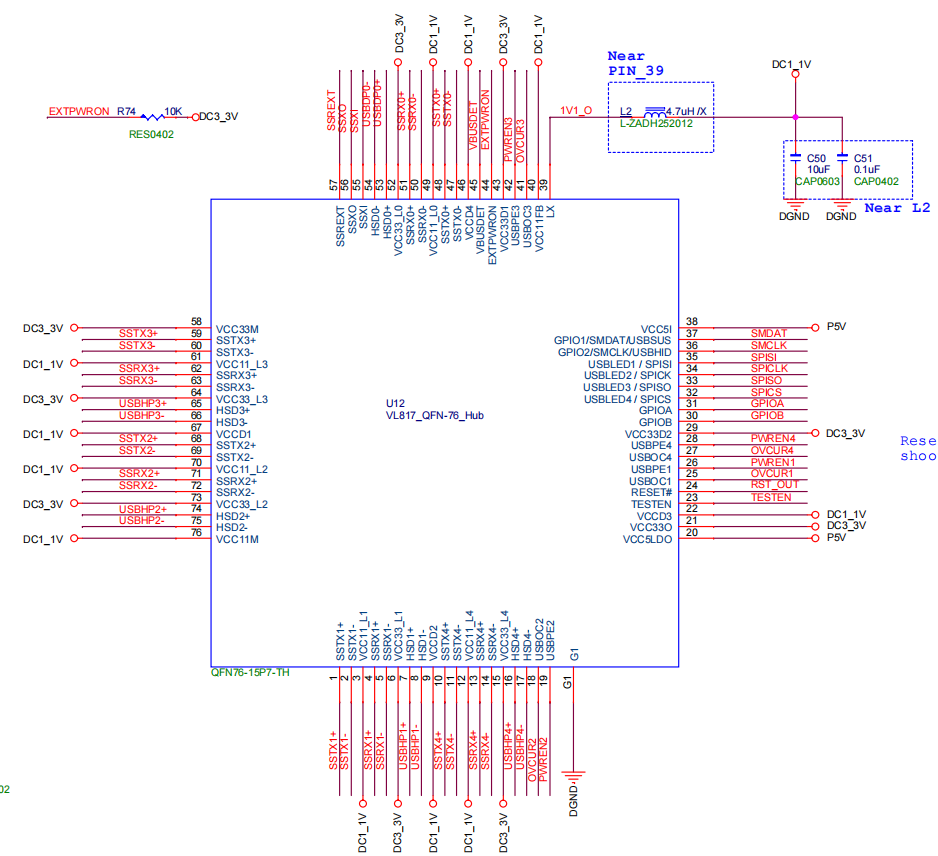

相對于VL817C0以及VL817B0來說,VL817S使用外部供電不需要接入5V,HUB 5V 請參考參考設計接地。內部3.3 LDO輸出請懸空。1。2V LX和FB請懸空。如下所示,詳見參考設計。

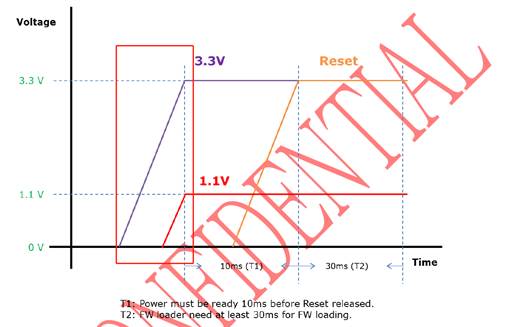

1、3.3V和1.2V之間的時序要求是怎么樣的?

下圖是VL817(S) 上電時序。參考線路中有增加不上件0。1uF調整時序。

2,各電源的紋波要求是怎么樣的?

沒有特別要求。DC-DC基本都可以滿足紋波要求

3、817B0/C0和817S這三款芯片的對比測試數據以及產品替換,可根據你們

的數據來評估重點測試內容及注意事項

內部測試目前來說OK,可進行PIN TO PIN D迭代代替

4、需要提供LAYOUT指導說明文件或者參考的PCB文件

請對比VL817B0/C0規格書以及相關原理圖,結合以上更改參數進行對照修改。

VL817相關原理圖:

VL817 Power On Sequence上電時序:

1.1V 和3.3V 理論上需要同時起來,誤差需保證兩個電壓上電間隔超過1mS

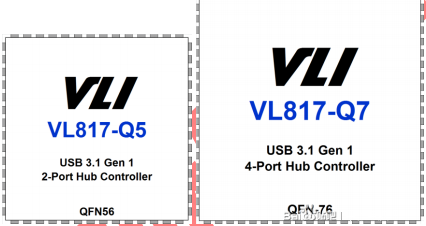

以上即是VL817S與其他型號相同之處,但是總的來說:

1. VL817 C0/B0 與VL817S pin to pin 的產品

2. VL817 C0/B0與 VL817S均為獨立FW

3. VL817 S為VL817C0//B0的進階版本

4. VL817S采用外置LDO供電,

并且VL817-Q7S(A1)性價比更高。

審核編輯:湯梓紅

-

芯片

+關注

關注

456文章

50892瀏覽量

424335 -

控制

+關注

關注

4文章

1011瀏覽量

122680 -

hub

+關注

關注

1文章

115瀏覽量

41743

發布評論請先 登錄

相關推薦

BJT與其他半導體器件的區別

PROM器件與其他存儲器的區別

Orin芯片與其他芯片對比

NAND Flash與其他類型存儲器的區別

肖特基二極管與其他二極管的區別

PLC如何與其他設備進行通信

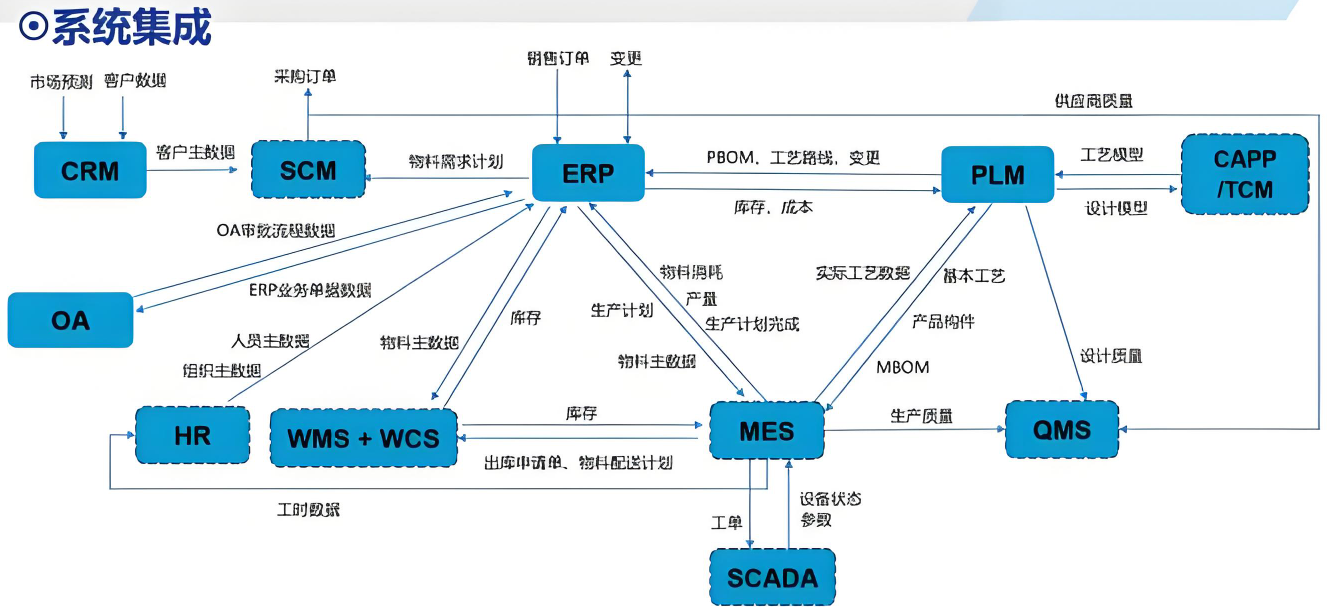

MES管理系統與其他系統的集成

817光耦和2501光耦區別 2501光耦可以代替pc817嗎

TLP521與PC817的區別

pc817光耦ABC檔有什么區別

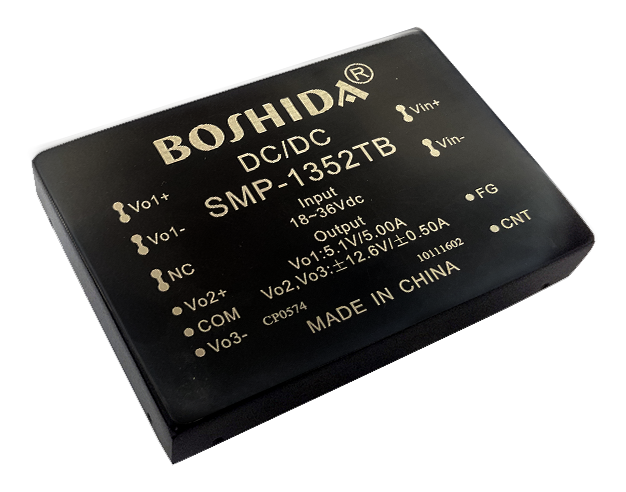

DC電源模塊與其他電源模塊的區別與優勢

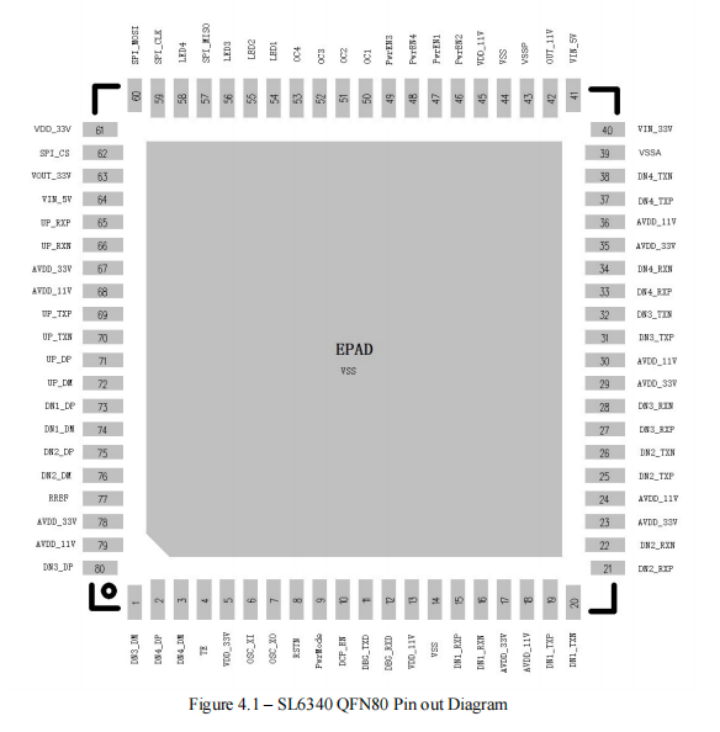

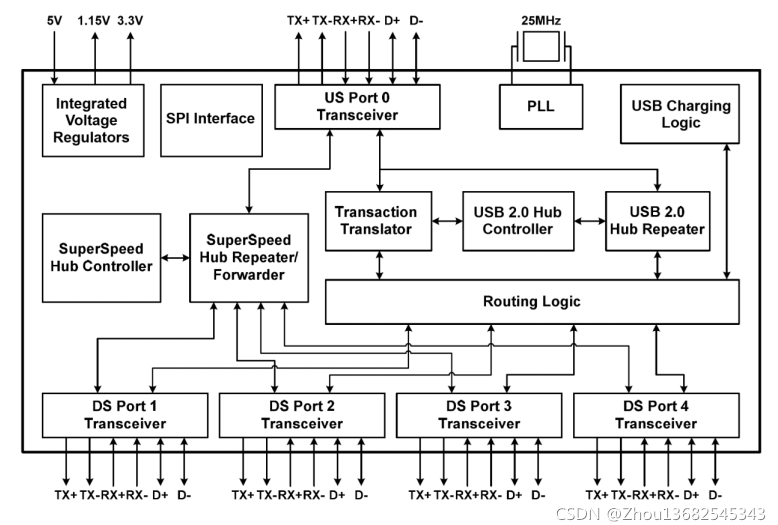

SL6340是國產USB3.0 HUB芯片,一擴四,替換RTS5411/GL3510/VL817,適用于擴展塢/延長/電腦等

HUB控制芯片VL817S與其他型號的區別及改動

HUB控制芯片VL817S與其他型號的區別及改動

評論