Q1

請教下各位,如果芯片尺寸很大,12寸wafer可能一片wafer只有300顆die。每顆成本很高,做可靠性測試的樣本數(shù)量能適當(dāng)減少嗎?

A

可以的,特別昂貴的芯片,可以降低抽樣率。

Q2

請教群里大神,F(xiàn)T發(fā)現(xiàn)批量性O(shè)S超標(biāo),開蓋發(fā)現(xiàn)都是固定Pad位置ESD保護(hù)管燒傷,一般會是什么原因造成?

A

這種插指結(jié)構(gòu)是典型的ESD clamp結(jié)構(gòu)。這種電測后ESD電路damage的現(xiàn)象并不少見,但最終能找到root cause較少,主要是因為high current damage destroyed損壞了證據(jù)。FA盡量的找一些燒得比較輕微的FIB/top down delayer,如果運氣好的話也許能找到蛛絲馬跡。但我覺得也許可以同時做一些數(shù)據(jù)分析/DOE/ESD測試也許更有幫助。可以搞幾顆Die 快封后打打ESD看,是否可以復(fù)現(xiàn),再確認(rèn)一下改善哪些有可能ESD的地方,改善到什么程度。

Q3

請教個問題,有個產(chǎn)品做靜電測試。在外協(xié)方測試,vin和gnd過不了2000V,在我們自己實驗室,可以過3000V。除了靜電測試設(shè)備差異,還會是什么原因,可以造成結(jié)差異?

A

1.建議對比測試機臺類型。

2.建議對比采用測試標(biāo)準(zhǔn),一般會誤導(dǎo)把系統(tǒng)級ESD和芯片級ESD混淆。

3.對比測試方法,一定要一比一的對比,很多時候VIN到GND自己ESD本身沒有問題,而且一些IO 管腳的ESD繞道電源到底打死VIN。

4.可以考慮外協(xié)機臺是否寄生電容導(dǎo)致結(jié)果不一致,驗證方法是讓外協(xié)采用Two pin的方式進(jìn)行,減少寄生。

Q4

如果我們用TLP測試機再試試,看和hbm測試設(shè)備的結(jié)果對比,是否有意義?

A

個人感覺只能作為參考,兩者的波形不同,內(nèi)部電路的寄生情況可能會降低參考價值吧。

Q5

請教大家:銀線WB不能做bHAST嗎?是否有業(yè)界規(guī)范?

A

銀焊線建議要做b-HAST考核。

Q6

據(jù)了解,工廠一般不會做,因為失效率較高,建議做的原因是什么?

A

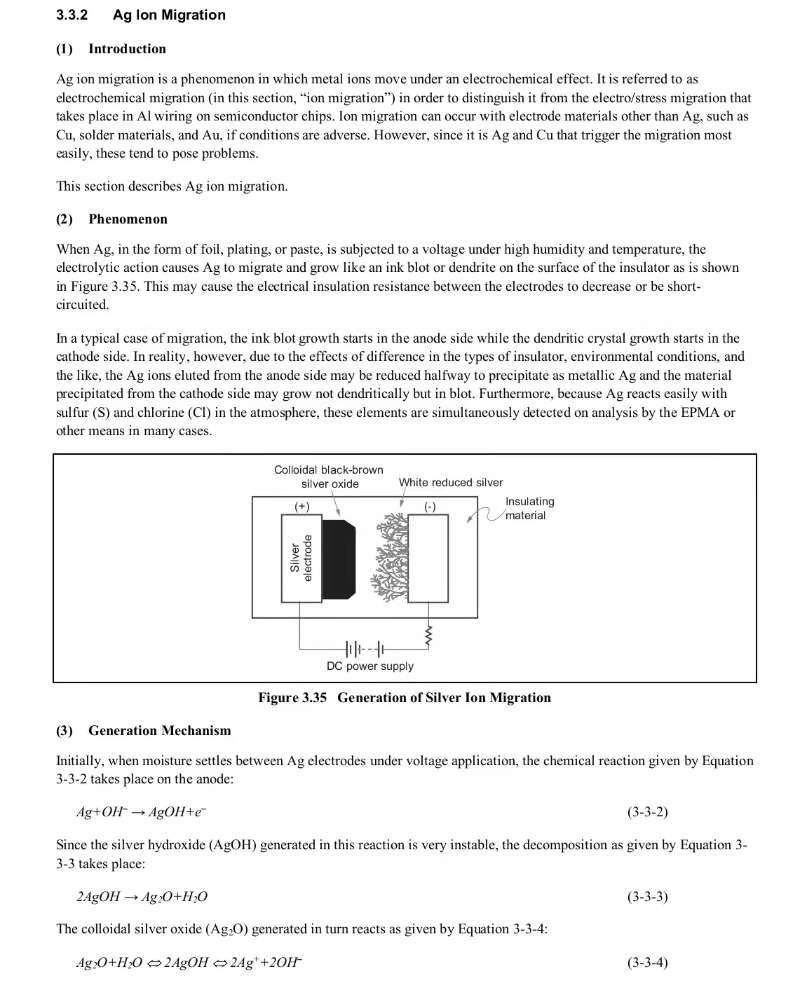

帶電工作的情況下,Ag可能會發(fā)生電化學(xué)反應(yīng),出現(xiàn)Ag離子遷移情況。

Q7

想請教一下:

1.gate oxide layer如何形成缺陷?

2.如何預(yù)防解決gate oxide layer的缺陷,防止gate oxide擊穿?

3.都說導(dǎo)致空洞最大原因跟封裝廠貼片有關(guān),那除了貼片原因外,還有什么情況也會導(dǎo)致空洞的發(fā)生?

A

有FN tunneling效應(yīng)在,不可能存在所謂不會被擊穿的gate oxide,其它gate oxide相關(guān)的可以搜索下GOI/TDDB詞條。常見氧化層缺陷有污漬,局部變薄,針孔,氧空位等。取決于fab長膜工藝及機臺穩(wěn)定性。

Q8

咨詢大家一個問題:如果把CP pad放在劃片槽里面,會不會后續(xù)引起什么問題?但是這種CP pad還是要和內(nèi)部電路相連接的,劃的時候會不會出什么可靠性問題,我的意思是為了省面積,把CP pad放在劃片槽,但是要和seal ring 里面的電路連接,或者把CP pad放在電路的上面有啥問題么?

A

CP pad不要放,PAD應(yīng)該是最終被劃掉的,不會打線,但你如果用CP pad劃片等于上下打穿了,PAD和下面ESD電路短接,最終會不會對你整個芯片帶來影響。

Q9

那您的意思,放在劃片槽里的pad 就用頂層金屬做即可?另外需不需要把劃片槽做寬一點?可不可以做DFT目的的CP pad?

A

這種應(yīng)該可以吧,我們以前見過是把燒fuse 用PAD放劃片槽,沒必要把劃片槽做寬,你PAD可以縮小的。

Q10

請問客戶在BGA周圍點膠了,現(xiàn)在用熱風(fēng)槍吹不下來。請問有什么辦法可以解焊嗎?類似這樣的

A

點膠是無法解焊的,要取下封裝只能把板子用研磨的方法研磨去除,后續(xù)再針對錫球重新值球。

Q11

請教大家一個問題:請問一下對于模擬IC類以及功率器件類器件bHAST試驗怎么加電,是以最小功率讓其工作起來,還是給直流偏置?

A

bHAST加直流偏置電壓,這是封裝可靠性項目,不是產(chǎn)品設(shè)計考核項目。不必讓進(jìn)入芯片工作模式。不能工作起來,防止發(fā)熱阻擋水汽進(jìn)入。

Q12

請教一下 如果package reliability 測試前后只測試 open short會有什么風(fēng)險,如果不測試function ?

A

有可能一些漏電的失效發(fā)現(xiàn)不到。

Q13

各位,請教個問題,對于雙向的IO pin,Latch up 測試的時候是作為INPUT PIN還是Out pin?

A

具體做輸入還是輸出要看當(dāng)前配置的狀態(tài)是輸入還是輸出。

原文標(biāo)題:季豐電子IC運營工程技術(shù)知乎 –22W10

文章出處:【微信公眾號:上海季豐電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423144 -

ESD

+關(guān)注

關(guān)注

48文章

2029瀏覽量

172929 -

靜電測試

+關(guān)注

關(guān)注

0文章

17瀏覽量

9445

原文標(biāo)題:季豐電子IC運營工程技術(shù)知乎 –22W10

文章出處:【微信號:zzz9970814,微信公眾號:上海季豐電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

為什么capture/library 里的元件不能做仿真?

用AD8367做音頻AGC不能做到AGC

用AD8367為什么不能做音頻AGC?

人工智能仍然不能做也不能理解的5個方面

納米銀線的應(yīng)用將是柔性觸控領(lǐng)域的突破

納米銀線將成為未來柔性觸控的新材料

STM32WB55_NUCLEO開發(fā)(7)----手機與STM32WB進(jìn)行綁定

AN5597_STM32WB3或5xxx和STM32WB1xxx應(yīng)用筆記

DB4388_NUCLEO_WB55RG NUCLEO_WB15CC 數(shù)據(jù)手冊摘要

GaN HEMT為什么不能做成低壓器件

封裝可靠性之BHAST試驗簡析

網(wǎng)線銅包銀線與銅線哪個好

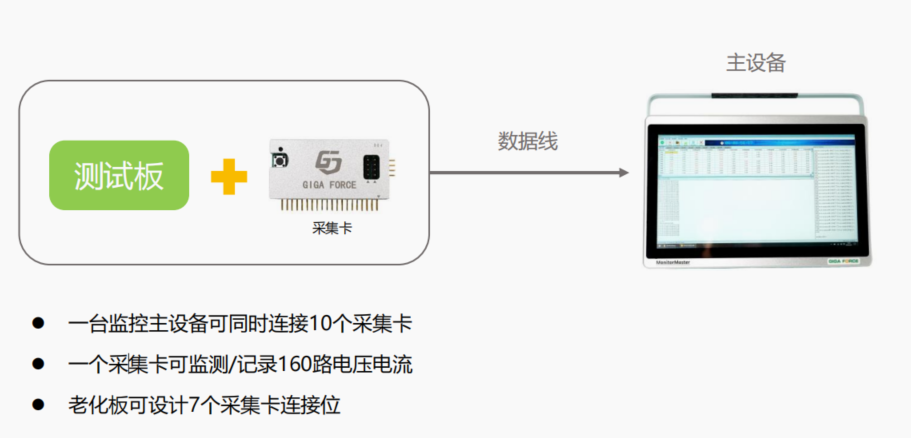

季豐電子MonitorMaster系統(tǒng)在BHAST實驗中的應(yīng)用

銀線WB不能做bHAST嗎

銀線WB不能做bHAST嗎

評論