對(duì)于設(shè)計(jì)者來(lái)說(shuō),當(dāng)然希望我們?cè)O(shè)計(jì)的電路的工作頻率(在這里如無(wú)特別說(shuō)明,工作頻率指FPGA片內(nèi)的工作頻率)盡量高。我們也經(jīng)常聽(tīng)說(shuō)用資源換速度,用流水的方式可以提高工作頻率,這確實(shí)是一個(gè)很重要的方法,今天我想進(jìn)一步去分析該如何提高電路的工作頻率。

我們先來(lái)分析下是什么影響了電路的工作頻率。我們電路的工作頻率主要與寄存器到寄存器之間的信號(hào)傳播時(shí)延及clock skew有關(guān)。在FPGA內(nèi)部如果時(shí)鐘走長(zhǎng)線的話,clock skew很小,基本上可以忽略, 在這里為了簡(jiǎn)單起見(jiàn),我們只考慮信號(hào)的傳播時(shí)延的因素。信號(hào)的傳播時(shí)延包括寄存器的開(kāi)關(guān)時(shí)延、走線時(shí)延、經(jīng)過(guò)組合邏輯的時(shí)延(這樣劃分或許不是很準(zhǔn)確,不過(guò)對(duì)分析問(wèn)題來(lái)說(shuō)應(yīng)該是沒(méi)有可以的),要提高電路的工作頻率,我們就要在這三個(gè)時(shí)延中做文章,使其盡可能的小。

我們先來(lái)看開(kāi)關(guān)時(shí)延,這個(gè)時(shí)延是由器件物理特性決定的,我們沒(méi)有辦法去改變,所以我們只能通過(guò)改變走線方式和減少組合邏輯的方法來(lái)提高工作頻率。

1.通過(guò)改變走線的方式減少時(shí)延。以altera的器件為例,我們?cè)?a href="http://www.1cnz.cn/tags/quartus/" target="_blank">quartus里面的timing closure floorplan可以看到有很多條條塊塊,我們可以將條條塊塊按行和按列分,每一個(gè)條塊代表1個(gè)LAB,每個(gè)LAB里有8個(gè)或者是10個(gè)LE。它們的走線時(shí)延的關(guān)系如下:同一個(gè)LAB中(最快) < 同列或者同行 < 不同行且不同列。

我們通過(guò)給綜合器加適當(dāng)?shù)募s束(不可貪心,一般以加5%裕量較為合適,比如電路工作在100Mhz,則加約束加到105Mhz就可以了,貪心效果反而不好,且極大增加綜合時(shí)間)可以將相關(guān)的邏輯在布線時(shí)盡量布的靠近一點(diǎn),從而減少走線的時(shí)延。(注:約束的實(shí)現(xiàn)不完全是通過(guò)改進(jìn)布局布線方式去提高工作頻率,還有其它的改進(jìn)措施)

2.通過(guò)減少組合邏輯的減少時(shí)延。上面我們講了可以通過(guò)加約束來(lái)提高工作頻率,但是我們?cè)谧鲈O(shè)計(jì)之初可萬(wàn)萬(wàn)不可將提高工作頻率的美好愿望寄托在加約束上,我們要通過(guò)合理的設(shè)計(jì)去避免出現(xiàn)大的組合邏輯,從而提高電路的工作頻率,這才能增強(qiáng)設(shè)計(jì)的可移植性,才可以使得我們的設(shè)計(jì)在移植到另一同等速度級(jí)別的芯片時(shí)還能使用。

我們知道,目前大部分FPGA都基于4輸入LUT的,如果一個(gè)輸出對(duì)應(yīng)的判斷條件大于四輸入的話就要由多個(gè)LUT級(jí)聯(lián)才能完成,這樣就引入一級(jí)組合邏輯時(shí)延,我們要減少組合邏輯,無(wú)非就是要輸入條件盡可能的少,這樣就可以級(jí)聯(lián)的LUT更少,從而減少了組合邏輯引起的時(shí)延。

我們平時(shí)聽(tīng)說(shuō)的流水就是一種通過(guò)切割大的組合邏輯(在其中插入一級(jí)或多級(jí)D觸發(fā)器,從而使寄存器與寄存器之間的組合邏輯減少)來(lái)提高工作頻率的方法。比如一個(gè)32位的計(jì)數(shù)器,該計(jì)數(shù)器的進(jìn)位鏈很長(zhǎng),必然會(huì)降低工作頻率,我們可以將其分割成4位和8位的計(jì)數(shù),每當(dāng)4位的計(jì)數(shù)器計(jì)到15后觸發(fā)一次8位的計(jì)數(shù)器,這樣就實(shí)現(xiàn)了計(jì)數(shù)器的切割,也提高了工作頻率。

在狀態(tài)機(jī)中,一般也要將大的計(jì)數(shù)器移到狀態(tài)機(jī)外,因?yàn)橛?jì)數(shù)器這東西一般是經(jīng)常是大于4輸入的,如果再和其它條件一起做為狀態(tài)的跳變判據(jù)的話,必然會(huì)增加LUT的級(jí)聯(lián),從而增大組合邏輯。以一個(gè)6輸入的計(jì)數(shù)器為例,我們?cè)M?dāng)計(jì)數(shù)器計(jì)到111100后狀態(tài)跳變,現(xiàn)在我們將計(jì)數(shù)器放到狀態(tài)機(jī)外,當(dāng)計(jì)數(shù)器計(jì)到111011后產(chǎn)生個(gè)enable信號(hào)去觸發(fā)狀態(tài)跳變,這樣就將組合邏輯減少了。

上面說(shuō)的都是可以通過(guò)流水的方式切割組合邏輯的情況,但是有些情況下我們是很難去切割組合邏輯的,在這些情況下我們又該怎么做呢?

狀態(tài)機(jī)就是這么一個(gè)例子,我們不能通過(guò)往狀態(tài)譯碼組合邏輯中加入流水。如果我們的設(shè)計(jì)中有一個(gè)幾十個(gè)狀態(tài)的狀態(tài)機(jī),它的狀態(tài)譯碼邏輯將非常之巨大,毫無(wú)疑問(wèn),這極有可能是設(shè)計(jì)中的關(guān)鍵路徑。那我們?cè)撛趺醋瞿?還是老思路,減少組合邏輯。我們可以對(duì)狀態(tài)的輸出進(jìn)行分析,對(duì)它們進(jìn)行重新分類,并根據(jù)這個(gè)重新定義成一組組小狀態(tài)機(jī),通過(guò)對(duì)輸入進(jìn)行選擇(case語(yǔ)句)并去觸發(fā)相應(yīng)的小狀態(tài)機(jī),從而實(shí)現(xiàn)了將大的狀態(tài)機(jī)切割成小的狀態(tài)機(jī)。在ATA6的規(guī)范中(硬盤(pán)的標(biāo)準(zhǔn)),輸入的命令大概有20十種,每一個(gè)命令又對(duì)應(yīng)很多種狀態(tài),如果用一個(gè)大的狀態(tài)機(jī)(狀態(tài)套狀態(tài))去做那是不可想象的,我們可以通過(guò)case語(yǔ)句去對(duì)命令進(jìn)行譯碼,并觸發(fā)相應(yīng)的狀態(tài)機(jī),這樣做下來(lái)這一個(gè)模塊的頻率就可以跑得比較高了。

總結(jié):提高工作頻率的本質(zhì)就是要減少寄存器到寄存器的時(shí)延,最有效的方法就是避免出現(xiàn)大的組合邏輯,也就是要盡量去滿足四輸入的條件,減少LUT級(jí)聯(lián)的數(shù)量。我們可以通過(guò)加約束、流水、切割狀態(tài)的方法提高工作頻率。

原文標(biāo)題:如何提高FPGA的運(yùn)行速度

文章出處:【微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1629文章

21754瀏覽量

604234 -

電路

+關(guān)注

關(guān)注

172文章

5933瀏覽量

172459 -

頻率

+關(guān)注

關(guān)注

4文章

1511瀏覽量

59268

原文標(biāo)題:如何提高FPGA的運(yùn)行速度

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

設(shè)計(jì)一個(gè)儀表放大電路,其中的性能該如何提高?

求解釋該無(wú)線發(fā)射電路工作原理

labview通過(guò)myrio采樣 采樣頻率過(guò)低 該如何提高

工作接地按工作頻率而采用的幾種接地方式

請(qǐng)教如何提高rkvdec的工作頻率?

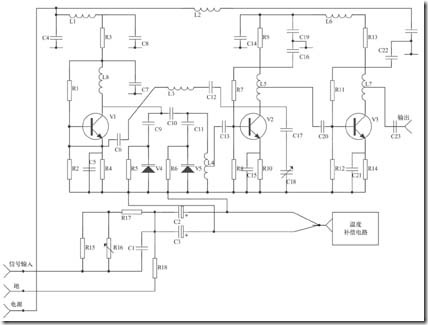

提高變?nèi)荻O管調(diào)頻電路頻率穩(wěn)定度的溫度補(bǔ)償方法

工作頻率可變的信號(hào)發(fā)生器電路

頻率解調(diào)器設(shè)計(jì)電路

該如何提高電路的工作頻率

該如何提高電路的工作頻率

評(píng)論