前言

每一次神舟載人飛船和SpaceX衛星的發射升空,都能吸引眾多人關注。對于這些神秘的航天飛信器,你知道它們的信息都是怎么處理的嗎?航天飛行器信息的處理依靠CPU/FPGA,而指令的執行則憑借存儲器。目前市場上大多數售賣主芯片的廠商都是靠存儲器起家的。Excelpoint世健公司的工程師Wolfe Yu在此對存儲的分類以及它們各自的優劣進行了科普介紹。

半導體存儲器功能分類

半導體存儲器是一種能存儲大量二進制信息的半導體器件,半導體存儲器種類很多,一般按功能來分,可以分為只讀存儲器(ROM)和隨機存儲器(RAM)。

ROM結構簡單,斷電以后數據還保留著;重新上電,讀出來的數據還能恢復成原來的樣子。

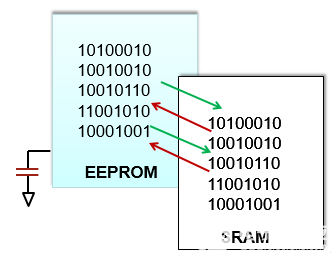

圖1 ROM重新上電信息保留

RAM就不一樣了,每次上電之后,上一次的信息無法保留。

圖2 RAM重新上電信息丟失

只讀存儲器(ROM)

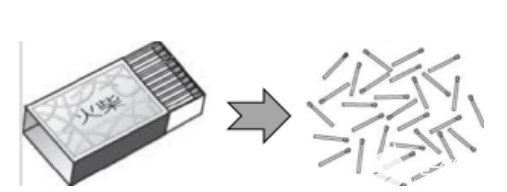

只讀存儲器主要分為掩膜存儲器、可編程存儲器(PROM)、電可擦寫可編程存儲器(EEPROM)和Flash等等。

早期只讀存儲器一覽

掩膜只讀存儲器:定制產品,按照用戶要求來,內部數據在出廠時就被設定好,后續無法修改。

可編程只讀存儲器:也叫“反熔絲”,比掩膜存儲器高級點,出廠時可以燒寫一次,但如果燒錯了,只好作廢換下一個。

EEPROM(E2PROM):為了重復利用,這代產品首先研究了第一代通過紫外線擦除的EPROM產品。這代產品是將電荷通過浮柵雪崩注入MOS管(FAMOS)、或者疊柵雪崩注入MOS管(SIMOS),通過雪崩效應編程。這種產品擦出復雜,而且擦寫速度很慢。

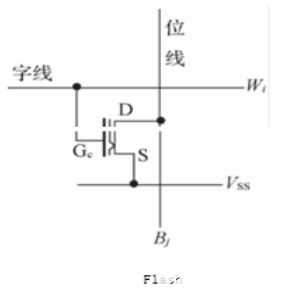

后來經過改良升級,改采用浮柵隧道氧化層MOS管注入,取名“EEPROM”,也稱作“E2PROM”。為了提高擦寫可靠性,并保護隧道氧化層,EEPROM還會再加一個選通管。程序讀寫時,主要通過字線和位線施加脈沖來實現操作。

圖3 掩膜存儲器、反熔絲存儲器、EEPROM一覽

快閃存儲器(Flash Memory)

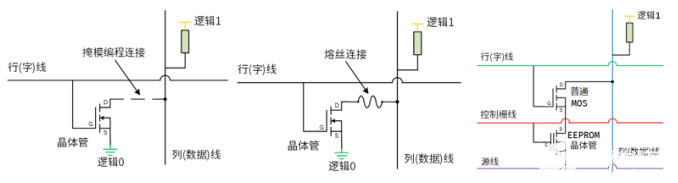

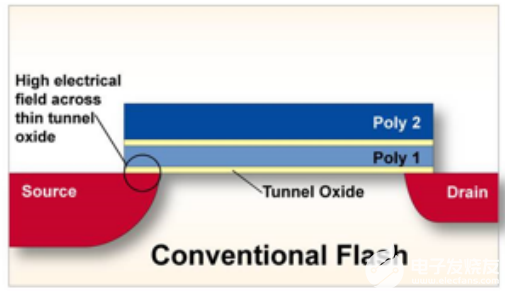

快閃存儲器Flash是在EPROM和EEPROM的基礎上做了一些改進,它采用一種類似于EPROM的單管疊柵結構的存儲單元,只用一個單管來實現。

圖4 Flash存儲器單元結構

快閃存儲器Flash的結構與EPROM的SIMOS管類似,主要差異為浮柵與襯底氧化層的厚度不同,下圖是一個Flash的疊柵MOS管結構。

圖5 普通Flash的疊柵MOS管結構

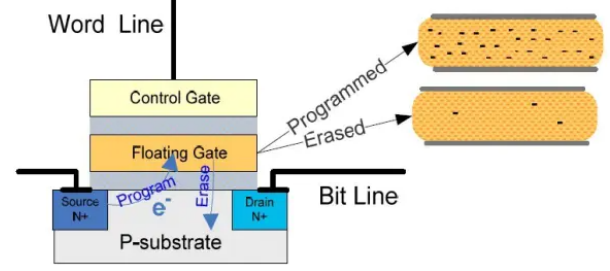

快閃存儲器究竟是怎么保存數據的呢?Flash擦寫是通過改變浮柵上的電荷來實現的。寫入時,漏極經過位線接正壓,并將襯底接地,在字線上加脈沖高壓(18~20V),源級和漏極之間會發生雪崩擊穿,部分電子會穿過氧化層到達浮柵,形成浮柵充電電荷。

擦除即是將電子從浮柵移出來實現。擦除時,將字線接地,同時,在P阱和N襯底上偏置一個正的脈沖高電壓(約20V)。這時,浮柵上面的電荷又會通過隧道效應被移出。

讀取Flash時,一般在字線加正常邏輯電平(一般3.3V或者5V),源級接地,當浮柵上存在電荷時,MOS管截止,輸出1狀態信號。反之,浮柵上沒有電荷,MOS管導通,輸出0狀態信號。

圖6 Flash單元擦寫示例

Flash過擦除(Over Erase)

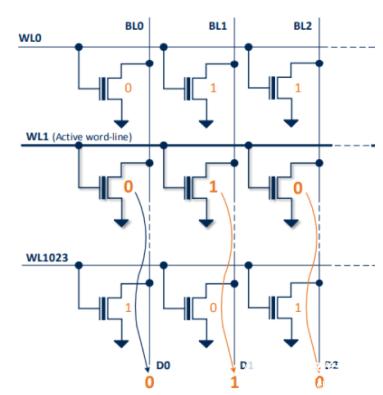

快閃存儲器的本質是存儲陣列,通過對浮柵上的電荷與字線邏輯電平作比較來判斷的。以Nor Flash為例。按照正常的工作方法,字線工作,會加正常邏輯(3.3V或5V);字線不工作,通常是懸空或者輸入0V電平。

正常情況,當字線不工作時,無正常邏輯(3.3V或5V)施壓到柵極,不論浮柵上有無電荷,MOS管都要求截止。

如果Flash出現過擦除,這時,浮柵上會表現為高壓,輸出電壓值不確定。如果電壓值剛好能使該單元的MOS管導通,此時,無論選擇哪個字線,該位線的讀值都是0V,從而影響其他單元的讀寫,這被稱為“單元泄露”。因此,為了讓Flash避免過擦除,對擦除的時候會非常小心,從而讓擦除時間變長。

圖7 Nor Flash操作示意圖

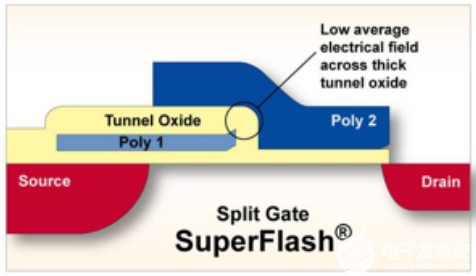

超級快閃存儲器(SuperFlash?)

前面提到,快閃存儲器的功能很強大,但擦除速度太慢。針對這一問題,Wolfe Yu介紹了世健代理的Microchip旗下SST發明的一種全新超級快閃存儲SuperFlash?技術。

圖8 SuperFlash?閃存的疊柵MOS管結構

在SuperFlash閃存中,控制柵被分成兩部分,只覆蓋一部分浮柵,它可以直接控制流入漏極的電流。

過度擦除留下的正電荷會產生單元泄漏路徑,導致閃存無法正確讀取數據。對于SuperFlash閃存來說,由于控制柵直接管理漏極邊緣,過度擦除無法使浮柵的泄漏路徑的達到漏極。所以,SuperFlash閃存不會考慮過度擦除問題,相對來說,擦除時間就會短很多。

隨機存儲器(RAM)

隨機存儲器,可以隨時隨地讀寫數據,讀寫方便,操作靈活。但是,RAM存在數據易失性的缺點。RAM主要分為動態隨機存儲器DRAM和靜態存儲器SRAM兩大類。

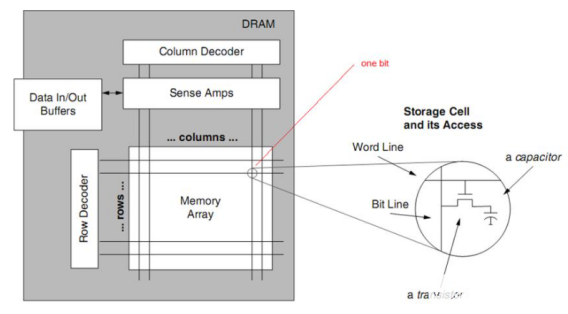

動態隨機存儲器(DRAM)一覽

動態隨機存取存儲器(Dynamic Random Access Memory,DRAM)是一種半導體存儲器,主要的作用原理是利用電容內存儲電荷來代表一個二進制比特(bit)。由于在現實中晶體管會有漏電電流的現象,導致電容上所存儲的電荷數量無法判別數據,從而造成數據毀損,因此DRAM需要周期性地充電。由于這種定時刷新的特性,因此被稱為“動態”存儲器。

圖9 DRAM結構示意圖

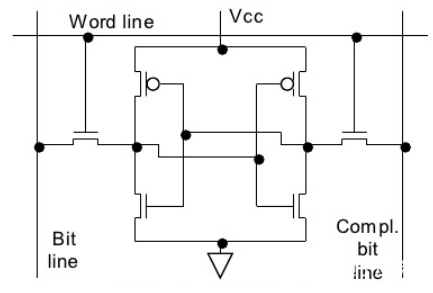

靜態隨機存儲器(SRAM)

靜態隨機存取存儲器(Static Random Access Memory,SRAM)是在靜態觸發器的基礎上構成,靠觸發器的自保功能存儲數據。

SRAM的存儲單元用六只N溝道MOS管組成,其中四個MOS管組成基本RS觸發器,用于記憶二進制代碼;另外兩個做門控開關,控制觸發器和位線。

圖10 SRAM結構示意圖

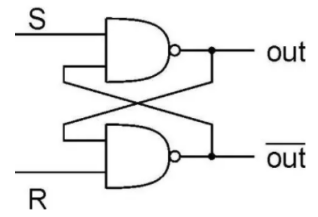

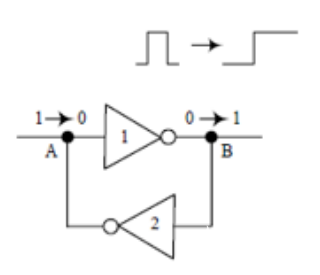

RS觸發器,是最常見的基本數字鎖存單元, FPGA的LUT的主要組成部分,結構簡單,操作靈活,RS觸發器有一個致命的缺陷,容易產生競爭冒險。

圖11 SRAM構造RS觸發器數字邏輯示意圖

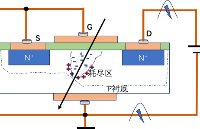

SRAM的單粒子翻轉事件(SEU)

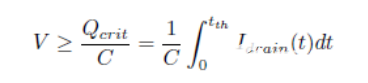

RS觸發器有著非常好的鎖存性能,但也有一個設計缺陷。在實際應用中,特別是在空間環境存在輻射的一些場景,會出現帶電粒子穿過P管漏區有源區。此時,在粒子徑跡上電離產生大量電子空穴對,形成“瞬態電流”。

圖12 單粒子翻轉事件充電原理

當上管出現一次電離輻射,通過建模,可以大致算出輸出電壓脈沖和累積電荷、以及存儲電容存在一定關系。

假設,如果前級輸入是邏輯1,輸出是邏輯0,存儲單元電容為100fF,只要累積電荷達到0.65pC-0.7pC時,輸出電壓脈沖幅值》0.7V,就很容易判斷為輸出為高電平。在輸出端電壓脈沖恢復到零電平之前,通過反饋,將邏輯0寫入輸入,從而造成輸出端電壓固定在高電平,變成邏輯1,出現粒子翻轉效應。這也是我們常說的數字電路的競爭冒險現象。

圖13 RS觸發器引起競爭冒險現象

單粒子翻轉影響及加固

單粒子翻轉會造成存儲數據的改寫,特別是行業多數FPGA芯片,大多是基于SRAM型的產品。一旦工作在惡劣環境下,極有可能引發產品工作異常,最終導致整個系統失靈。

一般來說,通過三模冗余、時間冗余和錯誤檢測與糾正等電路結構設計加固方法,可對其進行改善。

不過最好的解決方法是采用Flash型FPGA。由于Flash型FPGA和基于鎖存器原理的SRAM FPGA的存儲原理完全不同,所以很難發生通過簡單的電離輻射改寫邏輯單元的情況,從而提高了可靠性。同時,Flash技術的產品的功耗也比SRAM的功耗低很多。

目前,基于Flash工藝的FPGA主要是Microchip。它擁有基于反熔絲和Flash技術的FPGA,目前市場上主流產品是第三代SmartFusion? ProASIC?3/IGLOO?、第四代SmartFusion? 2/IGLOO2和第五代PolarFire/PolarFire SoC系列。

其他存儲器(FRAM&EERAM)

相對于傳統的主流半導體存儲器,非易失性只讀存儲器(ROM)和易失性隨機存儲器(RAM),還有一些速度較快,而且非易失性存儲器,比如鐵電存儲器(FRAM)、和非易失性隨機存儲器(EERAM)。

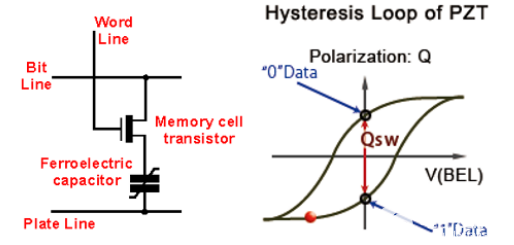

鐵電存儲器(FRAM)

上文有提到,EEPROM是通過電荷泵對浮柵操作來做數據存儲,浮柵的擦寫需要時間,還會破壞浮柵單元,存在次數限制。鐵電存儲器(FRAM)是采用一種特殊工藝的非易失性的存儲器,是采用人工合成的鉛鋯鈦(PZT) 材料形成存儲器結晶體。

當一個電場被加到鐵電晶體時,中心原子順著電場的方向在晶體里移動。當原子移動時,它通過一個能量壁壘,從而引起電荷擊穿。內部電路感應到電荷擊穿并設置存儲器。移去電場后,中心原子保持不動,存儲器的狀態也得以保存。鐵電存儲器不需要定時更新,掉電后數據能夠繼續保存,速度快而且不容易寫壞。

鐵電存儲器是個好東西,不過有一個致命的弱點,貴。用在低成本的工業和消費場合性價比不高。

圖14 鐵電存儲器原理

非易失性隨機存儲器存儲器(EERAM)

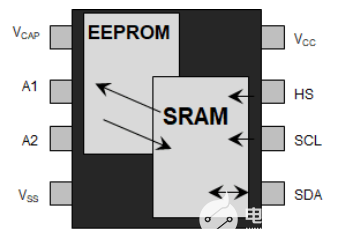

除了上文提到的FRAM,還有一種新型非易失性隨機存儲器(EERAM),這個產品是Microchip的獨家秘籍。

圖15 非易失性隨機存儲器架構

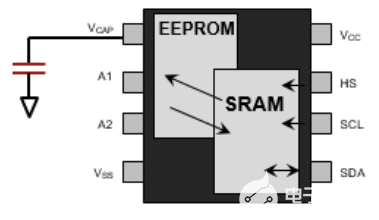

EERAM的工作原理非常簡單,靈感來源于采用后備電池供電的SRAM,它的本質就是不需要外部電池,而是通過一個很小的外部電容器,SRAM和EEPROM之間通過IC監測共集極的電壓,一旦電源電壓較低,就通過電容供電,把SRAM的數據搬到EEPROM里面,防止信號丟失。

對于需要不斷更新的存儲數據,EERAM采用了一種特殊的工作方式,在監測到供電電壓異常的時候,通過Vcap作為備用電源,把數據從SRAM轉移到EEPROM,自動完成數據的安全轉存。

當供電重新恢復正常,EEPROM的數據又自動導出到SRAM。而且,你也可以手動刷新數據到EEPROM。

圖16 非易失性隨機存儲器用電容為SRAM轉移數據提供電源

EERAM的優勢包括:自動通過斷電可靠地保存數據、無限次寫入數據、 低成本方案和 接近零時間的間隔寫入。這個器件性能較高,而且價格也沒有鐵電那么昂貴,非常適合防數據丟失,成本敏感的客戶。

圖17 非易失性隨機存儲器工作原理

Microchip基于先進存儲技術一攬子解決方案

隨著5G通信等市場的快速爆發,越來越多的定制產品層出不窮。由于存儲器大多都要暴露在十分苛刻的環境中,市場對萬能芯片FPGA的需求越來越大。Excepoint世健擁有專業的技術團隊,其代理的Microchip 的FLASH型FPGA能有效抵抗輻射從而提高系統的可靠性,快速的SuperFlash和創新的EERAM技術的存儲器等解決方案也都非常有特色,能幫助客戶降低存儲成本,為客戶的系統設計需求提供更多選擇。

-

半導體

+關注

關注

334文章

27290瀏覽量

218090 -

存儲器

+關注

關注

38文章

7484瀏覽量

163765 -

主控芯片

+關注

關注

2文章

198瀏覽量

24636

發布評論請先 登錄

相關推薦

SSD主控芯片格局已定?一家國內企業躋身全球第二,主控江湖劍指PCIe5.0

軟錯誤防護技術在車規MCU中應用

顯示器主控芯片和電視主控芯片的區別

機器人主控器的主控芯片在功能上與什么相似

科普 | 一文了解FPGA

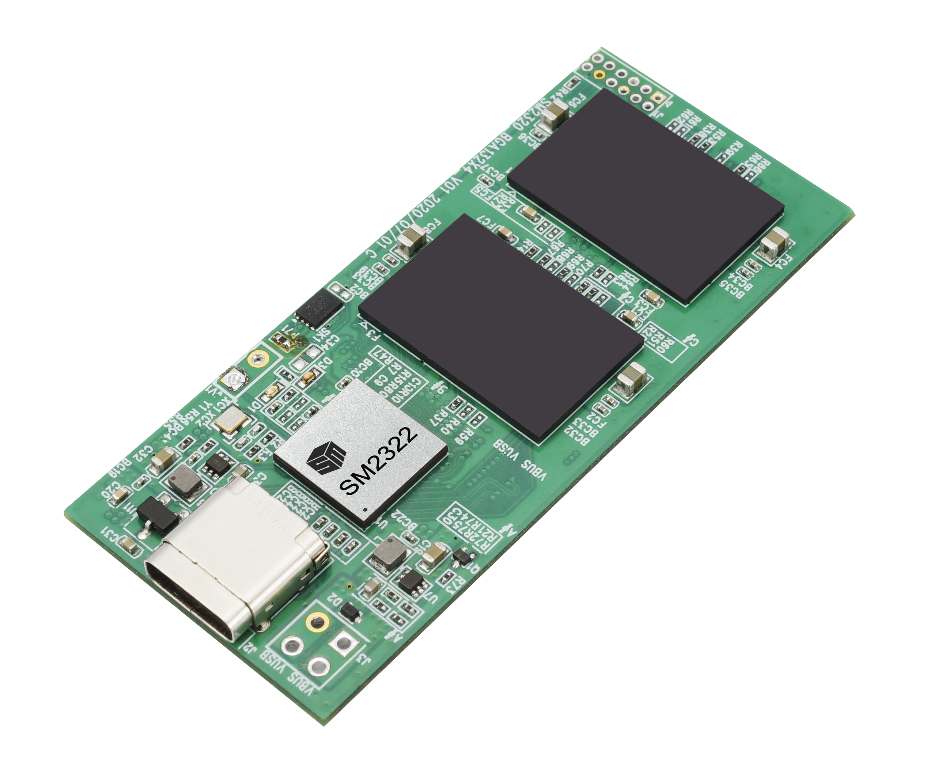

AI及游戲設備的理想選擇,慧榮科技推出新一代PSSD單芯片主控SM2322

得一微電子:AI時代重新定義存儲主控芯片

主控芯片CPU/FPGA存儲及單粒子翻轉科普

主控芯片CPU/FPGA存儲及單粒子翻轉科普

評論