編者按:模數轉換器 (ADC) 將模擬世界連接到數字世界,因此是連接到現實世界的任何電子系統的基本部件。它們也是決定系統性能的關鍵因素。本系列文章探討 ADC 的基礎知識、各種 ADC 類型及其應用。本文為本系列關于模擬基礎知識文章的第 1 部分,將討論逐次逼近寄存器 (SAR) ADC。第 2 部分將討論三角積分 (Δ?) 轉換器。第 3 部分將探討流水線 ADC。第 4 部分 將說明三角積分 ADC 如何能夠產生超低噪音結果。第 5 部分 探討 SAR ADC 的輸入驅動難題。

現在仍然是一個模擬世界,因此要讓感知的信息進入數字領域,需要進行某種轉換。這一重任就由模數轉換器 (ADC) 來完成。多年來,成功崛起的三種 ADC 拓撲結構是逐次逼近寄存器 (SAR)、三角積分 (S-D) 和流水線 ADC。這三種 ADC 拓撲結構截然不同,以便在不同的頻率范圍內工作,服務于從低頻傳感器應用到更高頻率的 LiDAR 或衛星通信等所有領域。

SAR ADC 是第一種成為主流的轉換器。隨著時間的推移,這種轉換器拓撲結構出現在各種應用中,包括過程控制、醫療和早期數字音頻系統。這些應用受益于 SAR ADC 的 8 位至 20 位輸出轉換范圍。但是,SAR ADC 賴以成名的原因是它會捕獲模擬輸入信號的快照,并使用多個信號快照來繪制一段時間內的圖像。

本文將簡要介紹與 SAR ADC 密切相關的信號鏈。接下來,通過分析負責 ADC 快照操作的基本輸入級,深入研究該 ADC 拓撲結構。然后,本文將介紹 SAR ADC 示例解決方案——Analog Devices 的 AD7625BCPZ 和 AD4020BCPZ-RL7,著重討論 ADC4020BCPZ-RL7 的內部模數轉換機制。另外,還提供了合適數據采集系統的關鍵規格。

SAR ADC 的模擬信號鏈

SAR ADC 常用于自動測試設備、機器自動化、醫療設備和精密數據采集等系統中。在所有 SAR ADC 應用中,都存在一個需要適度 8 至 20 位分辨率數字表示的模擬信號,并且采樣速率從接近 DC 到每秒 15 兆 (MSPS)(在撰寫本文時)。

SAR ADC 能力強大,無需模擬前端 (AFE) 信號鏈即可工作。但是,如果設計人員的工作還包括在 SAR ADC 的前端成功呈現信號,則很有可能需要一定程度的信號調節(圖 1)。

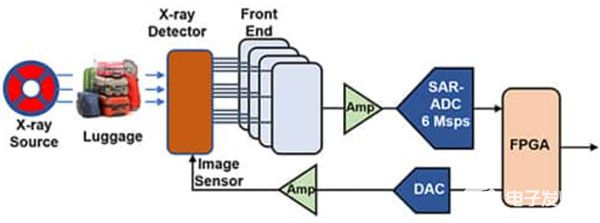

圖 1:該示例 SAR ADC 信號鏈包括 X 射線探測器、AFE、放大器驅動器、Analog Device 的 AD7625BCPZ 6 MSPS 轉換器,以及用于獲得轉換結果的數字接收器 (FPGA)。(圖片來源:Digi-Key Electronics)

在圖中,X 射線源經行李箱將信號發送到 x 射線探測器。X 射線設備的工作是在短時間內構建行李箱的完整圖像,以減少旅客的不滿。

前端獲取探測器信號并執行信號調節功能,例如模擬增益和電平位移。然后信號被提供給 SAR ADC,在本例中為 Analog Devices 的 AD7625BCPZ。

SAR ADC 之前的放大器提供適當的穩定功能,在放大器與 SAR ADC 之間通常有一個一階低通濾波器。該 SAR ADC 能夠以高達 6 MSPS 的速度采樣(每 167 納秒 [ns] 采樣一次),可以在短時間內獲得多個快照。

SAR ADC 輸入級的核心已簡化

隨著時間的推移,SAR ADC 經歷了許多增強和改進,但在所有情況下,轉換期間的主要活動都是電荷再分配,這是逐次逼近 ADC 最常見的實現形式之一。此外,與 S-D 和流水線轉換器不同,SAR ADC 還具有零延遲優勢。

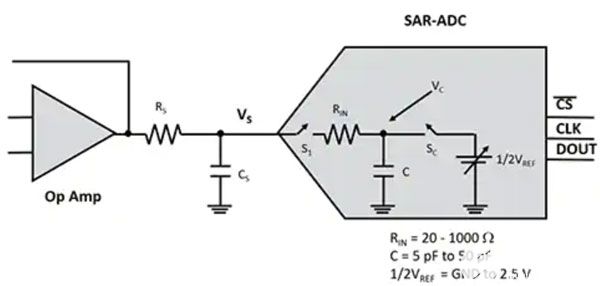

在最簡單的層面上,很容易看到信號快照發生的位置。SAR ADC 輸入核心包含輸入信號采集開關 (S1)、電容陣列、轉換開關 (SC) 和內部基準電壓 (? VREF)(圖 2)。

圖 2:驅動 SAR ADC 的運算放大器 (op amp),帶有輸出穩定濾波器。(圖片來源:Digi-Key Electronics)

SAR ADC 核心的工作方式如下:

1、S1 打開,SC 關閉:斷開輸入級與模擬信號源的連接。

2、C 上的電荷通過 ? VREF 重新校準。這種重新校準使 SAR ADC 清零。

3、然后,S1 關閉,SC 打開:現在,該設備已連接到輸入模擬信號。

4、SAR ADC 在預定的采集時間內采集輸入信號 VS。此采集時間可產生 S1 和 SC 開關噪聲,以及放大器突然暴露于電容加載和開關噪聲。

5、然后,S1 打開:這是發生信號快照的確切實例。

6、SAR ADC 將 VC 處的信號轉換為數字表示。執行此操作花費的時間就是“轉換時間”。

SAR ADC 輸入級的核心詳細信息

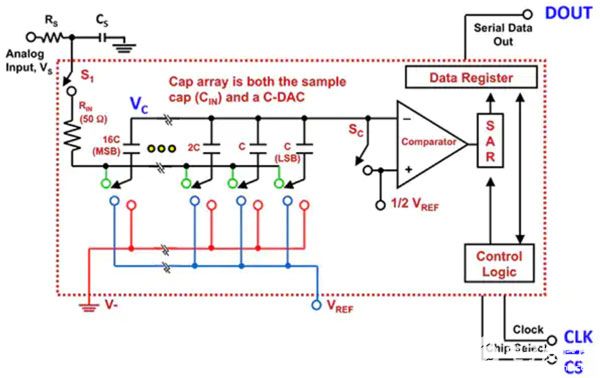

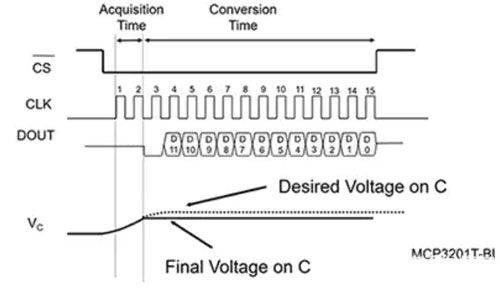

轉換核心可對在 VC 處所采集信號進行電荷再分配。轉換器電荷再分配的協調發生在核心中,由時鐘進行門控。通過此過程,每個時鐘控制的數字輸出代碼會到達 SAR ADC 的 DOUT 輸出(圖 3)。

圖 3:4 位 SAR ADC 光幕具有完整的數字加權電容陣列:16C、8C、4C、2C 和兩個 C。(圖片來源:Digi-Key Electronics)

在轉換過程中,SAR ADC 算法首先會確定最高有效位 (MSB)。SAR ADC 通過在 V- 和 VREF 比較器輸入之間切換 16C 電容器的底部,開始測試與 ? VREF 相比的信號幅度。在 SAR ADC 轉換線中,下一個比較是針對 ? VREF 測試 8C(未顯示),然后是 4C 測試,等等。

SAR ADC 輸出轉換詳細信息

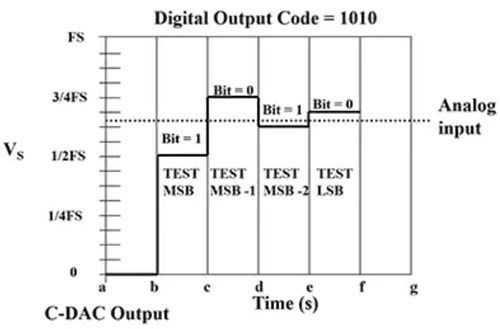

MSB 決策會立即通過 DOUT 引腳發送,而在進行 MSB 1 決策時,MSB 開關會保持凍結狀態。SAR ADC 會一直執行此算法,直到最終選擇最低有效位 (LSB)(圖 4)。

圖 4:4 位 SAR ADC 通過位決策對轉換算法進行時鐘控制,并通過 DOUT 引腳發送這些決策(如圖 3 所示)。(圖片來源:Digi-Key Electronics)

在圖 4 中,SAR ADC 時鐘控制的位決策順序是從 MSB 一直到 LSB。所有轉換數據在時鐘控制下繼續通過圖 3 右上角的 DOUT 立即輸出。完整的吞吐時間通常需要足夠的時間來采集信號,并且每個位需要一個時鐘周期。

SAR ADC 轉換挑戰

設計人員必須了解信號的建立時間量,以確保從轉換中捕獲正確的模擬值(圖 5)。

圖 5:12 位 SAR DAC 的轉換時序示意圖。每次完整的轉換需要 16 個時鐘。(圖片來源:Digi-Key Electronics)

在圖 5 中,輸入信號 VC 在轉換器輸入開關打開之前未達到最終所需電壓。出現這種情況是因為電路設計人員錯誤地計算了放大器輸入信號的建立時間。

AD4020BCPZ-RL7 20 位 1.8 MSPS SAR ADC 通過延長采集相位的同時仍保持吞吐率,降低了信號采集的復雜性。它具有 100.5 dB 的低信噪比 (SNR)。

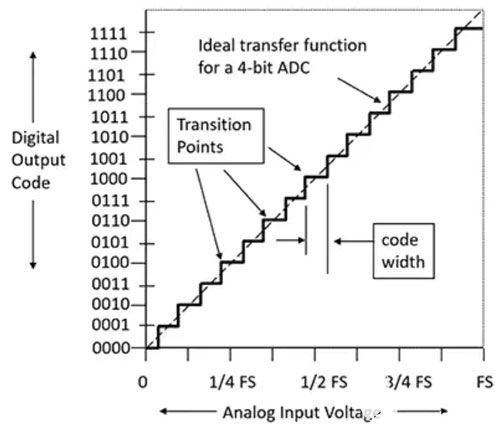

SAR AD 傳遞函數

ADC 的可能代碼數等于 2N,其中 N 是位數。例如,4 位轉換器具有 24 或 16 個單獨的可用代碼(圖 6)。

圖 6:理想 4 位 SAR AD 的傳遞函數或數字輸出代碼與模擬輸入電壓的關系圖,應為一條直線。(圖片來源:Digi-Key Electronics)

繪制圖像

SAR ADC 的吞吐率包括采集時間和轉換時間,以讓 Analog Devices 的 AD4020BCPZ-RL7 在 20 位分辨率下的吞吐率高達 1.8 MSPS。利用 AD4020BCPZ-RL7 吞吐速度,可以獲取多個快照并創建用于機器自動化和醫療設備的數字圖片渲染解決方案。

總結

從過程控制到醫療和消費類應用,SAR ADC 憑借獲取信號快照的能力及不斷提高的分辨率和速度,持續證明其價值。目前的 SAR ADC 具有 8 到 20 位的分辨率,吞吐率高達 15 MSPS。Analog Devices 的 AD4020BCPZ-RL 就是一個例子,其具有低噪聲、高速、20 位、1.8 MSPS 的精度。但是,SAR ADC 轉換器架構的發展還未結束。未來還會有更多產品。

-

運算放大器

+關注

關注

215文章

4929瀏覽量

172839 -

SAR

+關注

關注

3文章

416瀏覽量

45949 -

模數轉換器

+關注

關注

26文章

3200瀏覽量

126810

發布評論請先 登錄

相關推薦

ADS9110逐次逼近寄存器(SAR)模數轉換器(ADC)數據表

ADS9120逐次逼近寄存器(SAR)模數轉換器(ADC)數據表

ADS8862微功耗、微型、單端輸入、SAR模數轉換器數據表

逼近型模數轉換器特點和應用

模數轉換器的技術參數詳解

模數轉換器的工作原理、分類及應用

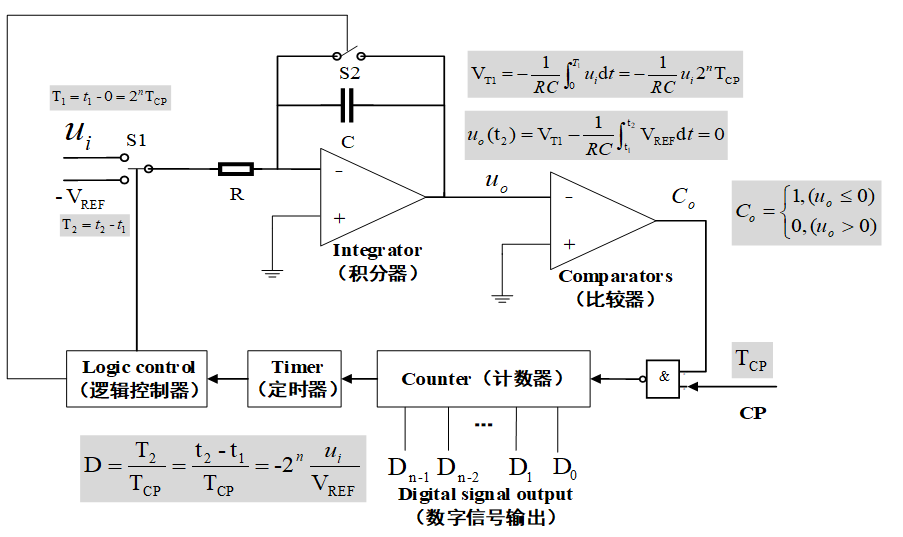

雙積分型模數轉換器結構及工作原理分析

模擬基礎知識:SAR模數轉換器

模擬基礎知識:SAR模數轉換器

評論