我們大多數人已經習慣于每天(如果不是每小時)與無處不在的技術生態系統進行交互。從健身追蹤器、智能吸塵器和半自動駕駛汽車到每天早上叫醒我們的智能家居設備,不可否認,物聯網(IoT) 熱潮已經擴散到我們生活的方方面面。在這一時刻的核心,觸手可及的連接是強大的云計算和機器學習技術,它們依靠物聯網通過有線和無線通道,通過互聯網或數據中心傳輸大量信息的能力而蓬勃發展。

許多具有上下文感知和響應能力的物聯網設備已經存在了相當長的一段時間,但近年來,相互通信和連接到云的實踐釋放了新的潛力。根據IDC的數據,2019 年聯網設備數量為 226 億臺,預計到 2025 年將增長到 750 億臺——考慮到屆時預計 180 澤字節的數據消耗,這是可預見的軌跡。

隨著消費者期望物聯網設備變得越來越緊湊和即時響應,片上系統 (SoC) 設計工程師通常需要在連接性、安全性、個性化和傳感器處理等功能之間做出艱難的選擇,以換取可接受的電池壽命。

全面的 IP 解決方案和持續的創新周期來開發能夠處理高效數據處理、在超小型尺寸中茁壯成長并支持多種無線連接標準的芯片,對于團隊將低功耗洞察力融入他們的設計至關重要。如今,設計團隊正在探索過去設計中預留的幾個選項,以盡可能提高設計的功率效率和性能。也就是說,我們才剛剛開始了解每種此類技術的潛力。

繼續閱讀以了解更多關于低功耗設計的需求、要考慮的關鍵設計技術、擴展物聯網應用的挑戰和機遇,以及為什么普遍連接將推動下一代物聯網設計。

為互聯世界而設計

物聯網的美妙之處在于,它使設備能夠在不受設備位置影響的情況下交換數據,并以以前無法想象的方式進行控制。過去,物理接近是插入式機械或電氣設備功能協作的關鍵先決條件。這種依賴于距離的連接限制了可以控制設備的位置和方式的范圍。今天,具有先進通信能力的微處理器已經創建了更大的物聯網系統,并用大量“邊緣設備”取代了剛性物理系統的障礙。

傳統上,物聯網設計團隊的唯一目標是降低成本而不是功耗。雖然降低功耗一直很重要,但當面臨降低成本作為壓倒一切的優先事項時,設計人員將被迫繞過降低功耗技術以滿足預算要求。另一方面,當今垂直排列的系統公司將降低功耗視為對總擁有成本的好處。對他們來說,隨著時間的推移,能源消耗遠遠超過單位芯片成本,因此他們優先考慮低功耗,并利用其與高性能和高效處理的結合,而不僅僅是降低硅成本——徹底改變了功耗游戲。總之,低功耗、延長電池壽命、

人工智能 (AI) 等智能技術的進步使團隊能夠縮小特定任務的范圍并優化每一瓦的功率。

將需要多種人工智能算法和額外的靈活性來處理來自新興市場的需求。這將使系統工程師能夠更深入地了解芯片如何針對功率進行優化,并將權衡平衡從終極靈活性和難以置信的低成本轉向靈活性和低功耗。

對低功耗設計的需求

世界各地的公司都在推動便攜式、手持式和電池供電小工具的更多特性和功能。通過降低功耗來延長電池壽命是此類產品的關鍵差異化因素,對其最終應用至關重要。

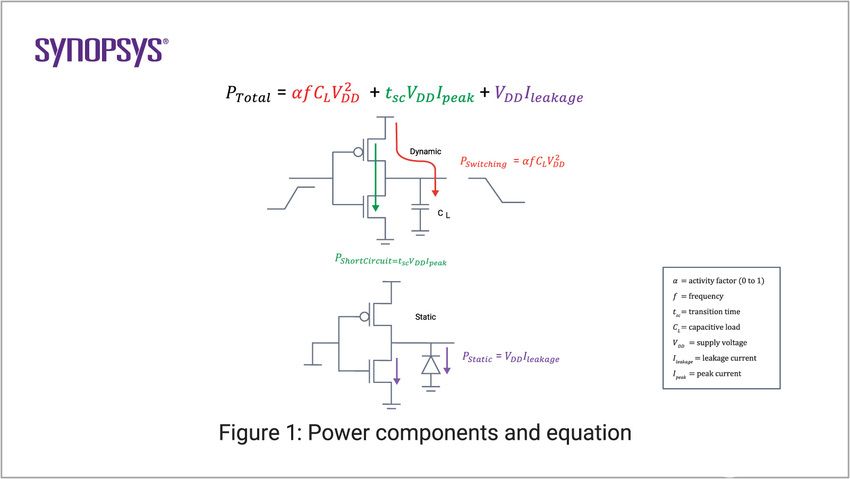

從本質上講,低功耗設計的目標是盡可能減少動態和靜態組件的功耗。開關和短路功率構成動態功率,而靜態功率由在沒有信號活動時流過電路的泄漏電流組成。這些功率組件中的每一個的值都與頻率、峰值電流、電壓、轉換時間、泄漏電流、容性負載和開關活動等因素直接相關。

電壓值越高,每個組件消耗的功率就越多。為了在消耗最少功率的同時獲得所需的性能,通過各種低功耗技術和方法來測試這些因素中的每一個的權衡,以滿足激進的市場需求。

在決定插入式物聯網設備是否需要復雜的冷卻系統或散熱器時,提高設備從關閉/睡眠狀態轉換為開啟/活動狀態所需的時間成為一個關鍵參數,從而增加了電力成本。例如,升級使用并行系統的服務器群中的 IC 可以顯著節省電力和成本,因為使用的單個芯片對系統有重大影響。

過去,采購團隊的主要目標是找到降低芯片成本和整合連接性的最佳方法——由于支持這些類型的需求需要額外的內存和外圍設備,因此成功實現這兩個參數是一項艱巨的任務.

隨著人工智能的普及,我們預計更多特定于應用程序的任務將為 SoC 設計團隊提供優化特定設計功能和組件的機會。與智能手機市場不同,這些設計必須對多種應用具有吸引力,以確保數量足以證明設計投資的合理性,從而降低成本。

關鍵的低功耗設計技術

物聯網邊緣設備內部的底層芯片從根本上執行三個關鍵功能:傳感、處理和通信。引起業界對低功耗設計重新燃起興趣的原因是市場對物聯網設備具有高性能、長電池壽命和移動性的需求不斷增長。

在針對低功耗進行設計時,可以采用多種技術:

- 時鐘門控:在邏輯綜合期間執行,其中具有“啟用”輸入的觸發器被優化為時鐘門控結構。這種技術通過減少對多個多路復用器的需求來節省大量面積,并通過減少整體開關活動來最小化動態功耗。

- 多電壓域:通過這種技術,芯片的功能根據性能特征分為不同的電壓域塊。然后,底層設計會考慮芯片的哪個區域需要更高的電壓才能運行,而不是整個區域都被歸類為高性能。這有助于降低動態和靜態功耗。

- 電源門控:與芯片/系統級的多電壓方法類似,IC 內的功能根據其電源域分為塊。電源門控有效地完全關閉了一個模塊的電源,從而實現了靜態和動態節能。

- 寄存器保留:這種方法通常與電源門控技術結合使用。當塊關閉時,塊中的觸發器子集或所有觸發器都保存其先前的值,然后在打開時恢復。這通過縮短恢復模塊原始狀態所需的時間和步驟以及改善整體加速時間來節省電力。

除了上述方法并結合使用它們之外,還有許多更先進的技術,例如工藝節點選擇、選擇定制處理器以獲得更高效的功能、良好的偏置、零引腳保持觸發器、耦合系統的不同部分、動態電壓和頻率縮放 (DVFS),以及自適應電壓和頻率縮放 (AVFS)。例如,許多現代處理器具有使用較低電壓和電源門控的模塊,并具有隔離、保持和電平轉換器。

最新的無線連接解決方??案

今天,系統設計人員有許多無線連接協議可供選擇,每種協議都針對不同的應用提供獨特的優勢。

有些基于低吞吐量無線技術(如低功耗藍牙)的技術因其降低功耗和成本的附加功能而需求增加,同時保持與經典藍牙版本相似的范圍。

Zigbee 和 Thread 等基于 IEEE 802.15.4 的協議在短距離內提供低數據速率連接,并且與其他專有協議一起顯然正在獲得動力。雖然不同的標準可能提供不同的管理標準和功能,包括安全性、定位服務和音頻,但從根本上說,它們都支持對更大帶寬和更多設備連接到互聯網的日益增長的需求。幾乎所有最新的 SoC 設計都在以創紀錄的速度采用更新的無線標準,例如在擁擠區域提供更快速度和更好性能的 Wi-Fi 6。

隨著 Wi-Fi 6E 和 Wi-Fi 7 的未來承諾,在與以前不同的更高速度和帶寬下,創新和采用的空間很大,從而對低功耗提出了新的要求。

使用高質量 IP 加速物聯網 SoC 設計成功

客戶可以通過多種選擇來評估最大化吞吐量的方法,從而使設計團隊能夠在功耗、面積、成本或性能之間進行權衡。從處理器、編譯器、RAM、基礎 IP 到接口 IP,所有東西都具有斷電功能和不同的權衡,需要根據最終應用加以考慮。

多年來,Synopsys 一直走在通過Synopsys DesignWare? IP提供全面 IP 解決方案的最前沿,使 SoC 團隊能夠更快地滿足物聯網設計的要求,并顯著降低風險。該產品組合包括經過硅驗證的有線和無線接口 IP、數據轉換器、安全 IP、低功耗嵌入式存儲器和邏輯庫、節能處理器內核和集成 IP 子系統。

我們在 IP 質量和全面技術支持方面的廣泛投資也拓寬了我們的整體客戶市場,讓更多客戶能夠采用最適合他們需求的工具。基于最新的配置和行業標準,我們繼續支持行業對 PCIe、USB 和 DDR 等高速協議的需求,同時也為高級物聯網 SoC 設計提供最高級別的安全性。

概括

隨著我們目睹物聯網技術的更多進步和便攜式設備的擴展功能,5G 網絡的日益部署以及對人工智能和自動化的興趣將需要團隊投資于改進的 SoC 設計技術、設計優化和定制工具。

無處不在的連接顯然將推動物聯網設計路線圖,并對尋找有效方法來提高世界各地城市的運營效率、能源使用和整體生活質量產生更大的影響。通過繼續優先考慮物聯網應用的低功耗設計和延長電池壽命,擔心每天為智能設備充電可能已成為過去。

審核編輯:符乾江

-

物聯網

+關注

關注

2909文章

44557瀏覽量

372790 -

人工智能

+關注

關注

1791文章

47183瀏覽量

238264 -

低功耗設計

+關注

關注

0文章

80瀏覽量

16157

發布評論請先 登錄

相關推薦

加速物聯網設計:萬物智能時代的低功耗設計

加速物聯網設計:萬物智能時代的低功耗設計

評論