自從1989年國際整流器公司(IR)率先推出首款單片式高壓驅動產品以來,高壓集成電路(HVIC)技術就開始利用獲得專利的單片式結構,集成雙極器件、CMOS及橫向DMOS器件,設計出了擊穿電壓分別高于700V和1400V的產品;這些高壓驅動芯片可以工作在600V和1200V偏置電壓下。

2016年英飛凌完全收購IR后,英飛凌擁有了這項經過多年市場驗證的PN結隔離(JI)技術,該技術是一項成熟的、可靠的且經過市場驗證的技術。特有的HVIC和抗閂鎖CMOS技術可打造出可靠的單片式構造。先進的制造工藝生產出性價比最佳的產品,可面向電機控制,開關電源等多種應用。

英飛凌PN結隔離(JI)技術的主要益處:

? 最大驅動電流可達4A

? 精密模擬電路(嚴格的時序/傳輸延遲)

? 擁有行業內數量最多的標準級門極驅動產品

? 電壓等級:1200V、600V、500V、200V和100V

? 驅動結構類型:三相、半橋、單通道等

? 最佳性價比

PN結隔離(JI)技術介紹

一個完整的半橋驅動芯片包含了耐高壓的高邊驅動電路和低邊驅動電路,其中高邊驅動電路包含高壓電平轉換電路和高壓浮動驅動電路。PN結隔離技術(JI)通過多晶硅環形成的“井”型高壓浮動開關,將可“浮動”600V或1200V的高壓電路與其他低壓電路在同一硅片上隔離,從而通過對地的低壓數字信號直接驅動需要高壓浮動開關的功率器件IGBT和MOSFET。廣泛應用于各種常見電路拓撲中,包括降壓電路、同步升壓電路、半橋電路、全橋電路和三相全橋電路等等。

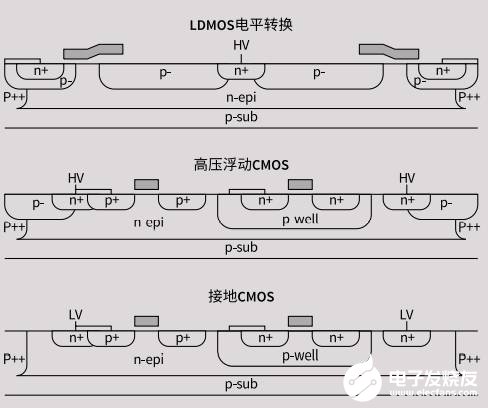

下圖分別是LDMOS電平轉換電路以及高低邊驅動CMOS的橫切面圖。

電平轉移式高壓驅動芯片的內部框圖和工作原理

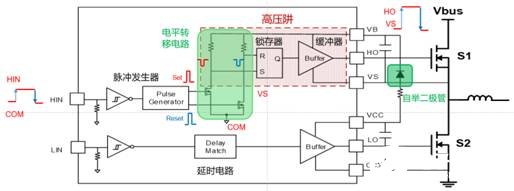

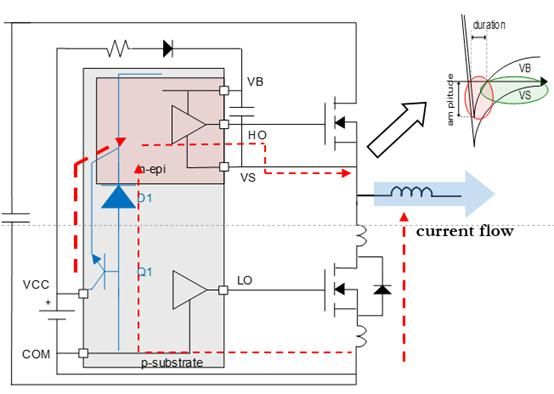

下圖是一個典型半橋驅動芯片的內部設計原理和結構。

這個半橋驅動芯片高邊HVIC包含了:

脈沖發生器:在輸入信號HIN的上升沿和下降沿產生脈沖信號;

? 電平轉移電路:把以COM為參考的信號轉換成以VS為參考的信號;

? SR鎖存器:鎖存從電平轉移電路傳輸過來的脈沖信號;

? 緩沖器:放大輸入信號

? 延時電路:補償高邊信號的傳輸延時;

? 自舉二極管:在S2開通時對自舉電容進行充電。通過電平轉換電路,使相對于地(COM)的Hin信號轉換成同步的相對對于懸浮地(VS)的Ho信號,從而控制高邊S1的開關。

VS負壓和閂鎖效應

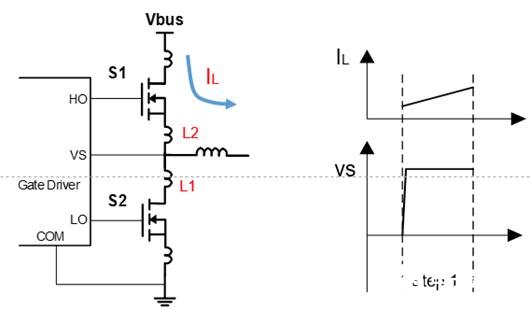

在半橋電路中,感性負載、寄生電感和下管反向續流可能在VS腳產生負壓。基于HVIC的構造,VS負壓可能導致HVIC失效。因此,如何抑制VS負壓,將是HVIC應用中的重要課題。

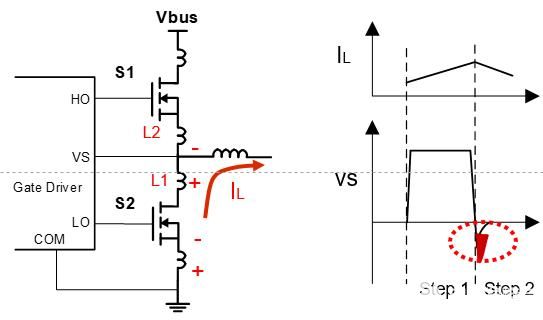

L1,L2分別是上下管上功率器件的封裝電感和電路走線的寄生電感,當上管開通時,電流經過上管流過負載電感;上管關斷換流時,續流電流經過S2的體二極管,并在L1L2寄生電感上產生電壓,導致VS端產生了低于地線電壓的負壓。該負電壓的大小正比于寄生電感的大小和開關器件的電流關斷速度di/dt;di/dt由柵極驅動電阻Rg和開關器件的輸入電容Ciss決定。

VS負壓除了使Vbs超過芯片的絕對最大額定值,導致芯片過壓損壞;更多的時候是產生閂鎖效應,導致不可預測的結果。

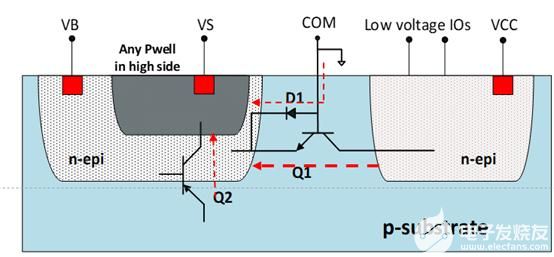

如上圖,驅動芯片外延層到襯底有一個等效二極管D1(VB-COM),外延層-襯底-外延層有一個等效NPN三極管Q1(VCC-COM-VB)。當VS產生負壓時,D1/Q1可能導通,會引起HO跳變(在沒有輸入信號時,HO可能從低電平跳到高電平),從而導致半橋功率管短路使系統失效,或者引起驅動芯片的內部CMOS結構發生閂鎖效應,從而導致驅動芯片失效。

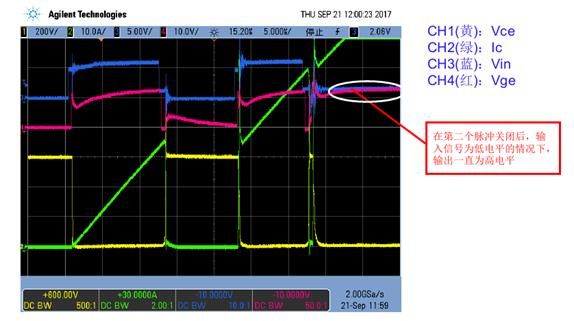

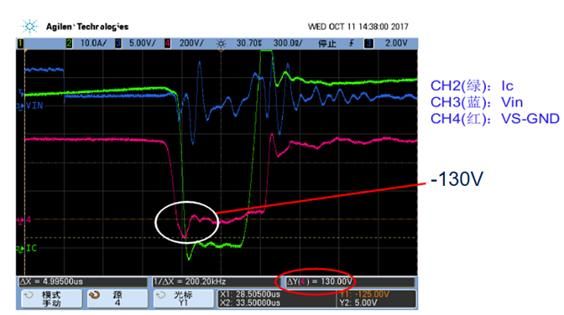

上兩圖是來自客戶的一個實測雙脈沖波形,驅動芯片的輸入信號是低電平,但是輸出跳變成高電平,在上管關斷的時候VS腳的瞬變電壓達到了-130V,這個負壓使得HO從低電平跳變成高電平。

JI技術驅動芯片周邊電路設計指導

為了減小-VS(VS=-(Lp*di/dt+Vf)),在電路設計中需要做到:

1.使寄生電感最小化,減小驅動回路的走線,避免交錯走線。

2.半橋電路兩個功率管盡可能靠近安裝,它們之間連接盡量用粗短線

3.驅動芯片盡量靠近功率管

5.使用低寄生電感的電阻作為電流檢測電阻,并盡量靠近下面的功率管

6.VB-VS之間使用低寄生電感的瓷片電容

7.VCC-COM之間也要使用低寄生電感的瓷片電容,推薦使用的VCC-COM之間的電容容量是VB-VS之間的電容容量的十倍以上

8.退耦電容盡量靠近驅動芯片引腳

如果注意了上述事項,VS腳負壓仍然很大的話,可以考慮降低功率管的開關速度,以便降低開關時的電流變化率di/dt,例如:

1.外加緩沖電路

2.增大驅動電阻(注意:這種方法會增加功率管開關損耗)

評估板

-

PN結

+關注

關注

8文章

482瀏覽量

48773 -

寄生電感

+關注

關注

1文章

156瀏覽量

14606 -

驅動芯片

+關注

關注

13文章

1290瀏覽量

54716

發布評論請先 登錄

相關推薦

基于PN結隔離(JI)技術的驅動芯片簡介及設計指導

基于PN結隔離(JI)技術的驅動芯片簡介及設計指導

評論