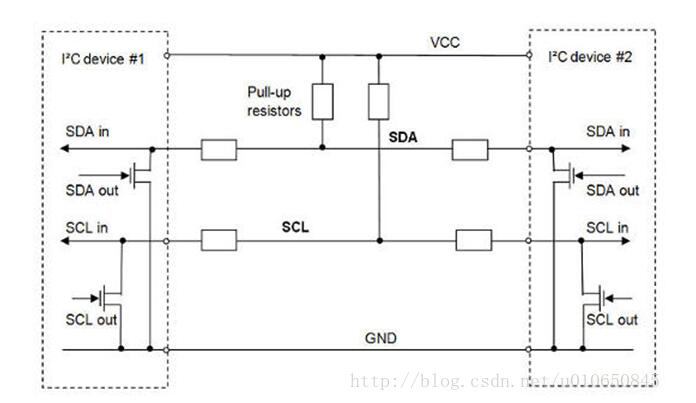

總線信號 :

SDA :串行數(shù)據(jù)線

SCL :串行時鐘

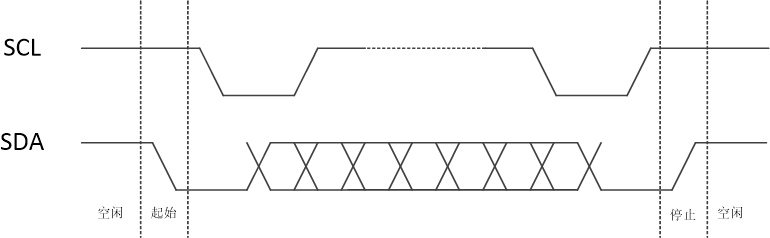

總線空閑狀態(tài) :

SDA :高電平

SCL :高電平

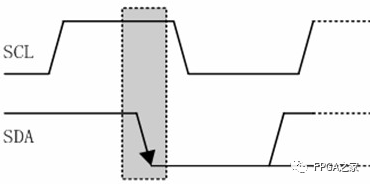

起始位:SCL為高電平期間 SDA出現(xiàn)下降沿

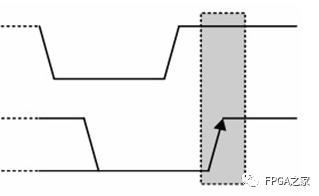

終止位:SCL為高電平期間 SDA出現(xiàn)上升沿

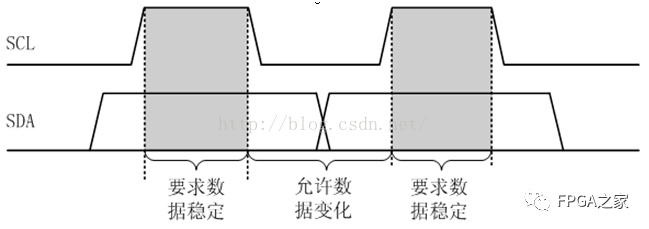

數(shù)據(jù)傳輸 :SDA的數(shù)據(jù)在SCL高電平期間被寫入從機。所以SDA的數(shù)據(jù)變化要發(fā)生在SCL低電平期間。

IIC時鐘頻率:不高于400K

應(yīng)答:當(dāng)IIC主機(不一定是發(fā)送端還是接受端)將8位數(shù)據(jù)或命令傳出后,會將SDA信號設(shè)置為輸入,等待從機應(yīng)答(等待SDA由高電平拉為低電平)

若從機正確應(yīng)答,表明數(shù)據(jù)或者命令傳輸成功,否則傳輸失敗,注意,應(yīng)答信號是數(shù)據(jù)接收方發(fā)送給數(shù)據(jù)發(fā)送方的。

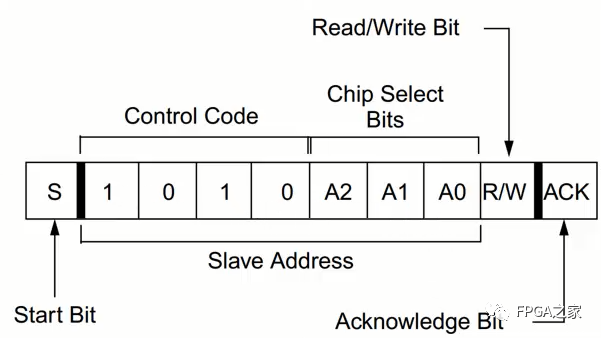

IIC器件地址:每一個IIC器件都有一個器件地址,有的器件地址在出廠時地址就設(shè)定好了,用戶不可以更改,比如OV7670的

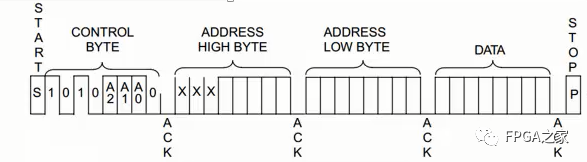

地址為0x42。有的器件例如EEPROM,前四個地址已經(jīng)確定為1010,后三個地址是由硬件鏈接確定的,所以一

個IIC總線最多能連8個EEPROM芯片。

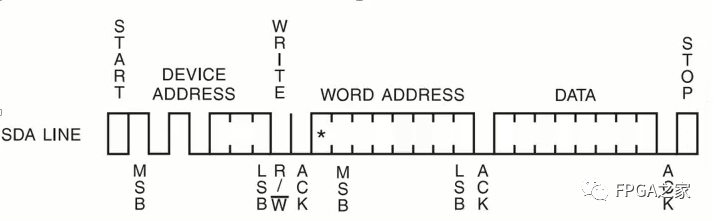

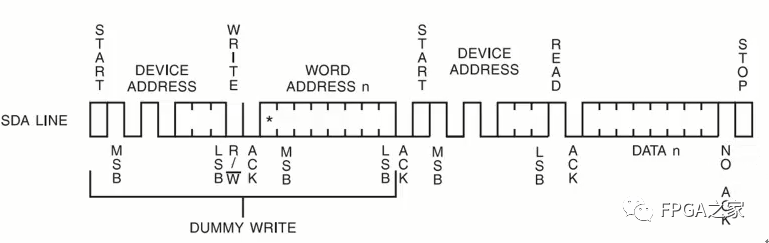

圖上開始信號之后,七位地址代表器件地址,第八位代表讀或者寫,0為寫,1代表讀,然后跟著響應(yīng)位。

IIC器件單字節(jié)寫時序:

IIC器件多字節(jié)地址寫時序:多字節(jié)地址比單字節(jié)地址在時序上就多了一塊寫地址

單字節(jié)器件讀時序:注意最后產(chǎn)生無應(yīng)答信號,另外多字節(jié)地址讀時序跟單字節(jié)類似,只不過是多了幾個地址字節(jié)而已。

三大串行總線:uart、spi、iic

同步:spi異步 :iic,uart

同步和異步區(qū)別:采集數(shù)據(jù)是否用的是時鐘的沿,如果是時鐘沿采數(shù)據(jù),同步傳輸,如果電平采集數(shù)據(jù)是異步

串口接受數(shù)據(jù)其實就是一個串轉(zhuǎn)并的過程

原文標(biāo)題:IIC協(xié)議

文章出處:【微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

審核編輯:湯梓紅

-

總線

+關(guān)注

關(guān)注

10文章

2878瀏覽量

88053 -

IIC

+關(guān)注

關(guān)注

11文章

300瀏覽量

38311 -

SCL

+關(guān)注

關(guān)注

1文章

239瀏覽量

17057

原文標(biāo)題:IIC協(xié)議

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

IIC總線協(xié)議時序介紹 IIC總線程序設(shè)計

IIC總線協(xié)議與SCCB協(xié)議的區(qū)別

IIC總線介紹

IIC協(xié)議總線特點簡介

基于FPGA來介紹并設(shè)計標(biāo)準(zhǔn)的SPI總線協(xié)議

IIC總線協(xié)議的相關(guān)資料下載

IIC總線協(xié)議及應(yīng)用

IIC總線協(xié)議介紹

IIC總線協(xié)議介紹

評論