2022年4月刊致辭

“ 在過去的一個月里,雖然疫情肆虐,但擋不住我們的技術團隊依然在通過線上的方式為用戶帶來各種最新的解決方案,領域涉及了3DIC先進封裝和高速測試等。我們的后勤保障團隊,在物資極度緊缺、物流幾乎停滯的情況下,也想盡辦法,給每位上海員工家庭都送上了急需的物資包。春暖花開,我們期待疫情盡快過去,期待和您再次相聚。”

芯和半導體創始人、高級副總裁

代文亮博士

新聞亮點

ESD(Electronic System Design)電子系統設計聯盟近日宣布,芯和半導體正式成為該聯盟的成員。ESD聯盟是SEMI旗下的一個代表電子系統和半導體設計生態系統成員的技術社區,是一個解決影響整個行業的技術、市場、經濟和法律問題的社區,是溝通和提升半導體設計生態系統作為全球電子行業重要組成部分的價值的中心。除了 ESD 聯盟的成員,芯和半導體同時也是 SEMI 的成員。SEMI 是代表了全球電子產品設計和制造供應鏈的全球性行業協會。

市場活動

如何從設計階段就考慮串擾的規避,將會是每位SI工程師都需要直面的問題;高效、充分的產品驗證是產品快速上市的一個保證。如何進行有效的產品開發階段的串擾驗證則是產品開發工程師需要思考的問題。芯和半導體的技術專家鄭拓受邀于3月25日參加安立通訊科技的第11期高速接口測試論壇線上講座,就高速數字產品設計與開發中串擾仿真和驗證進行分享和交流。

3DIC第一講:后摩爾時代異構集成的設計挑戰及EDA的新使命

芯和半導體聯合新思科技在全球首發了“3DIC先進封裝設計分析全流程”EDA平臺,是目前國內唯一布局了3DIC先進封裝的本土EDA公司。芯和半導體技術支持總監蘇周祥在本節課程中為我們全面分析3DIC先進封裝最新的發展趨勢,以及EDA如何迎接這其中的各項設計挑戰。

應用案例

如何實現 “無阻抗校準的TOD去嵌”?

隨著數據傳輸速率的不斷提升,無源互連通道所承載的傳輸速率已經超過 67Gbps 甚至更高。為了能夠準確預估無源通道的真實特性,需要具備更高帶寬的測量儀器。然而,在現實的高速測量過程中,工程師難免都會遇到去嵌的問題:即待測器件無法與儀器直接相連,必須在兩者之間插入轉換夾具才能夠實現測量,此時的測量結果同時包含了待測器件和夾具的效應,而在最終的結果中需要把夾具效應去除。

芯和半導體的SnpExpert針對不同應用場景提供了兩種去嵌方法,包括Open-Short/Thru和 Thru-Only De-embedding(TOD)。本文著重介紹如何在不進行阻抗校準的情況下進行TOD去嵌,并通過實際案例,詳細演示去嵌流程與結果。

高速接口利用T-coil的帶寬提升解決方案

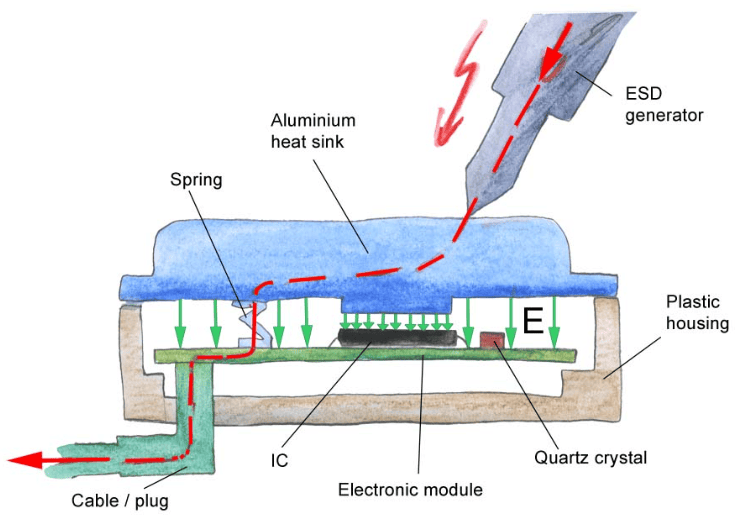

隨著集成電路尺寸的縮小,以及集成電路工作速率的不斷攀升,數據通信網絡、微處理器、存儲等產品的高速IO接口已經達到幾十甚至上百GHz并對靜電防護(ESD)越來越嚴格。然而,較大的ESD防護網絡擁有高量級的電容,這對于接口帶寬非常不利。是否能通過一種有效的方案,在不減少ESD電容的情況下,有效提升高速接口的帶寬呢?

設計訣竅視頻

如何在Hermes PSI中進行電源完整性分析

本次視頻將為各位帶來:如何使用芯和Hermes PSI工具,對電源網絡的直流壓降進行建模和仿真流程。

我們將以“一塊PCB設計板”為例,為您一步步展示:

如何導入PCB版圖文件至Hermes PSI中;

配置VRM和SINK;

檢查DC結果電壓分布圖,電流密度圖和功率密度圖。

原文標題:員工抗疫物資已到——芯和半導體電子雜志4月刊

文章出處:【微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

ESD

+關注

關注

49文章

2037瀏覽量

173087 -

電子系統

+關注

關注

0文章

417瀏覽量

31181 -

芯和半導體

+關注

關注

0文章

107瀏覽量

31439

原文標題:員工抗疫物資已到——芯和半導體電子雜志4月刊

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

集成電路電磁兼容性及應對措施相關分析(一) 電子系統性能要求與ESD問題

集成電路電磁兼容性及應對措施相關分析(一) — 電子系統性能要求與ESD問題

虛擬設計與優化電力電子系統依賴于半導體芯片模型

第二季度電子系統設計行業增長18.2%

西門子EDA發布下一代電子系統設計平臺

使用泰克示波器精確診斷并優化汽車電子系統

24芯M16插座在汽車電子系統中的關鍵作用

宏微科技將參加2024德國紐倫堡電力電子系統及元器件展覽會

瑞薩收購Altium,以推動電子系統設計與創新

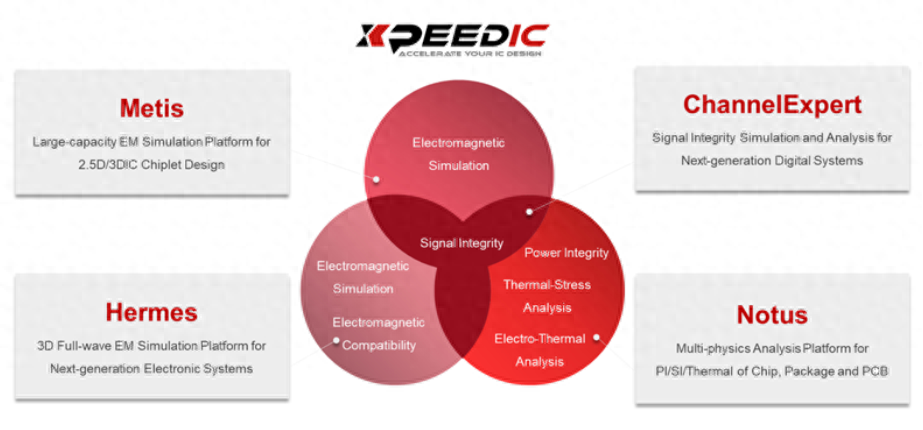

芯和半導體在DesignCon2024大會上發布針對下一代電子系統的SI/PI/多物理場分析EDA解決方案

DesignCon2024 | 芯和半導體發布針對下一代電子系統的“SI/PI/多物理場分析”EDA解決方案

ESD電子系統設計聯盟宣布芯和半導體加盟

ESD電子系統設計聯盟宣布芯和半導體加盟

評論