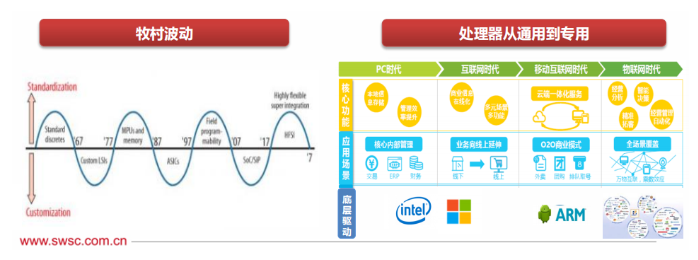

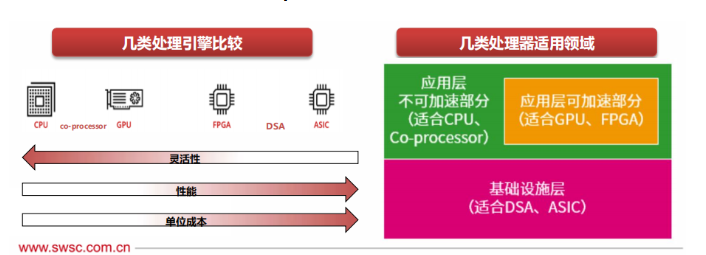

1)從通用到專用:面向不同的場景特點定制芯片,XPU、FPGA、DSA、ASIC應運而生。

2)從底層到頂層:軟件、算法、硬件架構。架構的優化能夠極大程度提升處理器性能,例如AMD Zen3將分離的兩塊16MB L3 Cache合并成一塊32MB L3 Cache,再疊加改進的分支預測、更寬的浮點unit等,便使其單核心性能較Zen2提升19%。

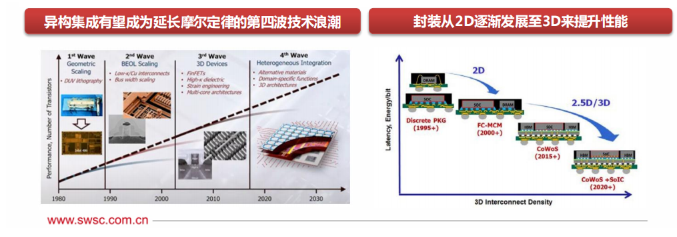

3)異構與集成:蘋果M1 Ultra芯片的推出帶來啟迪,利用逐步成熟的3D封裝、片間互聯等技術,使多芯片有效集成,似乎是延續摩爾定律的最佳實現路徑。

主流芯片廠商已開始全面布局:Intel已擁有CPU、FPGA、IPU產品線,正加大投入GPU產品線,推出最新的Falcon Shores架構,打磨異構封裝技術;NvDIA則接連發布多芯片模組(MCM,Multi-Chip Module)Grace系列產品,預計即將投入量產;AMD則于近日完成對塞靈思的收購,預計未來走向CPU+FPGA的異構整合。

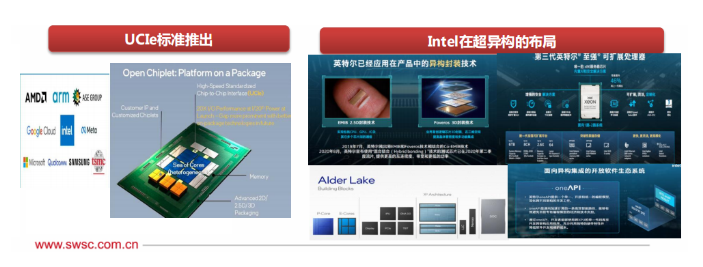

此外,英特爾、AMD、Arm、高通、臺積電、三星、日月光、Google云、Meta、微軟等十大行業主要參與者聯合成立了Chiplet標準聯盟,正式推出通用Chiplet的高速互聯標準“Universal Chiplet InterconnectExpress”(通用小芯片互連,簡稱“UCIe”)。

在UCIe的框架下,互聯接口標準得到統一。各類不同工藝、不同功能的Chiplet芯片,有望通過2D、2.5D、3D等各種封裝方式整合在一起,多種形態的處理引擎共同組成超大規模的復雜芯片系統,具有高帶寬、低延遲、經濟節能的優點。

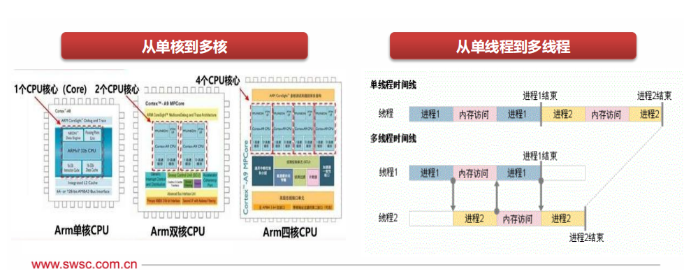

以多核提升性能功耗比:多核處理器把多個處理器核集成到同一個芯片之上,每個單元的計算性能密度得以大幅提升。同時,原有的外圍部件可以被多個CPU系統共享,可帶來更高的通信帶寬和更短的通信時延,多核處理器在并行性方面具有天然的優勢,通過動態調節電壓/頻率、負載優化分布等,可有效降低功耗,提升性能。

以多線程提升總體性能:通過復制處理器上的結構狀態,讓同一個處理器上的多個線程同步執行并共享處理器的執行資源,可以極小的硬件代價獲得相當比例的總體性能和吞吐量提高。

微架構的改進

眾多算數單元、邏輯單元、寄存器在三態總線和單項總線,以及各個控制線的連接下共同組成CPU微架構。不同的微架構設計,對CPU性能和效能的提升發揮著直觀重要的作用。

微架構的升級,一般涉及到指令集拓展、硬件虛擬化、大內存、亂序執行等等一系列復雜的工作,還涉及到編譯器、函數庫等軟件層次的修改,牽一發而動全身。

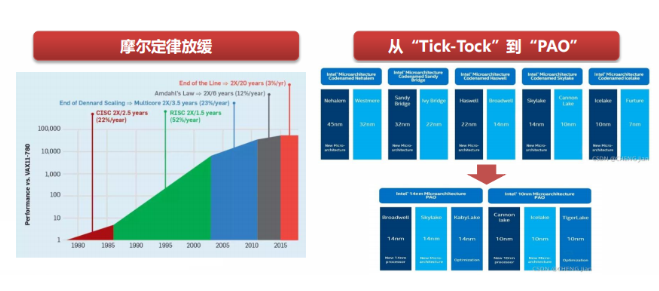

摩爾定律放緩

摩爾定律于上世紀60年代提出,直至2011年前,計算機元器件的小型化是提升處理性能的主要因素。2011年后,摩爾定律開始放緩,制硅工藝的改進將不再提供顯著的性能提升。

“Tick-Tock”模式失效

自2007年開始,英特爾開始實施“Tick-Tock”發展模式,以兩年為周期,在奇數年(Tick)推出新制成工藝,在偶數年(Tock)推出新架構的微處理器。

在14nm轉10nm接連推遲后,英特爾自2016年起宣布停止 “Tick-Tock”處理器升級周期,改為處理器升級的三步戰略:制程工藝(Process)-架構更新(Architecture)-優化(Optimization)。

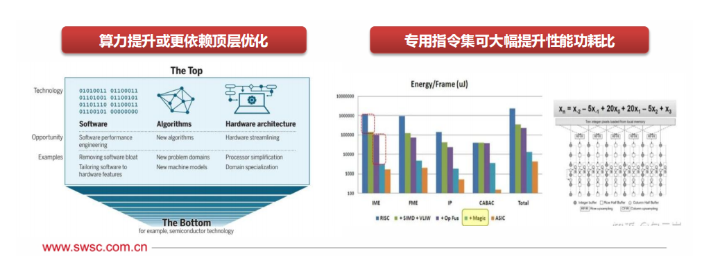

后摩爾時代,頂層優化或更為重要

新的底層優化路徑被提出,例如3D堆疊、量子計算、光子學、超導電路、石墨烯芯片等,技術目前仍處于起步階段,但后續有望突破現有想象空間。

根據MIT在《Science》發布的文章,后摩爾定律時代,算力提升將更大程度上來源于計算堆棧的「頂層」,即軟件、算法和硬件架構。

通用指令集為了覆蓋更多應用,往往需要支持上千條指令,導致流水線前端設計(取指、譯 碼、分支預測等變得十分復雜),對性能功耗會產生負面影響。

領域專用指令集可大大減少指令數量,并且能夠增大操作粒度,融合訪存優化,實現數量級提高性能功耗比。

新興場景出現,CPU從通用向專用發展

1972年,戈登·貝爾(Gordon Bell)提出,每隔10年,會出現新一類計算機(新編程平臺、 ,新網絡連接、新用戶接口,新使用方式且更廉價),形成新的產業。 1987 年, 原日立公司總工程師牧村次夫(Tsugio Makimoto) 提出,半導體產品未來可能將沿著“標準化”與“定制化”交替發展的路線前進,大約每十年波動一次。

經歷了桌面PC、互聯網時代和移動互聯網時代后,“萬物智聯”已成為新的風向標,AIoT正掀起世界信息產業革命第三次浪潮。而AIoT最明顯的特征是需求碎片化,現有的通用處理器設計方法難以有效應對定制化需求。

通用與性能,難以兼得

CPU是最通用的處理器引擎,指令最為基礎,具有最好的靈活性。Coprocessor,是基于CPU的擴展指令集的運行引擎,如ARM的NEON、Intel的AVX、AMX擴展指令集和相應的協處理器。

GPU,本質上是很多小CPU核的并行,因此NP、Graphcore的IPU等都和GPU處于同一層次的處理器類型。

FPGA,從架構上來說,可以用來實現定制的ASIC引擎,但因為硬件可編程的能力,可以切換到其他ASIC引 擎,具有一定的彈性可編程能力。

DSA,是接近于ASIC的設計,但具有一定程度上的可編程。覆蓋的領域和場景比ASIC要大,但依然存在太多的領域需要特定的DSA去覆蓋。

ASIC,是完全不可編程的定制處理引擎,理論上最復雜的“指令”以及最高的性能效率。因為覆蓋的場景非常小,因此需要數量眾多的ASIC處理引擎,才能覆蓋各類場景。

后摩爾定律時代,展望CPU未來發展之路

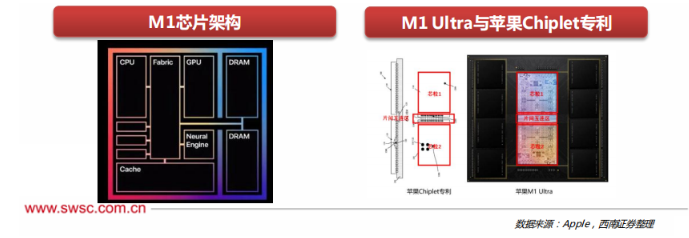

不可逆轉的SoC集成:由于集成電路集成度不斷提高,將完整計算機所有不同的功能塊一次直接集成于一顆芯片上的 SoC 片上就成為整個半導體行業發展的一個趨勢,可以顯著降低系統成本和功耗,提高系統可靠性。M1 并不是傳統意義上的 CPU,而是一顆SoC。CPU采用了8核心,包括4個高性能核心和4個高能效核心。每個高性能核心都提供出色的單線程任務處理性能,并在允許的范圍內將能耗降至最低。

異構能力的大幅提升:M1還采用了統一內存架構(UMA),CPU、GPU、神經引擎、緩存、DRAM內存全部通過Fabric高速總線連接在一起,得益于此,SoC中的所有模塊都可以訪問相同的數據,而無需在多個內存池之間復制數據,帶寬更高、延遲更低,大大提高了處理器的性能和電源效率。此外,最新一代的M1 Ultra本質上是兩個M1 MAX的有效組合,通過UltraFusion架構,提供高達128G統一內存,相較M1的GPU性能提高8倍。

蘋果M1處理器完成了一次從多芯片走向一體化的過程,這也是蘋果打造完整PC生態鏈的必經之路,讓我們看見了CPU未來發展的更多可能性。

后摩爾時代,異構與集成

海外芯片巨頭積極布局異構計算:英特爾現已布局CPU、FPGA、IPU、GPU產品線,并接連公布Alder Lake、Falcon Shores等新架構;英偉達接連發布多芯片模組(MCM,Multi-ChipModule)Grace系列產品,預計即將投入量產;AMD則于近日完成對塞靈思的收購,預計未來走向CPU+FPGA的異構整合。

晶圓廠和封裝廠亦積極投入異構集成:異構計算需要有先進的集成封裝技術,得益于近十年來先進封裝與芯片堆疊技術的發展,例如3D堆疊、SiP等,也使得異構集成成為了大幅存在可能。目前,2.5D封裝技術已發展較為成熟,例如臺積電的CoWoS,三星的I-Cube,3D封裝成為各大晶圓廠發力方向。英特爾已開始量產Foveros技術,三星已完成X-Cube的驗證,臺積電亦提出了SoiC的整合方案。

CPU+XPU已廣泛應用,但仍有優化空間。傳統的異構計算架構存在IO路徑較長,輸入輸出資源損耗等固有問題,并且仍然無法完全兼顧極致性能與靈活性。

Chiplet聯盟組建,探索超異構可能性。2022年3月3日,英特爾、AMD、Arm、高通、臺積電、三星、日月光、Google云、Meta、微軟等十大行業巨頭聯合成立了Chiplet標準聯盟,正式推出了通用Chiplet的高速互聯標準“Universal Chiplet Interconnect Express”(通用小芯片互連,簡稱“UCIe”)。

在UCIe的框架下,互聯接口標準得到統一。各類不同工藝、不同功能的Chiplet芯片,有望通過2D、2.5D、3D等各種封裝方式整合在一起,多種形態的處理引擎共同組成超大規模的復雜芯片系統,具有高帶寬、低延遲、經濟節能的優點。

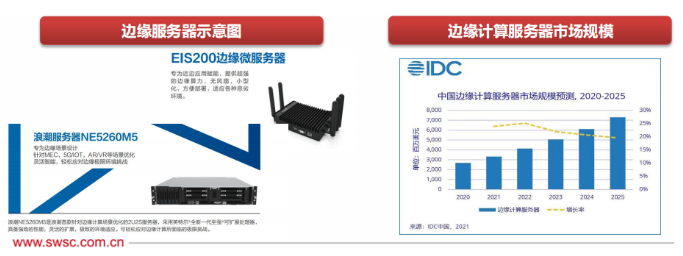

邊緣計算服務器是解決AIoT時代“算力荒”的必備產物

云計算無法滿足海量、實時的處理需求。伴隨人工智能、5G、物聯網等技術的逐漸成熟,算力需求從數據中心不斷延伸至邊緣,以產生更快的網絡服務響應,滿足行業在實時業務、應用智能、安全與隱私保護等方面的基本需求。

市場規模爆發式增長。根據IDC,中國邊緣計算服務器整體市場規模達到33.1億美元,較2020年增長23.9%,預計2020-2025年CAGR將達到22.2%,高于全球的20.2%。

定制服務器快速增加。當前通用服務器和邊緣定制服務器占比分別為87.1%和12.9%,隨著邊緣應用場景的逐漸豐富,為適應復雜多樣的部署環境和業務需求,對于具有特定外形尺寸、低能耗、更寬工作溫度以及其他特定設計的邊緣定制服務器的需求將快速增加。IDC預計邊緣定制服務器將保持76.7%的復合增速,2025年滲透率將超過40%。

根據業務場景多樣定制,集成化是趨勢

區別于數據中心服務器,邊緣服務器配置并不一味追求最高計算性能、最大存儲、最大擴展卡數量等參數,而是在有限空間里面盡量提供配置靈活性。當前邊緣服務器多用于工業制造等領域,需根據具體環境(高壓、低溫、極端天氣)等選擇主板、處理器等,下游需求呈現碎片化,未有統一的標準。

伴隨越來越多的計算、存儲需求被下放至邊緣端,當前趨勢通常涉及更緊密的加速集成,以滿足包括AI算力在內的多種需求。超大規模云提供商正在開始研究分類體系結構,為了減少熟悉的多租戶方法不可避免的碎片化,其中計算、存儲、網絡和內存成為一組可組合的結構,機柜式架構(RSA)分別部署了CPU、GPU、硬件加速、RAM、存儲和網絡容量。

云服務器正在全球范圍內取代傳統服務器

云服務器的發展使中國成為全球服務器大國。隨著移動終端、云計算等新一代信息技術的發展和應用,企業和政府正陸續將業務從傳統數據中心向云數據中心遷移。雖然目前中國云計算領域市場相比美國相對落后,但近年來我國的云計算發展速度顯著高于全球云計算市場增長速度,預計未來仍將保持這一趨勢。

面向不同需求,提供多樣性算力。一般小型網站請求處理數據較少,多采用1、2核CPU;地方門戶、小型行業網站,需要4核以上的CPU;而電商平臺,影視類網站等,則需要16核以上的CPU。此外,云服務器亦提供靈活的擴容、升級等服務,一般均支持異構類算力的加載。

CPU+ASIC,云服務器異構趨勢明顯

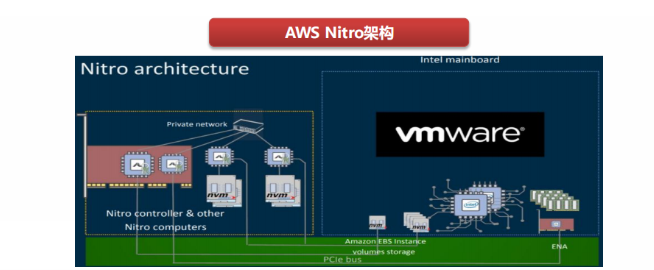

在傳統的計算機虛擬化架構中,業務層為虛擬機,管理層為宿主機,業務和管理共存于CPU運行,導致CPU大概只有七成的資源能夠提供給用戶。

AWS創造性進行架構重構,將業務和管理分離到兩個硬件實體中,業務運行在CPU,管理則運行在NITRO芯片中,既將虛擬化的損耗挪到定制的Nitro系統上,又提高了安全性。

Nitro架構不僅性能強大,而且特別靈活,可以基于一些常用的Hypervisor(如qemu-kvm,vmware)運行虛擬機,甚至可以直接裸跑操作系統,可節省30%CPU資源。

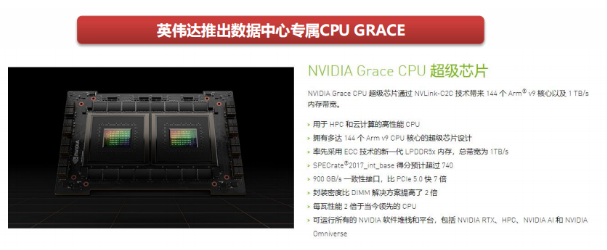

ARM或成重要挑戰者,英偉達推出首款數據中心專屬CPU GRACE

公有云巨頭價格競爭激烈,國內一線城市能耗管控嚴格,ARM移動端的優勢和低能耗特征是超大型數據中心解決節能和成本問題的重要方案之一;國內自主可控趨勢背景下,若能夠搭建強有力的生態聯盟,是未來可能顛覆原有格局的最有力挑戰者。

英偉達宣布推出首款面向AI基礎設施和高性能計算的數據中心專屬CPU——NvDIA Grace,由兩個CPU芯片通過最新一代NVLink-C2C技術互聯組成。

Grace基于最新的ARMv9架構,單個socket擁有144個CPU核心,利用糾錯碼(ECC)等機制提供當今領先服務器芯片兩倍的內存帶寬和能效,兼容性亦十分突出,可運行NvDIA所有的軟件堆棧和平臺,包括NvDIA RTX、HPC、Omniverse等。

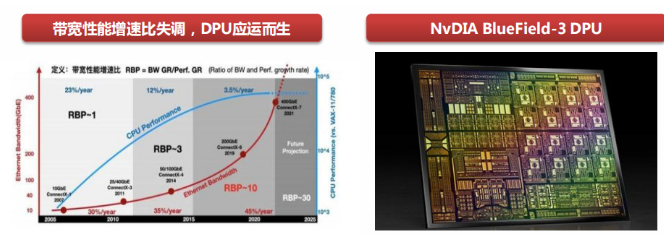

從CPU到CPU+DPU

DPU,即數據處理單元(Data Processing Unit),主要作為CPU的卸載引擎,主要處理網絡數據和IO數據,并提供帶寬壓縮、安全加密、網絡功能虛擬化等功能,以釋放CPU的算力到上層應用。

2013年,AWS研發的的Nitro和阿里云研發的X-Dragon均可看作DPU前身;英偉達在2020年正式發布一款命名為“DPU”的產品,將其定義為CPU和GPU之后的第三顆主力芯片,DPU的出現是異構計算的另一個階段性標志。

DPU是CPU和GPU的良好補充,據英偉達預測,每臺服務器可能沒有GPU,但必須有DPU,用于數據中心的DPU的量將達到和數據中心服務器等量的級別。

從CPU到CPU+XPU

AI模型通過數千億的參數進行訓練,增強包含數萬億字節的深度推薦系統,其復雜性和規模正呈現爆炸式增長。這些龐大的模型正在挑戰當今系統的極限,僅憑CPU的優化難以滿足其性能需求。

因此,AI服務器主要采用異構形式,表現形態多為機架式。在異構方式上,可以為CPU+GPU、CPU+FPGA、CPU+TPU、CPU+ASIC或CPU+多種加速卡。

現在市面上的AI服務器普遍采用CPU+GPU的形式,因為GPU與CPU不同,采用的是并行計算的模式,擅長梳理密集型的數據運算,如圖形渲染、機器學習等。繼續擴展模型以實現高度準確性和實用性,需要能夠快速訪問大型內存池并使 CPU 和 GPU 緊密耦合。

從CPU到CPU+TPU

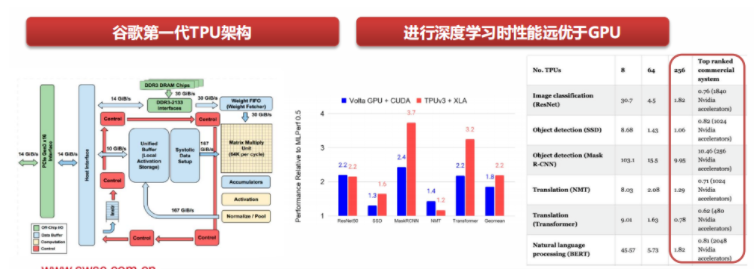

TPU,即張量處理單元(Tensor Processing Unit),是Google為加速深度學習所開發的專用集成電路(DSA),采用專用CISC指令集,自定義改良邏輯、線路、運算單元、內存系統架構、片上互聯等,并針對Tensorflow等開源框架進行優化。

2015年起,谷歌發布TPUv1,應用于Alpha Go等特定內部項目;2018年,谷歌發布TPUv3,開始向第三方出售,TPU開始逐漸走向商用。

2021年,谷歌發布TPUv4i,其性能相較第三代TPU提升2.7倍;256塊TPU僅用1.82分鐘便完成NLP領域著名的“BERT”模型訓練,而同樣條件下,利用Nvdia A100 GPU則需要3.36分鐘。

-

asic

+關注

關注

34文章

1204瀏覽量

120550 -

cpu

+關注

關注

68文章

10878瀏覽量

212135 -

AI

+關注

關注

87文章

31087瀏覽量

269414

發布評論請先 登錄

相關推薦

后摩爾定律時代 未來CPU處理器技術發展趨勢

后摩爾定律時代 未來CPU處理器技術發展趨勢

評論