在FPGA實際的開發(fā)中,官方提供的IP并不是適用于所有的情況,需要根據(jù)實際修改,或者是在自己設(shè)計的IP時,需要再次調(diào)用時,我們可以將之前的設(shè)計封裝成自定義IP,然后在之后的設(shè)計中繼續(xù)使用此IP。因此本次詳細(xì)介紹使用VIvado來封裝自己的IP,并使用IP創(chuàng)建工程。

一、IP的創(chuàng)建

首先新建工程。

如前面部分介紹的工程創(chuàng)建,完成代碼的設(shè)計、輸入,并在功能仿真或時序仿真完全正確的情況下。

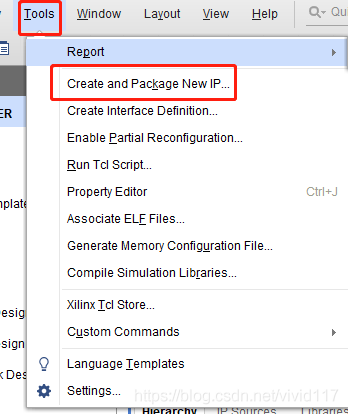

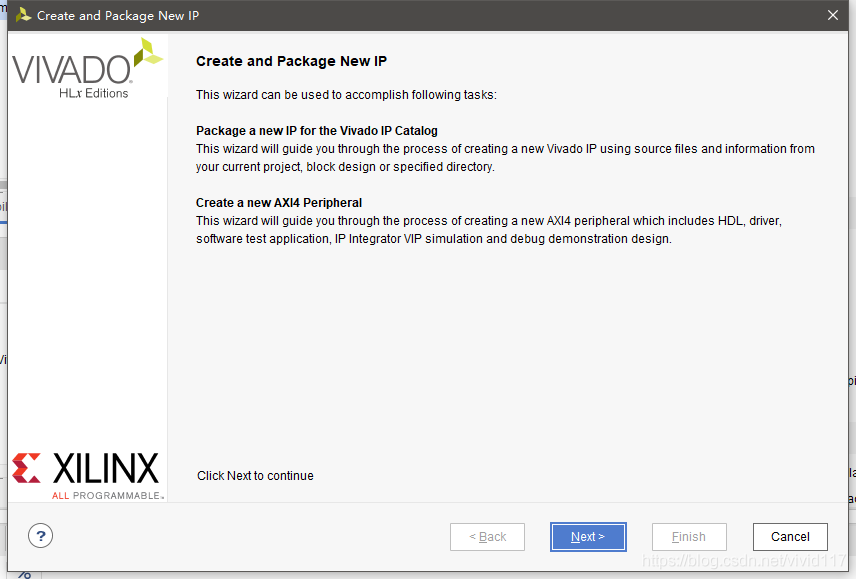

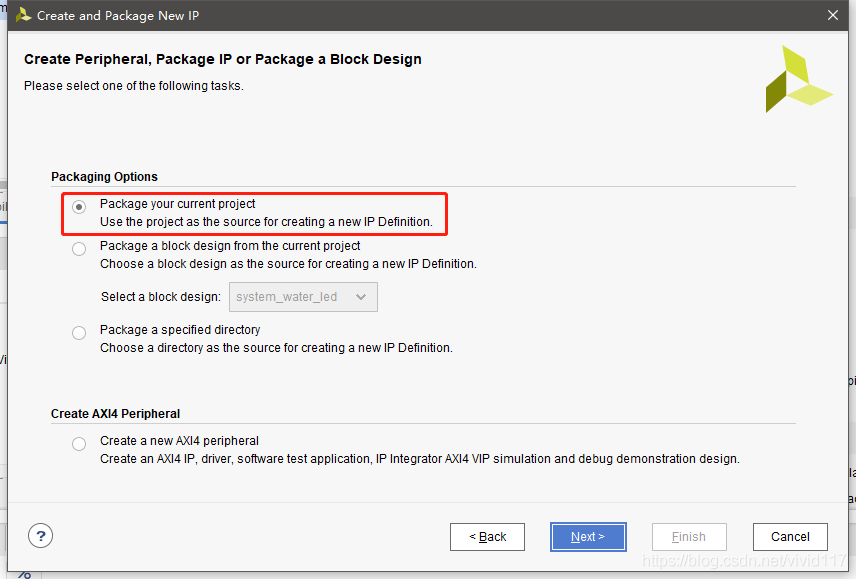

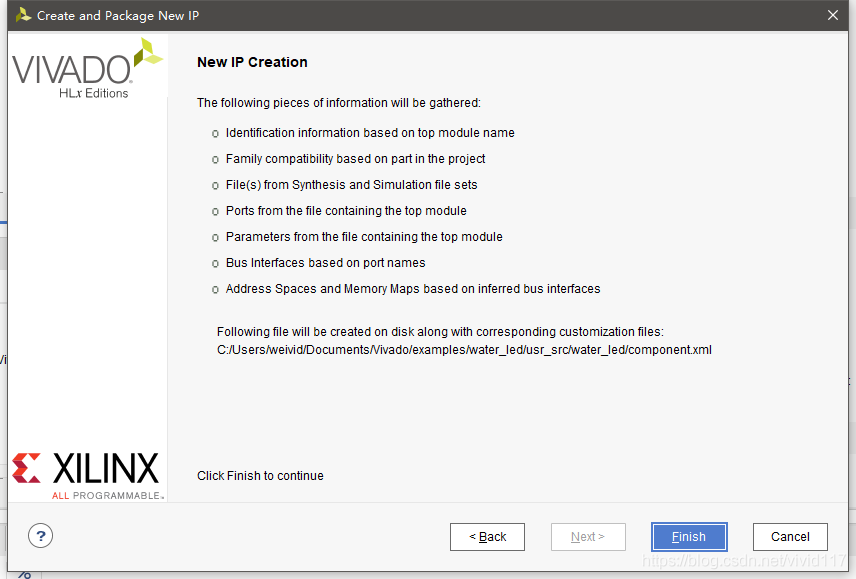

按如下步驟執(zhí)行:

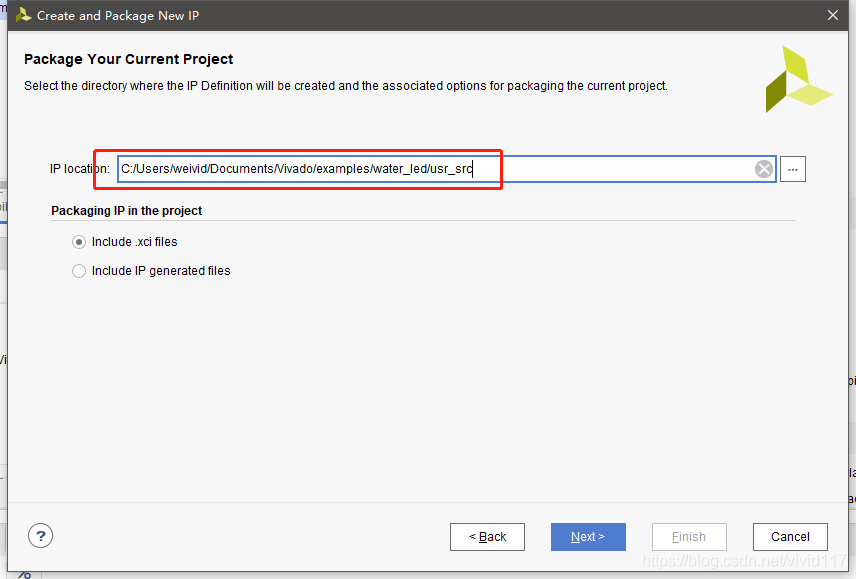

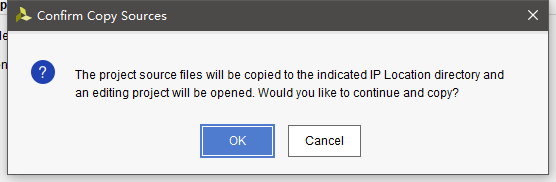

選擇要存放的位置,這一步很重要,可以存放在以后專門自定義的IP文件夾內(nèi),方便以后添加和管理查看。

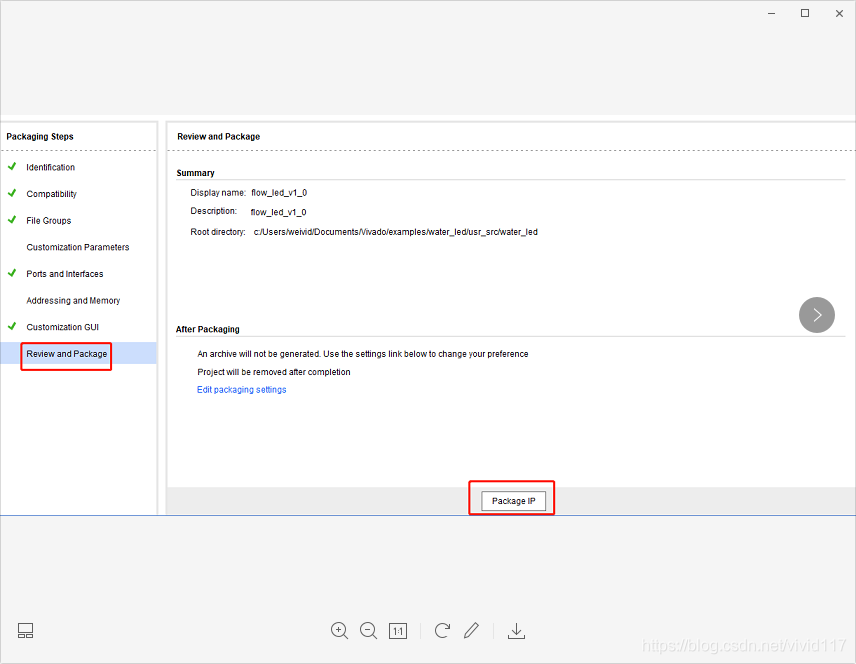

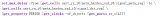

然后會彈出如下封裝IP的界面,按如下執(zhí)行Package IP

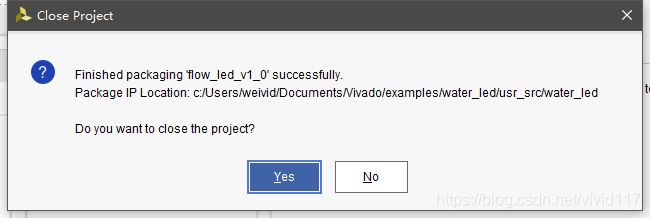

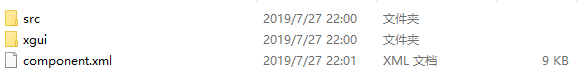

至此,我們IP就封裝好了。可以打開我們IP的文件夾,包括三個文件,src是源代碼文件。

二、IP的使用

本次設(shè)計采用block design來使用自定義的IP。

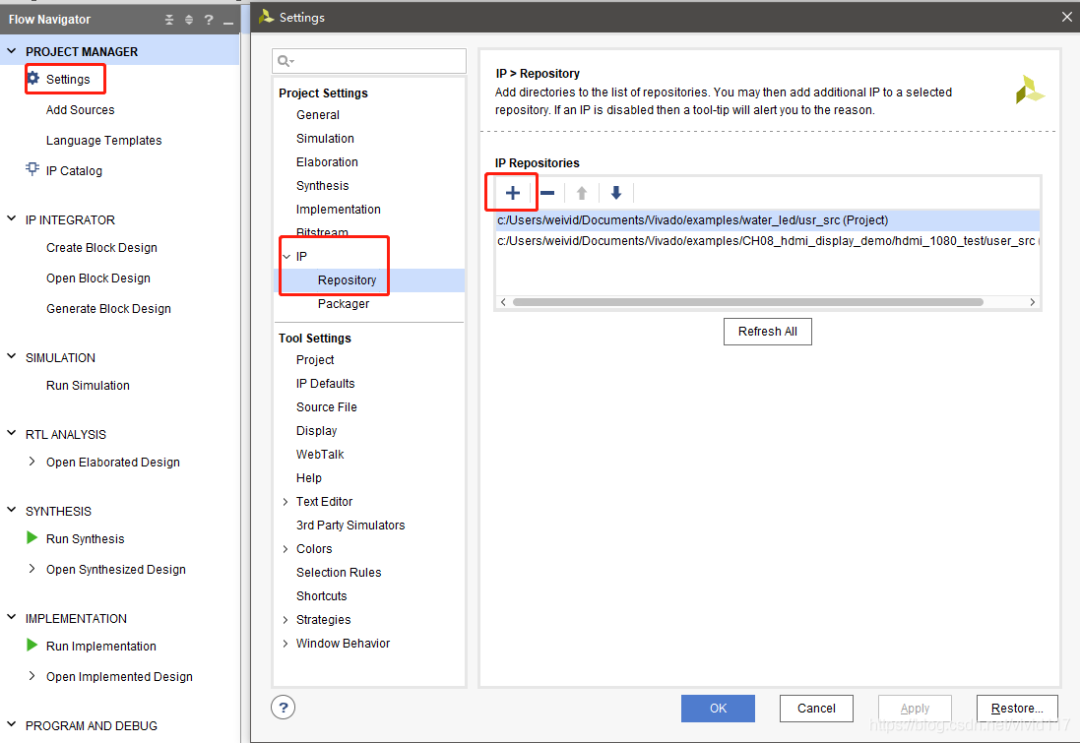

IP的添加。

1.新建一個vivado工程。

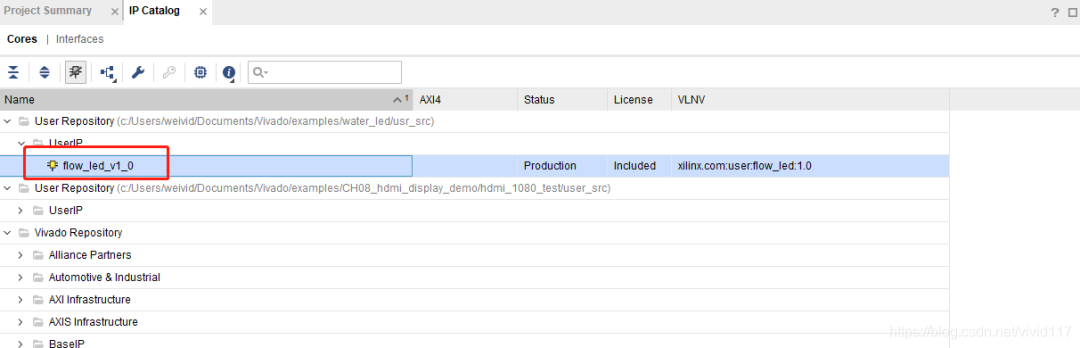

按照上面的步驟添加自定義的IP。

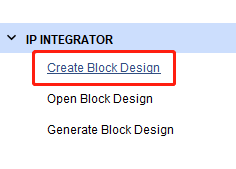

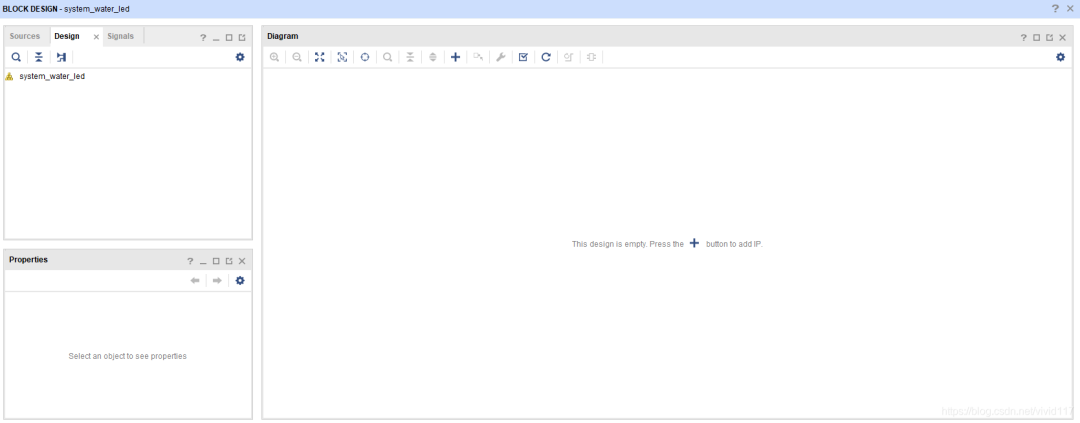

創(chuàng)建一個BD文件

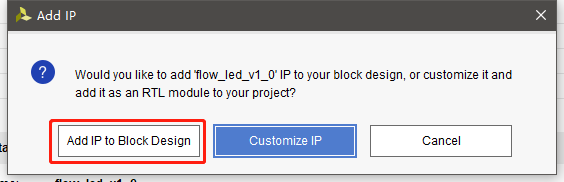

使用自定義的IP

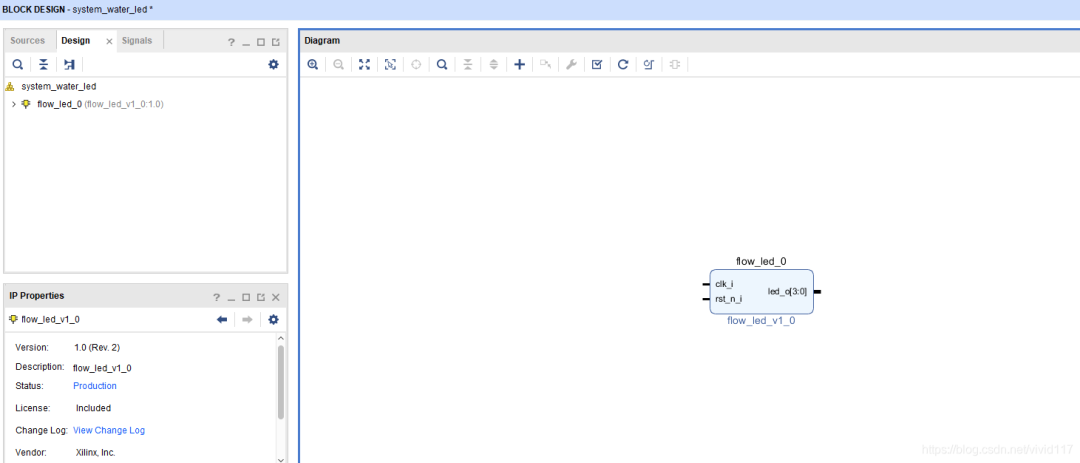

添加完之后如下:

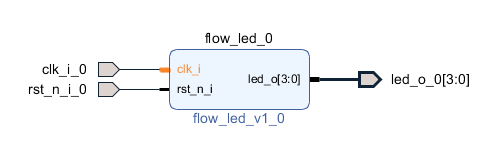

將引腳引出并重新命名,具體操作選中相應(yīng)的管腳,右鍵選擇make external

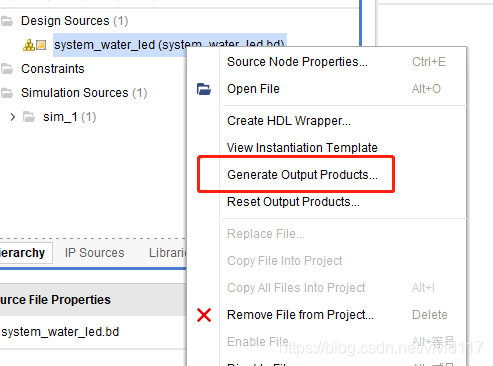

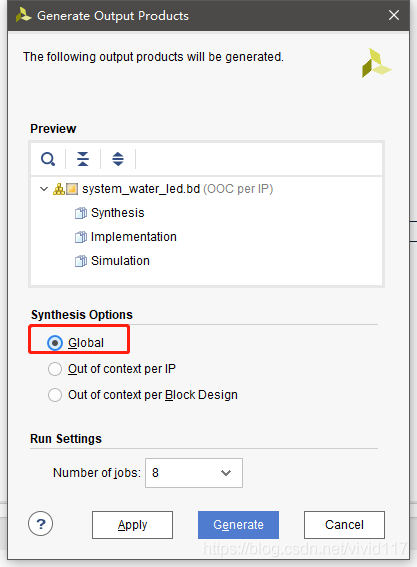

然后右鍵選擇general output product

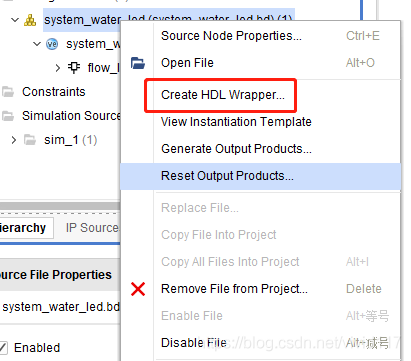

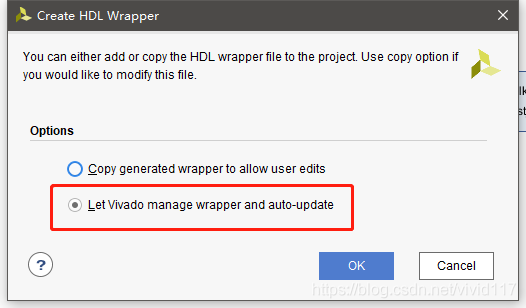

然后右鍵選擇 create HDL wrapper。

最后添加約束文件并進(jìn)行綜合編譯產(chǎn)生bit流,然后上班調(diào)試。

原文標(biāo)題:FPGA學(xué)習(xí)-Vivado封裝自定義IP及調(diào)用

文章出處:【微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21979瀏覽量

614495 -

封裝

+關(guān)注

關(guān)注

128文章

8553瀏覽量

144856 -

Vivado

+關(guān)注

關(guān)注

19文章

830瀏覽量

68289

原文標(biāo)題:FPGA學(xué)習(xí)-Vivado封裝自定義IP及調(diào)用

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

PYNQ設(shè)計案例:基于HDL語言+Vivado的自定義IP核創(chuàng)建

vivado帶ip核的工程封裝

基于 FPGA vivado 2017.2 的74系列IP封裝

xilinx vivado 怎么封裝包含一個ip核的自定義ip?

怎么在vivado HLS中創(chuàng)建一個IP

Xilinx Vivado的使用詳細(xì)介紹(3):使用IP核

vivado調(diào)用IP核詳細(xì)介紹

如何在vivado創(chuàng)建新工程上使用IP集成器創(chuàng)建塊設(shè)計

vivado創(chuàng)建工程流程

Vivado設(shè)計套件用戶指南:創(chuàng)建和打包自定義IP

Vivado Design Suite用戶指南:創(chuàng)建和打包自定義IP

評論