DDS原理及FPGA實(shí)現(xiàn)

一個(gè)按一定速度沿x軸行進(jìn),同時(shí)半徑按一定頻率在圓周上滑動(dòng)的圓,最后留下的痕跡就是一個(gè)正余弦波。

DDS全稱直接數(shù)字頻率合成(Direct Digital Synthesis),簡單來講,分以下幾步:

1.抽樣

但一般來講,為了波形的完整,我們一個(gè)周期中最少保留的點(diǎn)還會(huì)多一些。如果假設(shè)一個(gè)周期最小4個(gè)點(diǎn),采樣頻率為為100MSPS,那我們可以還原的源信號(hào)的頻率最大為25M

我們通常對(duì)一個(gè)周期采樣的點(diǎn)數(shù)為2^N個(gè),在這里,我采樣為2的8次方,即256個(gè)。

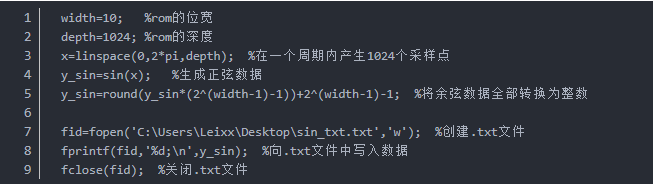

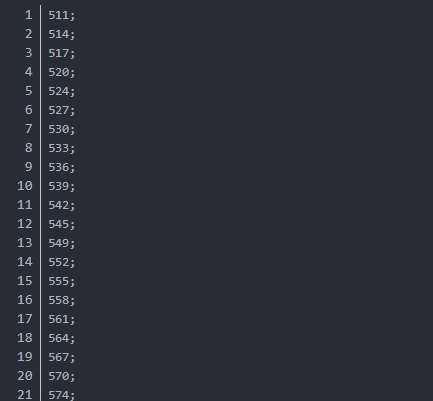

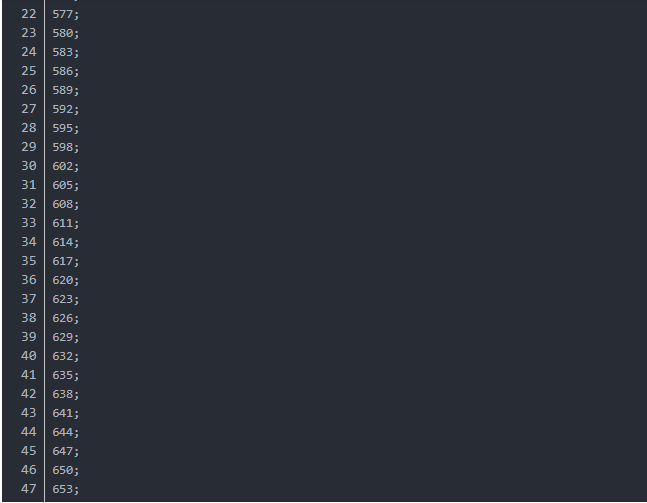

采樣的過程可以通過matlab進(jìn)行模擬,設(shè)置好采樣的位寬和深度便可以生成采樣數(shù)據(jù)。

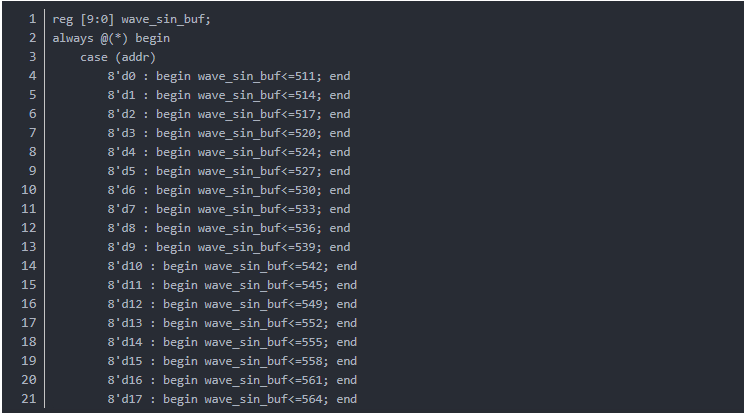

得到的部分采樣數(shù)據(jù)如下

2.合成

DDS技術(shù)的核心,簡單來說就是將我們的抽樣數(shù)據(jù)還原成模擬信號(hào)。還原的方式和文章講到的一樣:以一定的頻率將抽樣數(shù)據(jù)依次輸出,就可以還原波形。

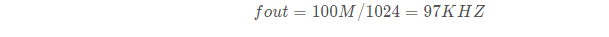

假設(shè),以100M的頻率輸出我們的1024個(gè)抽樣數(shù)據(jù),則將會(huì)得到一個(gè)頻率為

的正弦波。這就達(dá)到了最初的信號(hào)輸出。

那如何調(diào)頻呢?

調(diào)頻的方案有兩種:一種是改變我們的時(shí)鐘頻率,將我們讀取抽樣數(shù)據(jù)的速度變快或者變慢,這樣就可以改變頻率。這種方法對(duì)于當(dāng)下很多開發(fā)板固定的晶振頻率來說比較難以實(shí)現(xiàn)。

另一種方案就是減少我們輸出的抽樣數(shù)據(jù),輸出的抽樣數(shù)據(jù)越少,按照上面的公式,頻率便會(huì)越高。

比如說,我們最開始查數(shù)據(jù)是按照依次加一的方式,那我們改成依次加二,顯然,這樣做之后,輸出頻率便會(huì)提高。但也會(huì)帶來一個(gè)問題,我們輸出的點(diǎn)數(shù)少了,那么點(diǎn)與點(diǎn)之間不再平滑,輸出的波形會(huì)變得階梯化。

顯然加一會(huì)得到一個(gè)頻率,加二會(huì)得到另一個(gè)頻率,但這兩個(gè)頻率都不是我想要的怎么辦?

如何精準(zhǔn)調(diào)頻?

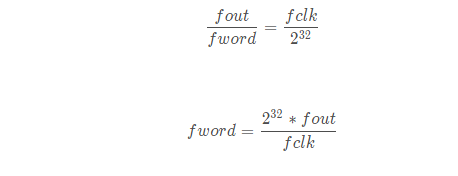

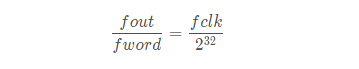

假設(shè)我們需要得到一個(gè)頻率很低的信號(hào),1KHZ,而我們的時(shí)鐘頻率為100M,我們?cè)谝粋€(gè)周期內(nèi)輸出1024個(gè)點(diǎn)也達(dá)不到這樣的頻率。因此我們就需要在輸出的每個(gè)數(shù)據(jù)之間進(jìn)行等待,可以通過設(shè)置計(jì)數(shù)器來解決這個(gè)問題。為了使輸出的信號(hào)盡可能的低,我們?cè)O(shè)置一個(gè)32位的累加器。將高10位作為查表的地址。對(duì)于1KHZ,有

所以,累加值f w o r d fwordfword為4295。

其余頻率對(duì)應(yīng)的累加值均可以按此公式計(jì)算。

如何解決階梯化?

從數(shù)字上來看,波形變得階梯化是因?yàn)槲覀冚敵龅某闃訑?shù)據(jù)減少,點(diǎn)與點(diǎn)之間不再平滑。但是從另一個(gè)角度理解,波形變得階梯化的原因是因?yàn)榀B加了其他雜波

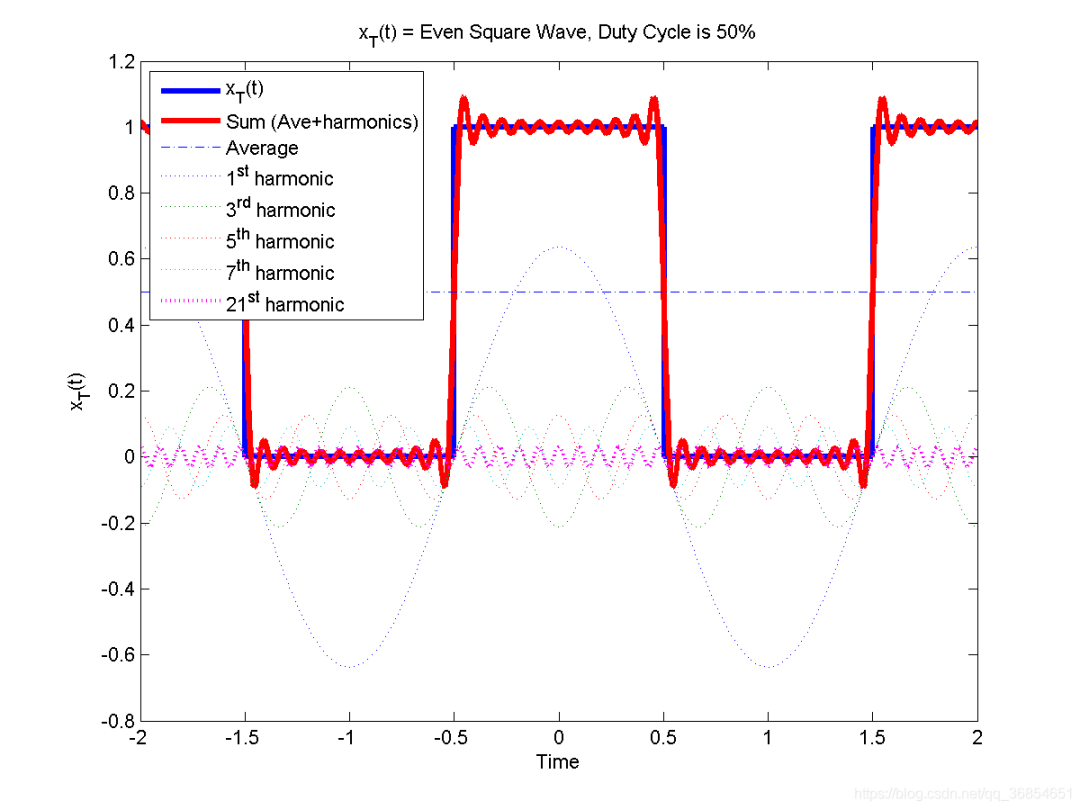

我們簡單地波形變得階梯化理解為趨近于方波。下圖是方波的合成。

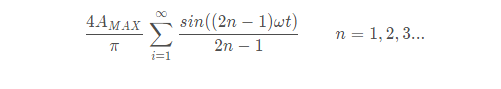

由方波的傅里葉級(jí)展開式

可以得出,方波是由無數(shù)個(gè)奇次諧波疊加起來的,頻率為2n-1倍,幅度為

因此,若我們的波形也是疊加了高頻的諧波導(dǎo)致波形階梯化,那么就通過低通濾波器來濾除高頻諧波,得到平滑的波形。

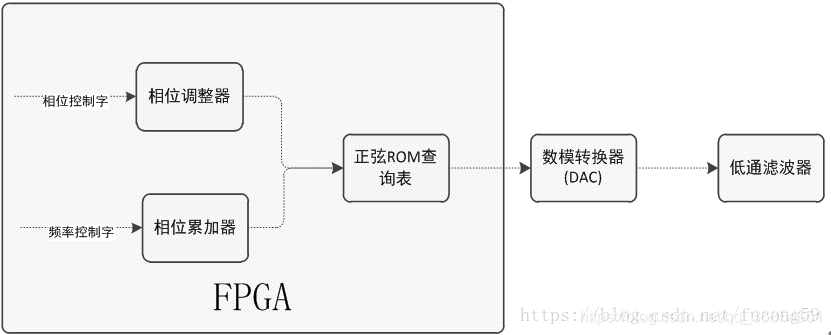

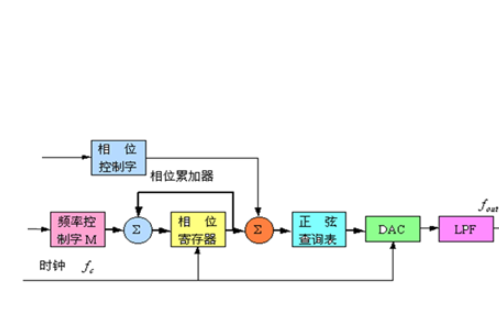

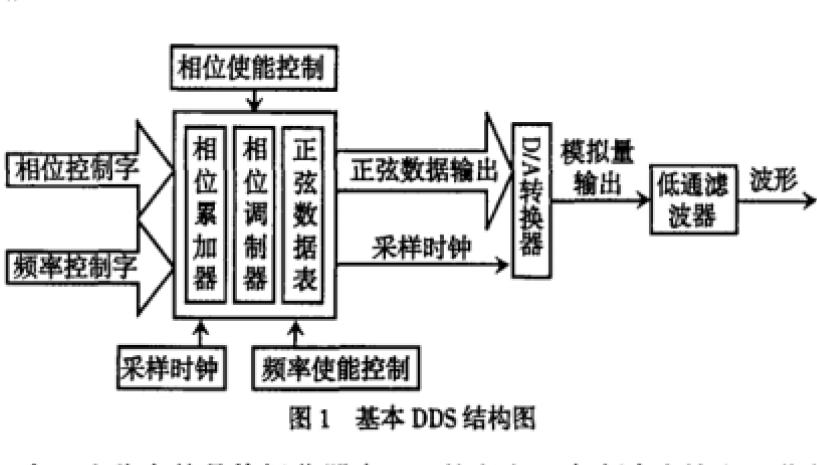

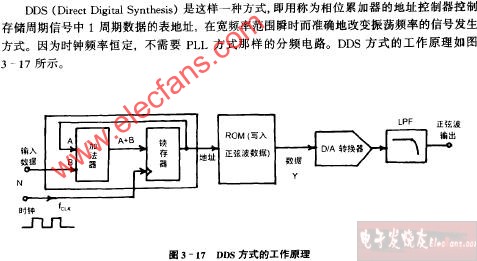

DDS的原理圖如下:

3.實(shí)現(xiàn)

基于FPGA的DDS,就是按照上面的原理來實(shí)現(xiàn)的。

我這里只儲(chǔ)存了256個(gè)數(shù)據(jù),至于原因,后面會(huì)講到。

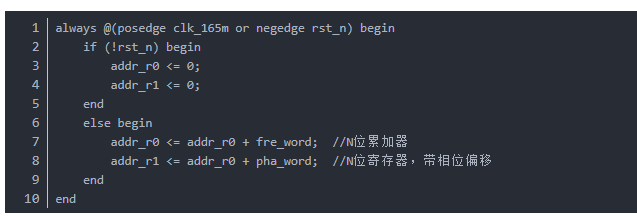

(2)累加

設(shè)置一個(gè)32位相位控制字和頻率控制字,進(jìn)行累加。

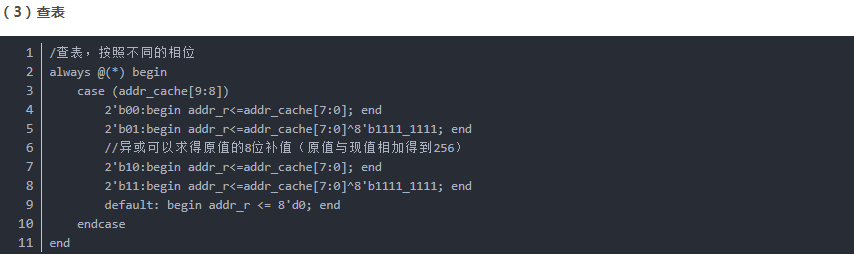

這里我只儲(chǔ)存了2^8個(gè)波形數(shù)據(jù),是為了節(jié)省寄存器資源。因?yàn)橐粋€(gè)周期的正弦波的四個(gè)相位實(shí)際上數(shù)據(jù)是有關(guān)聯(lián)的,知道第一相位的數(shù)據(jù),便可推導(dǎo)出另外三個(gè)相位的數(shù)據(jù)。

代碼中,00表示第一相位,此時(shí)按照正常的查表順序即可。

01表示第二相位,此時(shí),查表的順序應(yīng)當(dāng)是2^8-地址值。但實(shí)際上這個(gè)減法的操作就是異或的操作。

相減后,地址值8位中原本的“1”變?yōu)?,原本的“0”變?yōu)?,正好和異或的原理相同。這里為了方便,就直接寫了異或。實(shí)際上寫256-addr_cache[7:0]也是一個(gè)效果。

其余兩個(gè)相位,查表的方式類似。

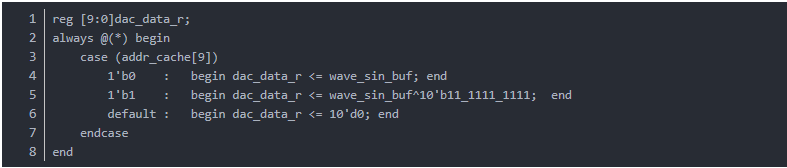

(4)轉(zhuǎn)換

因?yàn)槲疫@里的256個(gè)數(shù)據(jù)是第一相位的,而第三第四相位的數(shù)據(jù)是等于2^10減去第一相位的值,因此這里需要將輸出的數(shù)據(jù)轉(zhuǎn)換一下。

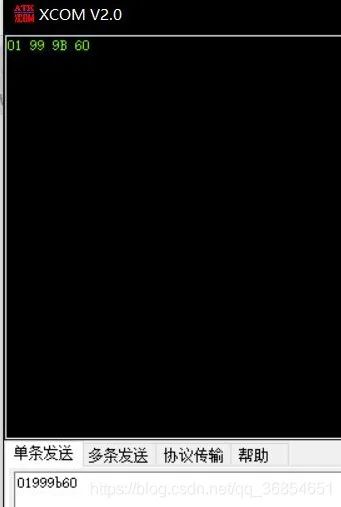

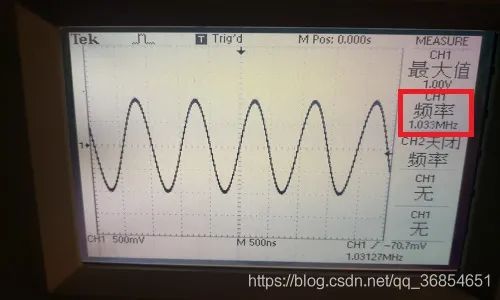

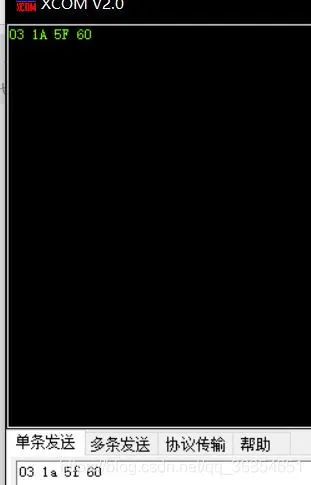

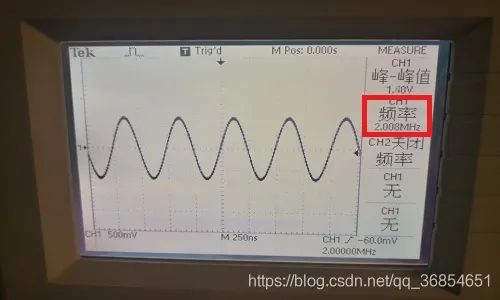

(5)測試

通過串口分別發(fā)送01999b60和031a5f60,由上面公式

可以算出分別是1M和2M的頻率控制字

以上便是DDS的FPGA實(shí)現(xiàn)。

原文標(biāo)題:FPGA學(xué)習(xí)-DDS原理及FPGA實(shí)現(xiàn)

文章出處:【微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21748瀏覽量

603865 -

DDS

+關(guān)注

關(guān)注

21文章

634瀏覽量

152697

原文標(biāo)題:FPGA學(xué)習(xí)-DDS原理及FPGA實(shí)現(xiàn)

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA實(shí)現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化...

如何利用FPGA設(shè)計(jì)DDS信號(hào)發(fā)生器?

如何利用FPGA和DDS技術(shù)實(shí)現(xiàn)正弦信號(hào)發(fā)生器的設(shè)計(jì)

如何利用現(xiàn)場可編程邏輯門陣列FPGA實(shí)現(xiàn)實(shí)現(xiàn)DDS技術(shù)?

如何利用FPGA設(shè)計(jì)DDS電路?

DDS的工作原理是什么?如何去設(shè)計(jì)DDS?

怎么實(shí)現(xiàn)基于FPGA+DDS的正弦信號(hào)發(fā)生器的設(shè)計(jì)?

基于FPGA的DDS調(diào)頻信號(hào)的研究與實(shí)現(xiàn)

基于FPGA的DDS信號(hào)源設(shè)計(jì)與實(shí)現(xiàn)

基于FPGA的DDS雜散分析及抑制方法

基于FPGA的DDS設(shè)計(jì)

DDS的基本結(jié)構(gòu)和工作原理及Matlab在DDS系統(tǒng)仿真中的應(yīng)用說明

如何使用FPGA實(shí)現(xiàn)DDS數(shù)字移相信號(hào)發(fā)生器的原理

DDS的工作原理及基于FPGA的實(shí)現(xiàn)方法

DDS的工作原理及基于FPGA的實(shí)現(xiàn)方法

評(píng)論