幾年前,我在 Design Ideas 中寫了一篇名為“ Double μC 的 PWM 頻率和分辨率”的文章,其中我提到了如何使用兩個具有相等占空比且相位為 180 度的 PWM 信號(一半一個周期延遲)彼此之間的差異。

PWM DAC 背后的想法非常簡單:它濾除 PWM 信號的所有諧波成分,只留下其中的直流分量。為此,PWM 信號經過低通濾波。顯然,當您使用具有較低截止頻率的濾波器時,輸出將更加“無紋波”,但瞬態響應將非常緩慢,反之亦然。

上述文章中提出的想法是生成一個反相信號,以通過相位抵消動作來抵消一些諧波分量,而不是僅僅依靠濾波器本身。

事實證明,這個想法在減少紋波方面很有用,同時也改善了瞬態響應。然而,它的用處是有限的,因為并非所有 PWM 信號的諧波分量都相互抵消。更具體地說,只有奇次諧波相互抵消,偶次諧波僅受濾波器影響,因為當我們引入半周期延遲時,只有奇次諧波經歷 180 度相移,偶次諧波經歷 360 度相移,即與同相相同。這導致偶次諧波不會相互抵消。

事實上,對于 50% 的占空比(它只包含奇次諧波),我們使用這種技術可以獲得無紋波輸出。對于任何其他占空比,都會有一些紋波,但與單通道等效物相比,紋波幅度仍然會有一些改進。我們可以通過使用更多具有不同相位差的 PWM 通道來擴展這個想法,以獲得更多無紋波占空比點。

假設我們決定在 f Hz 處使用 n 個通道,如果每個連續的 PWM 通道相對于彼此具有 1/(fn) 延遲(或 360/n 相移),那么每個諧波分量都將被消除,因為間隔均勻除每 n 次諧波外的時間延遲。更清楚地說,假設我們使用 10 kHz 作為我們的主要 PWM 頻率,并且我們實現了具有 25μs 時間延遲(90 度相移)的四個通道。在這種情況下,第一個通道是我們的基本通道,它沒有延遲;第二個通道相對于基本通道有 25μs 延遲(90 度);第三個通道相對于基本通道有 50μs 延遲(180 度);最后一個通道相對于基本通道有 75μs 的延遲(270 度)。

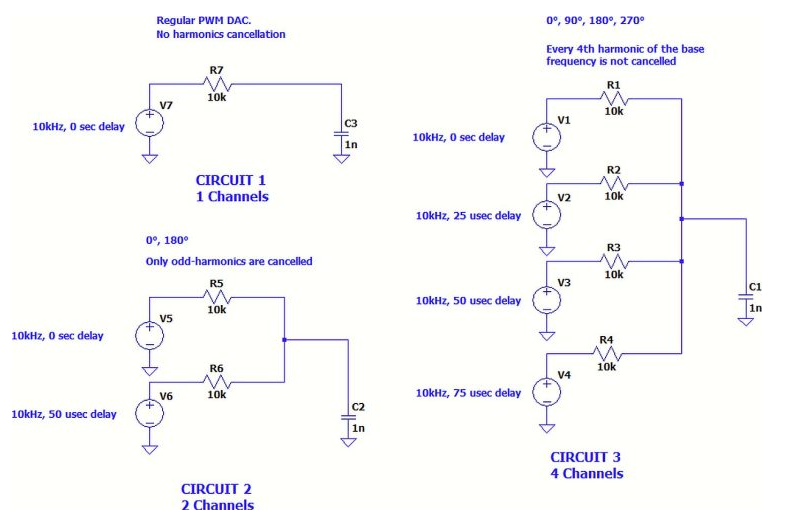

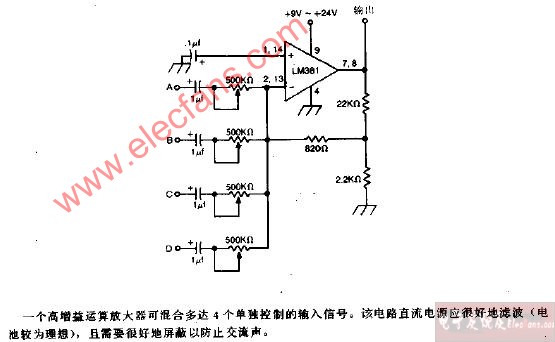

如前所述,每個連續通道相對于其“相鄰”通道具有 25μs (1/(fn), f=10kHz, n=4) 延遲。圖 1顯示了該電路以及單通道和雙通道版本。

圖 1四通道相控陣 PWM DAC 電路以及一通道和兩通道版本。

該四通道 PWM DAC 的輸出將僅包含基本 PWM 頻率的 4次諧波,因此當占空比為 25%、50% 或 75% 時,輸出將不包含紋波,因為這些 PWM 信號沒有 4次諧波含量。

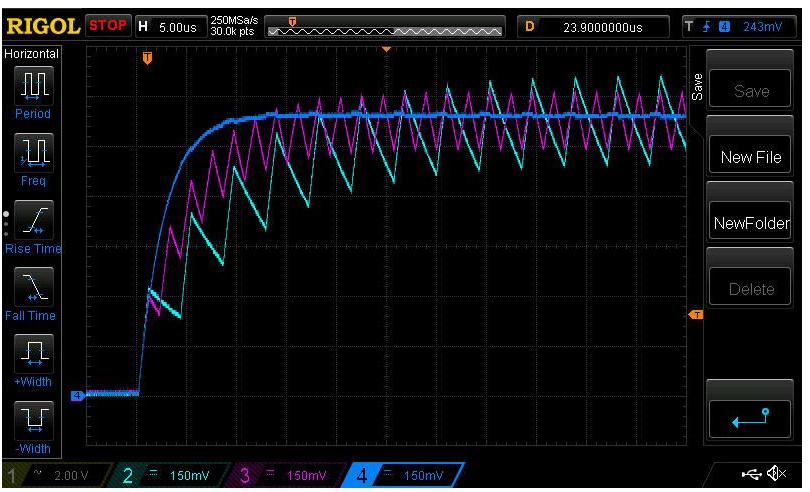

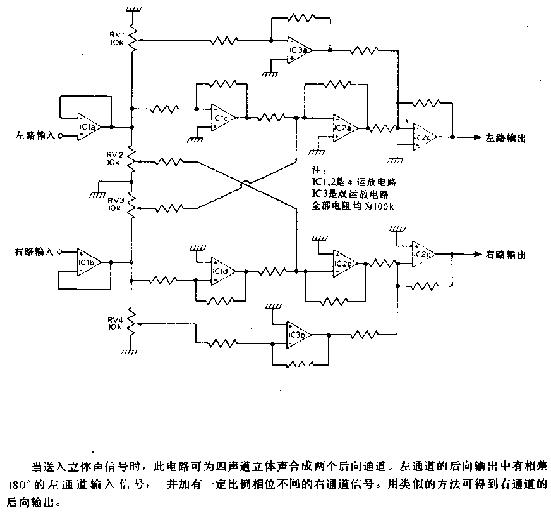

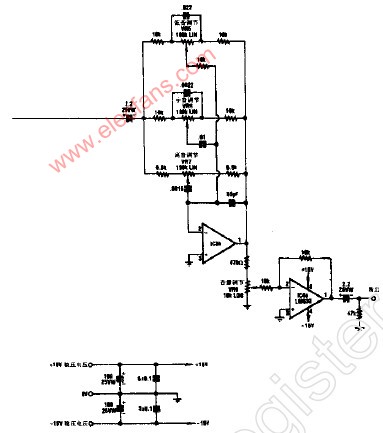

在圖 2、3和4中,我們可以看到占空比分別為 25%、50% 和 75% 的每個電路的輸出。

圖 2占空比為 25% 的電路。

圖 3占空比為 50% 的電路。

圖 4占空比為 75% 的電路。

正如預期的那樣,四通道電路(深藍色)在25%占空比下輸出幾乎沒有紋波,具有最快的瞬態響應;雙通道電路(粉紅色)有紋波,但紋波小于單通道(淺藍色)電路輸出,速度更快。在 50% 時,雙通道電路(粉紅色)和四通道電路(深藍色)都沒有任何紋波,但四通道電路具有更快的瞬態響應,顯然單通道(淺藍色)電路最慢和最吵。75% 的結果與 25% 的結果相同。

為了測試,電路是使用 FPGA 在 VHDL 中實現的(GitHub 鏈接在帖子末尾共享),因為通道很多,并且可以通過部署更多通道來進一步擴展這個想法。一般來說,如果實現了 n 個通道,將有 n-1 個無紋波占空比點(不包括 0% 和 100%,它們本身就是無紋波的)。從理論上講,使用這種方法可以使用 256 個通道實現 8 位 DAC,但當然這將是非常不切實際的,但沒有人能阻止您享受這個想法。

為了完整起見,該方法在 LTSpice 中最多模擬了 8 個通道(也在文章末尾的 GitHub 鏈接中)。出于同樣的原因,對于一個八通道電路,您應該在 12.5% 占空比點的倍數處獲得無紋波輸出;您可以通過下載 LTSpice 文件自己查看。以同樣的方式,如果您實現 100 個通道,您將在每 1% 占空比的倍數處獲得無紋波輸出。

總之,通過部署更多具有適當均勻間隔相位延遲的 PWM 通道,可以在某些占空比下實現無紋波輸出,即使在隨機占空比下,仍然可以同時改善瞬態響應和噪聲性能,這是傳統單通道 PWM DAC 方法。

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603887 -

PWM

+關注

關注

114文章

5190瀏覽量

214116 -

諧波

+關注

關注

7文章

826瀏覽量

41806

發布評論請先 登錄

相關推薦

四通道相控陣PWM DAC電路解析

四通道相控陣PWM DAC電路解析

評論