今天看《集成電路時序分析與建模》中看到這么一個知識點,覺得有點意思,就記錄下來,與大家一起分享。

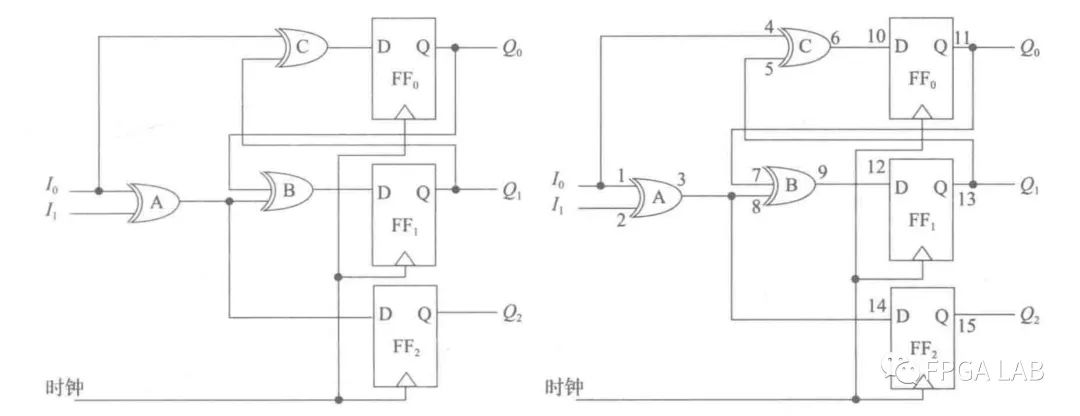

先看 如下電路圖:

左邊的電路圖是需要分析的電路,我們的目的是要對此電路進行時序分析,那首先要找到該電路需要分析的時序路徑,既然找路徑,那找到時序分析的起點與終點即可。

尋找時序路徑的起點和終點的原則如下:

起點:

設計邊界的數據輸入端口或信號輸入端口;如上圖右邊的I0,I1;

時序元件(一般指DFF)的輸出,例如上圖右邊的11,13,15;

存儲單元的數據輸出,其實這和第2條一致,時序單元也是存儲單元,例如DFF,但這里的存儲單元一般指存儲器,例如RAM等;

終點:

時序單元的數據輸入,例如上圖右邊的10,12,14;

存儲單元的數據輸入,類似于時序單元,但更多指存儲器等,例如RAM等;

設計邊界的輸出Q0,Q1,Q2;

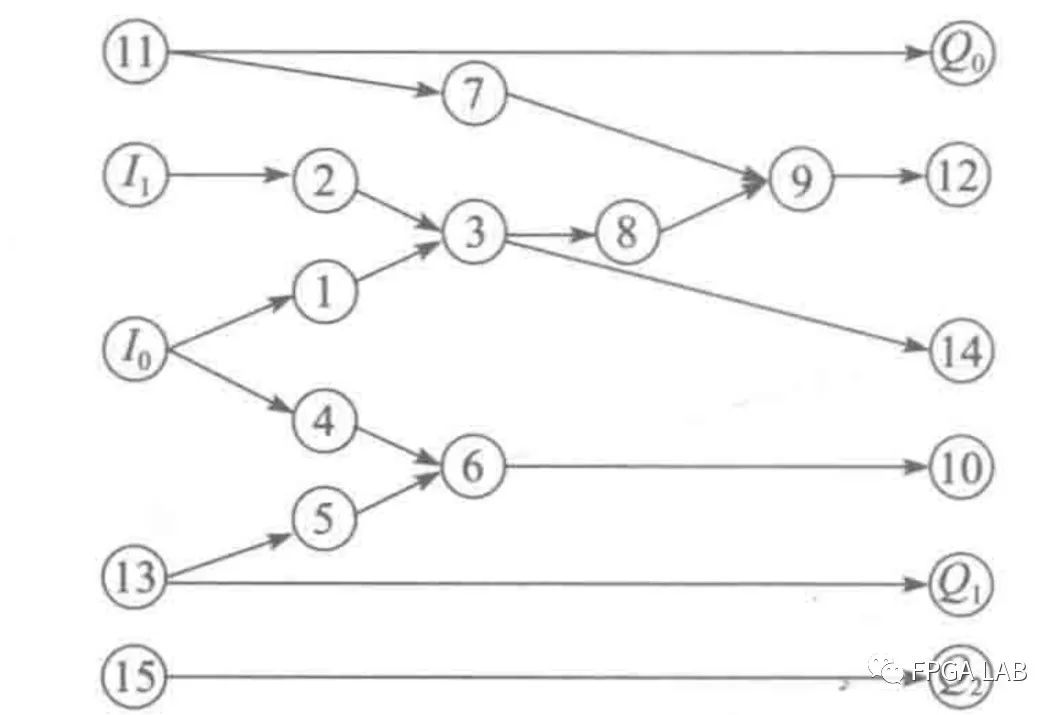

根據上述原則即可得到,時序分析的起點(最左邊)和終點(最右邊):

時序路徑

中間經過的節點都可認為是延遲單元。

實際進行時序分析時,可不必每次都這么轉換,但是不得不說,這種理論化的方式可以讓你的分析更具理論支撐,見多了熟悉了之后便可更快速的識別時序路徑。這是分析的第一步,祝入門快樂。

審核編輯 :李倩

-

集成電路

+關注

關注

5387文章

11530瀏覽量

361632 -

時序

+關注

關注

5文章

387瀏覽量

37318

原文標題:【靜態時序分析】如何尋找時序路徑的起點與終點

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

億緯鋰能榮獲雙項起點金鼎獎

使用霍爾效應傳感器針對篡改和移動終點位置檢測實現限制檢測

鎖存器的基本輸出時序

起點,經過點,終點,三點xyz,畫三維圓弧。

電源時序器的原理及使用方法是什么

FPGA 高級設計:時序分析和收斂

Xilinx FPGA編程技巧之常用時序約束詳解

FPGA工程的時序約束實踐案例

Xilinx FPGA編程技巧之常用時序約束詳解

#新開端、新起點,2024一起加油#

時序電路的分類 時序電路的基本單元電路有哪些

時序電路包括兩種類型 時序電路必然存在狀態循環對不對

為刻蝕終點探測進行原位測量

FPGA設計的常用基本時序路徑分析

如何尋找時序路徑的起點與終點

如何尋找時序路徑的起點與終點

評論