DDR5 系統管理引入了一種全新的邊帶總線,其正式名稱為 JESD403-1 JEDEC 模塊邊帶總線。 DDR5 標準的開發正由 JEDEC 和 MIPI 聯盟合作進行。

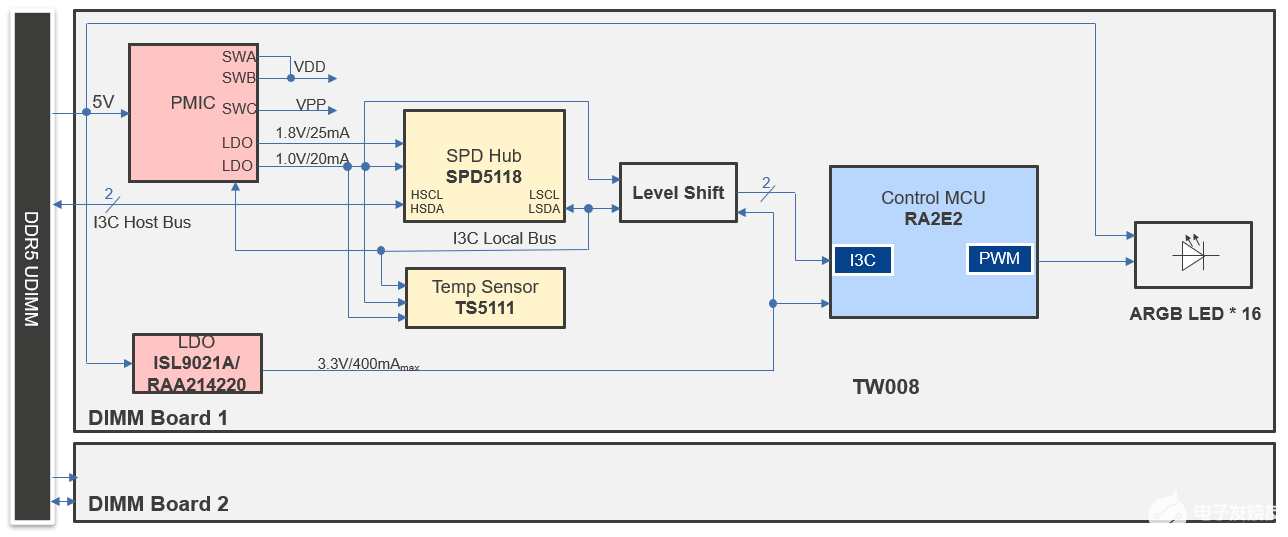

在引入這種全新應用的情況下,該應用所用到的 SPD 集線器、PMIC 和微控制器需要在確保協議合規性的基礎上實現高度集成。 因此,瑞薩開發了一種結合瑞薩 SPD5 集線器 SPD5118、瑞薩 PMIC、溫度傳感器和新款瑞薩 RA RA2E2 組的解決方案,以實現符合 JEDEC JESD403 和 MIPI I3C BasicSM 要求的邊帶總線操作。 另一方面,這些關鍵的瑞薩設備已通過 MIPI I3C BasicSM 的全面認證,并且該系統還能夠向后兼容舊版 JEDEC I2C 實施。

DDR5 DIMM 邊帶總線和主機總線的簡要架構

瑞薩 DDR5 解決方案附帶原型套件,可配合上述的總線和電源布局架構使用,并在 RA I3C 總線的前端采用了電平移動電路,以滿足 JESD403-1 的特定總線電壓要求。 客戶可以通過他們的 SDRAM 模塊充分利用此集成套件,從而加速產品發布計劃。

管理總線協議

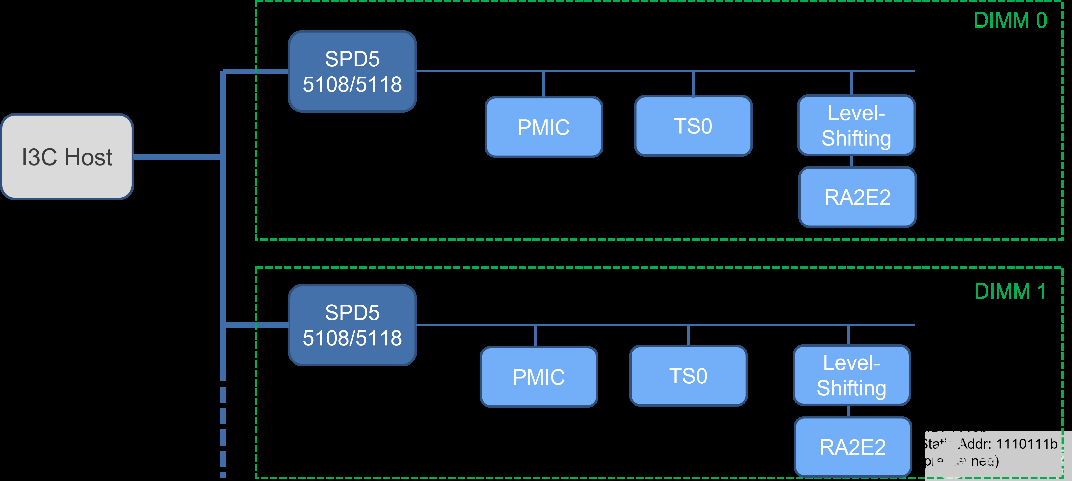

邊帶總線采用特定的結構化尋址方案(如下文簡述)來識別 DIMM 以及 DIMM 上的設備。 因此,I3C 基礎的 ENTDAA 和基于 PID 的地址計算方案并不需要強制執行。 基于此情況,SPD 集線器通過兩個模式處理地址計算和 HID 分配,而 DIMM 上能夠以 I3C 基礎模式運行的設備應為 JEDEC SETHID CCC 和 SETAASA CCC 提供支持。

在 JEDEC I2C 模式中(默認通電),通信(以 DIMM 上的設備為目標從屬設備)由主機發出啟動條件開始,后接 7 位從屬地址和一個讀/寫字位。 通信過程中,作為首個接收器的 SPD 集線器將替換尋址 DIMM 的從屬地址的 LSB 3bits(HID)并轉發到本地總線,不包括 0x7E 的廣播地址。 SPD 集線器借助精密電阻檢測 HID/DIMM_ID 并輔助 HID 分配。

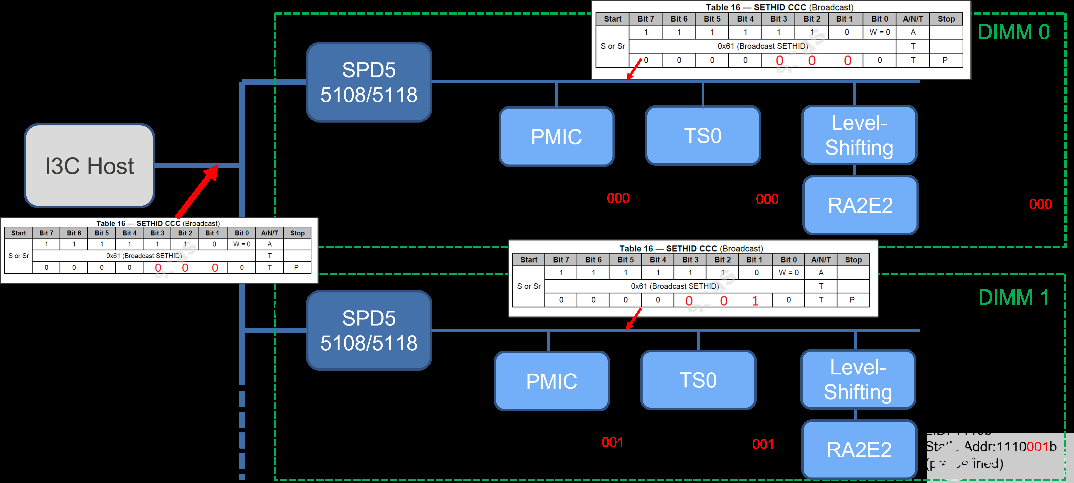

JEDEC I3C 模式將一直生效,直至作為邊帶總線上首個接收器的 SPD 集線器接收到 JEDEC SETHID CCC 為止。 一旦集線器檢測到 JEDEC SEHID CCC,集線器便會停止 HID 數位翻轉,并將傳入的 7 位從站地址按原樣透明地傳送到本地總線中。 在此操作之后,DIMM 上所有從 SPD 集線器接收 SETHID CCC 的 I3C 設備應更新其靜態地址分配,并等待 SETAASA CCC 完成地址分配以進入 I3C 基礎操作。

下圖對上述兩種模式的操作說明進行了匯總。

在收到 JEDEC SETHID CCC 之前,I2C 模式默認通電。

接收到 JEDEC SETHID CCC 時進入 I3C 模式。

RA2E2 組包含全面通過 MIPI I3C BasicSM 認證的 I3C 接口,可向后兼容舊版 JEDEC I2C 實施,設計師能夠簡化硬件設計,同時輕松而順暢地實現從舊版 I2C 平臺到 I3C 平臺的轉移。

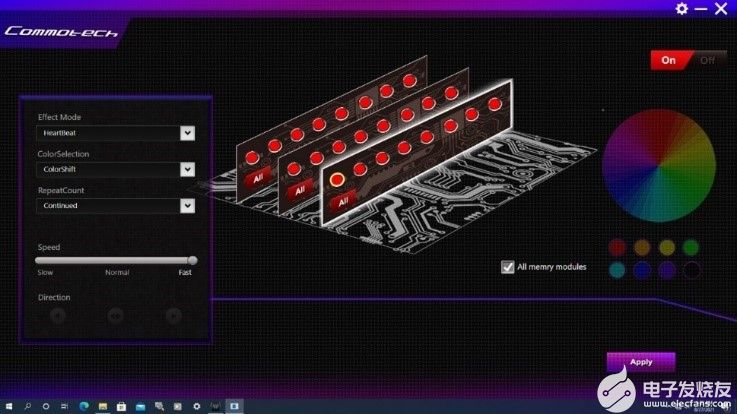

DDR5 ARGB LED 控制實施

RA2E2 組在尺寸僅為 4.00 x 4.00mm 的 24 引腳 HW 四方扁平無引腳 (HWQFN) 封裝中提供 6 通道的通用 PWM 定時器。 借助硬件支持,可以通過最大化可控 ARGB LED 陣列的數量來拓展照明效果的選項。

演示和驗證

作為 MIPI 聯盟的成員和較早采用 MIPI I3C Basic SM 和 JEDEC JESD 403-1 的先行者,瑞薩解決方案的邊帶總線運行和協議合規性驗證已通過 Prodigy I3C協議分析器和模擬器完成,可支持 MIPI I3C Basic V1.0, V1.1 規格。 此外,瑞薩解決方案能夠向后兼容 SM 總線,以滿足英特爾目前對 LED 照明控制的 DDR4 和 DDR5 結構要求,而瑞薩的第三方合作商也將提供包括 H/W、F/W 和 S/W 在內的全套解決方案,從而改善整體開發環境。

審核編輯:郭婷

-

英特爾

+關注

關注

61文章

9984瀏覽量

171952 -

模擬器

+關注

關注

2文章

879瀏覽量

43273 -

DDR5

+關注

關注

1文章

426瀏覽量

24161

發布評論請先 登錄

相關推薦

【RA-Eco-RA4E2-64PIN-V1.0開發板試用】+03+UART+控制舵機+控制LED

DDR5內存的工作原理詳解 DDR5和DDR4的主要區別

Rambus推出DDR5客戶端時鐘驅動器,將業界領先的內存接口芯片產品擴展到高性能 PC領域

Introspect DDR5/LPDDR5總線協議分析儀

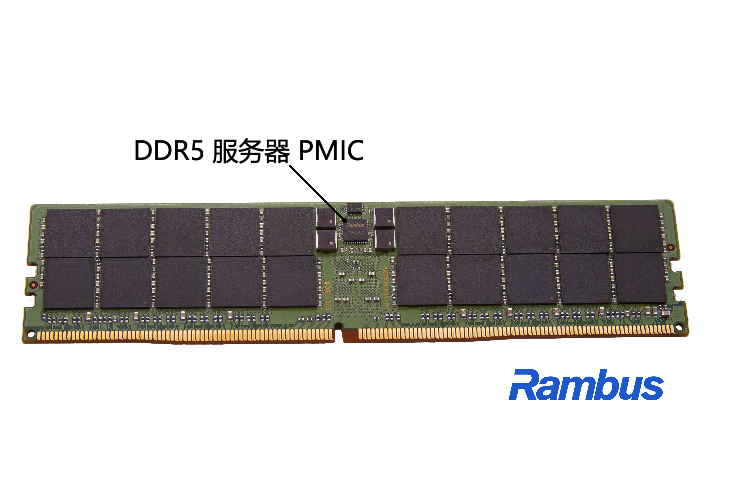

Rambus 通過 DDR5 服務器 PMIC 擴展適用于高級數據中心內存模塊的芯片組

適用于DDR5 On-DIMM 電源的TPS53832集成式數字降壓轉換器數據表

適用于DDR5 On-DIMM電源的TPS53830集成式數字降壓轉換器 數據表

適用于DDR5 On-DIMM 電源的TPS53832A集成式數字降壓轉換器數據表

適用于DDR5 On-DIMM 電源的TPS53830A集成式數字降壓轉換器數據表

適用于單節電池的I2C控制型3A降壓電池充電器BQ25622E數據表

DDR5內存接口芯片組如何利用DDR5 for DIMM的優勢?

適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準的TPS51206 2A峰值灌電流/拉電流DDR終端穩壓器數據表

RA2E2單片機組適用于DDR5 DIMM LED的控制應用

RA2E2單片機組適用于DDR5 DIMM LED的控制應用

評論