據(jù)報(bào)道,華為已開發(fā)了(并申請(qǐng)了專利)一種芯片堆疊工藝,該工藝有望比現(xiàn)有的芯片堆疊方法便宜得多。該技術(shù)將幫助華為繼續(xù)使用較老的成熟工藝技術(shù)開發(fā)更快的芯片。 唯一的問(wèn)題是華為是否真的可以利用其創(chuàng)新,因?yàn)闆]有美國(guó)政府的出口許可證,代工廠無(wú)法為該公司生產(chǎn)芯片。但至少華為自己當(dāng)然相信它可以,特別是考慮到這項(xiàng)技術(shù)可以為基于不受美國(guó)如此嚴(yán)厲限制的舊節(jié)點(diǎn)的芯片提供性能提升。

保持競(jìng)爭(zhēng)力的一種方式

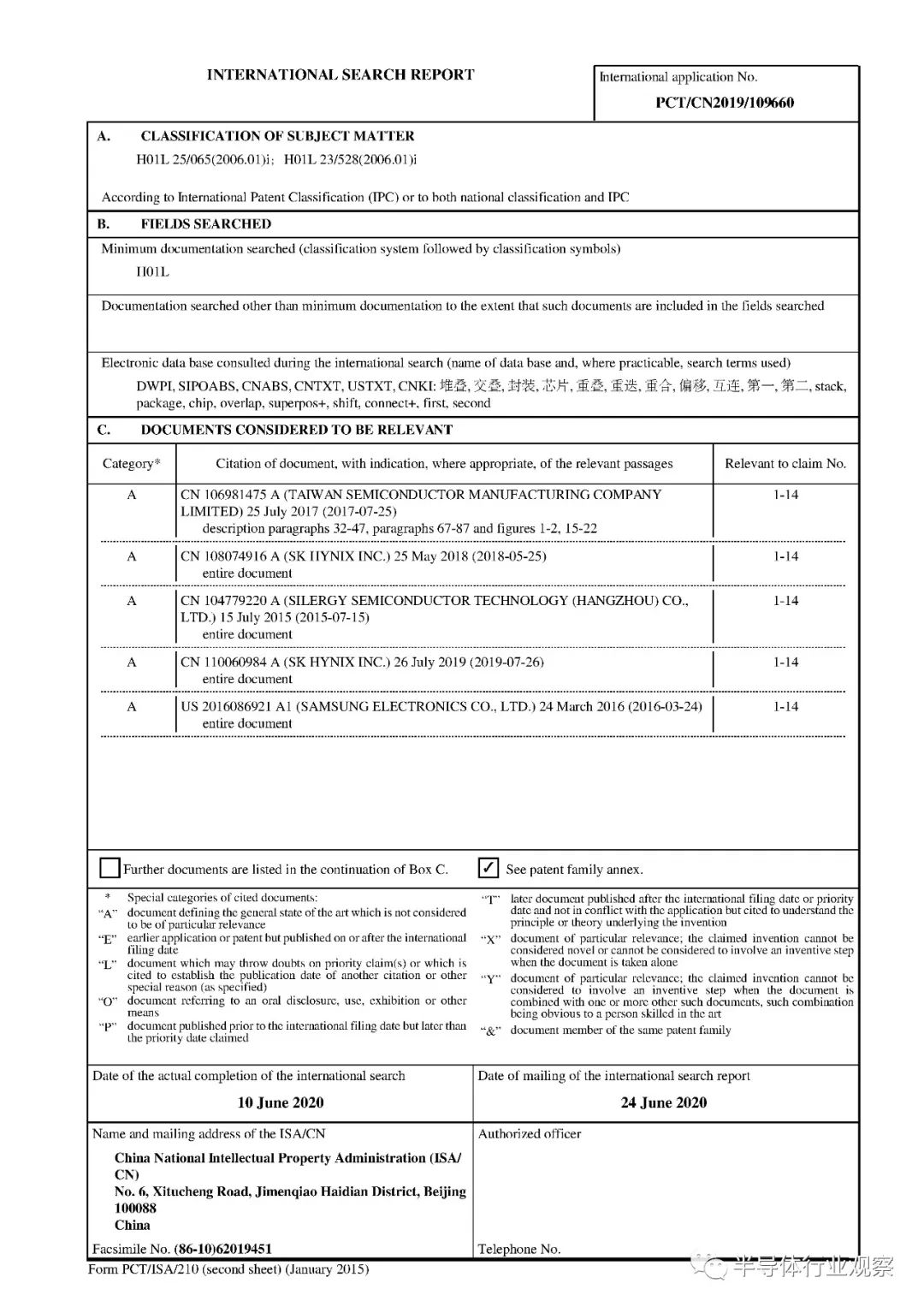

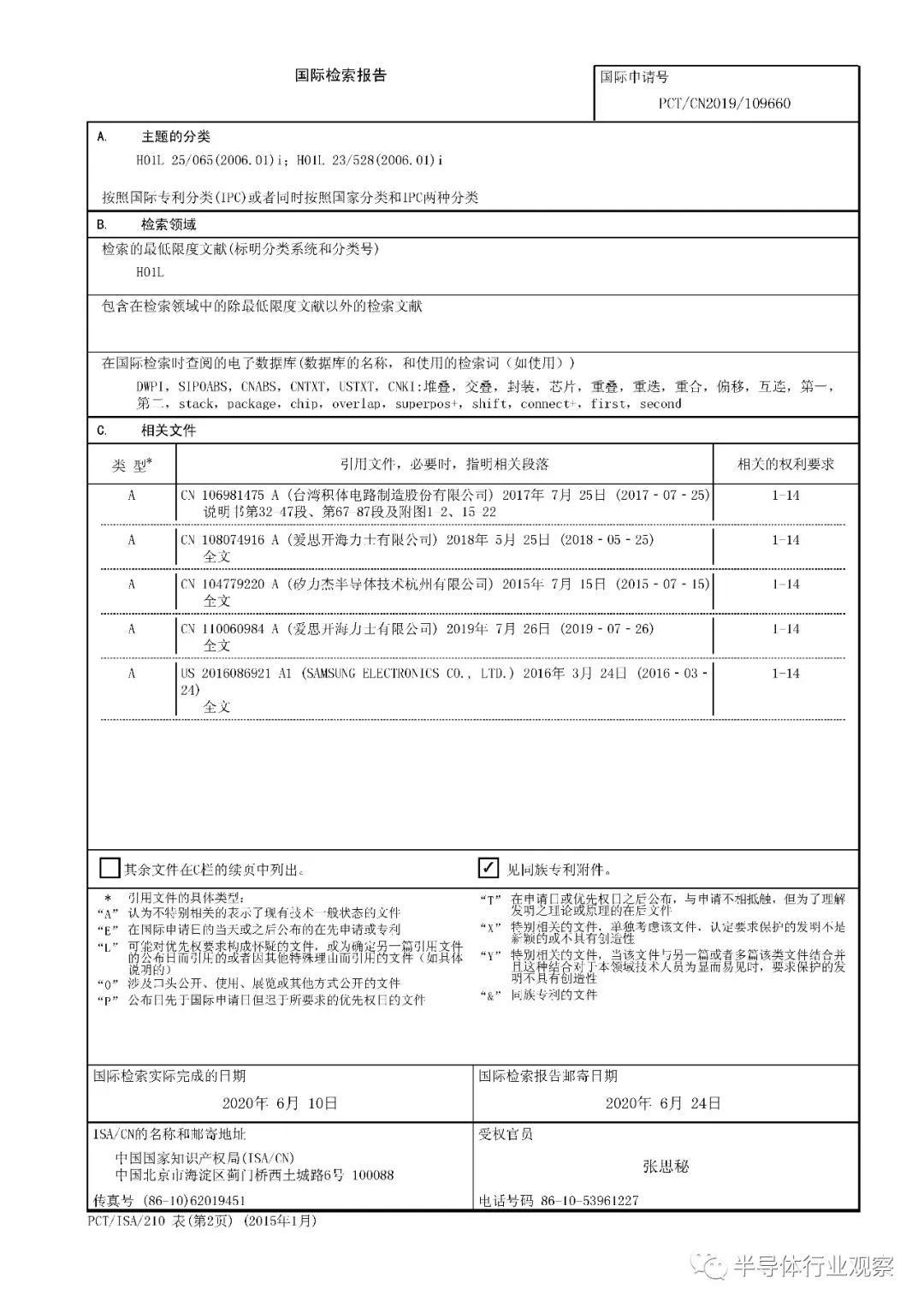

我們將在下面詳細(xì)介紹這項(xiàng)新技術(shù),但重要的是要了解華為為什么要開發(fā)這項(xiàng)新技術(shù)。 由于美國(guó)政府將華為及其芯片設(shè)計(jì)子公司海思列入黑名單,現(xiàn)在要求所有制造芯片的公司申請(qǐng)出口許可證,因?yàn)樗?a target="_blank">半導(dǎo)體生產(chǎn)都涉及美國(guó)開發(fā)的技術(shù),華為無(wú)法進(jìn)入任何先進(jìn)節(jié)點(diǎn)(例如臺(tái)積電的N5),因此必須依賴成熟的工藝技術(shù)。 為此,華為前任總裁郭平表示,創(chuàng)新的芯片封裝和小芯片互連技術(shù),尤其是 3D 堆疊,是公司在其 SoC 中投入更多晶體管并獲得競(jìng)爭(zhēng)力所需性能的一種方式。因此,該公司投資于專有的封裝和互連方法(例如其獲得專利的方法)是非常有意義的。 “以 3D 混合鍵合技術(shù)為代表的微納米技術(shù)將成為擴(kuò)展摩爾定律的主要手段,”郭說(shuō)。 華為高層表示,由于現(xiàn)代領(lǐng)先的制程技術(shù)進(jìn)展相對(duì)緩慢,2.5D或3D封裝的多芯片設(shè)計(jì)是芯片設(shè)計(jì)人員不斷在產(chǎn)品中投入更多晶體管,以滿足他們客戶在新功能和性能的預(yù)期,這也成為了產(chǎn)業(yè)界采用的一個(gè)普遍方式。因此,華為前董事長(zhǎng)強(qiáng)調(diào),華為將繼續(xù)投資于內(nèi)部設(shè)計(jì)的面積增強(qiáng)和堆疊技術(shù)。 華為在新聞發(fā)布會(huì)上公開發(fā)表的聲明清楚地表明,公司旨在為其即將推出的產(chǎn)品使用其混合無(wú) TSV 3D 堆疊方法(或者可能是類似且更主流的方法)。主要問(wèn)題是該方法是否需要美國(guó)政府可能認(rèn)為最先進(jìn)且不授予出口許可證的任何工具或技術(shù)(畢竟,大多數(shù)晶圓廠工具使用源自美國(guó)的技術(shù))。也就是說(shuō),我們是否會(huì)看到一家代工廠使用華為的專利方法為華為制造 3D 小芯片封裝,這還有待觀察。但至少華為擁有一項(xiàng)獨(dú)特的廉價(jià) 3D 堆疊技術(shù),即使無(wú)法使用最新節(jié)點(diǎn),也可以幫助其保持競(jìng)爭(zhēng)力。

無(wú)過(guò)孔堆疊

創(chuàng)新的芯片封裝和多芯片互連技術(shù)將在未來(lái)幾年成為領(lǐng)先處理器的關(guān)鍵,因此所有主要芯片開發(fā)商和制造商現(xiàn)在都擁有自己專有的芯片封裝和互連方法。

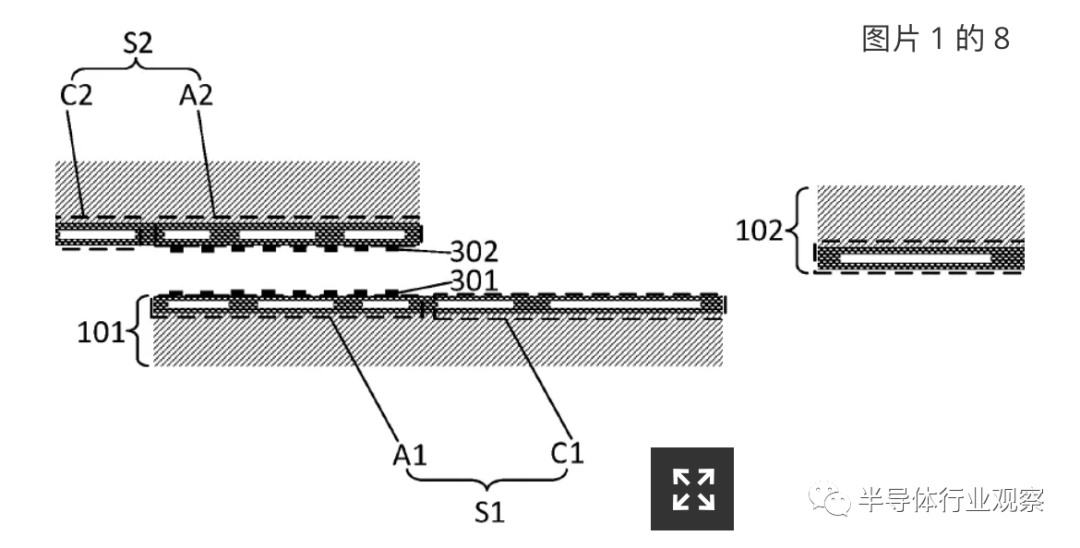

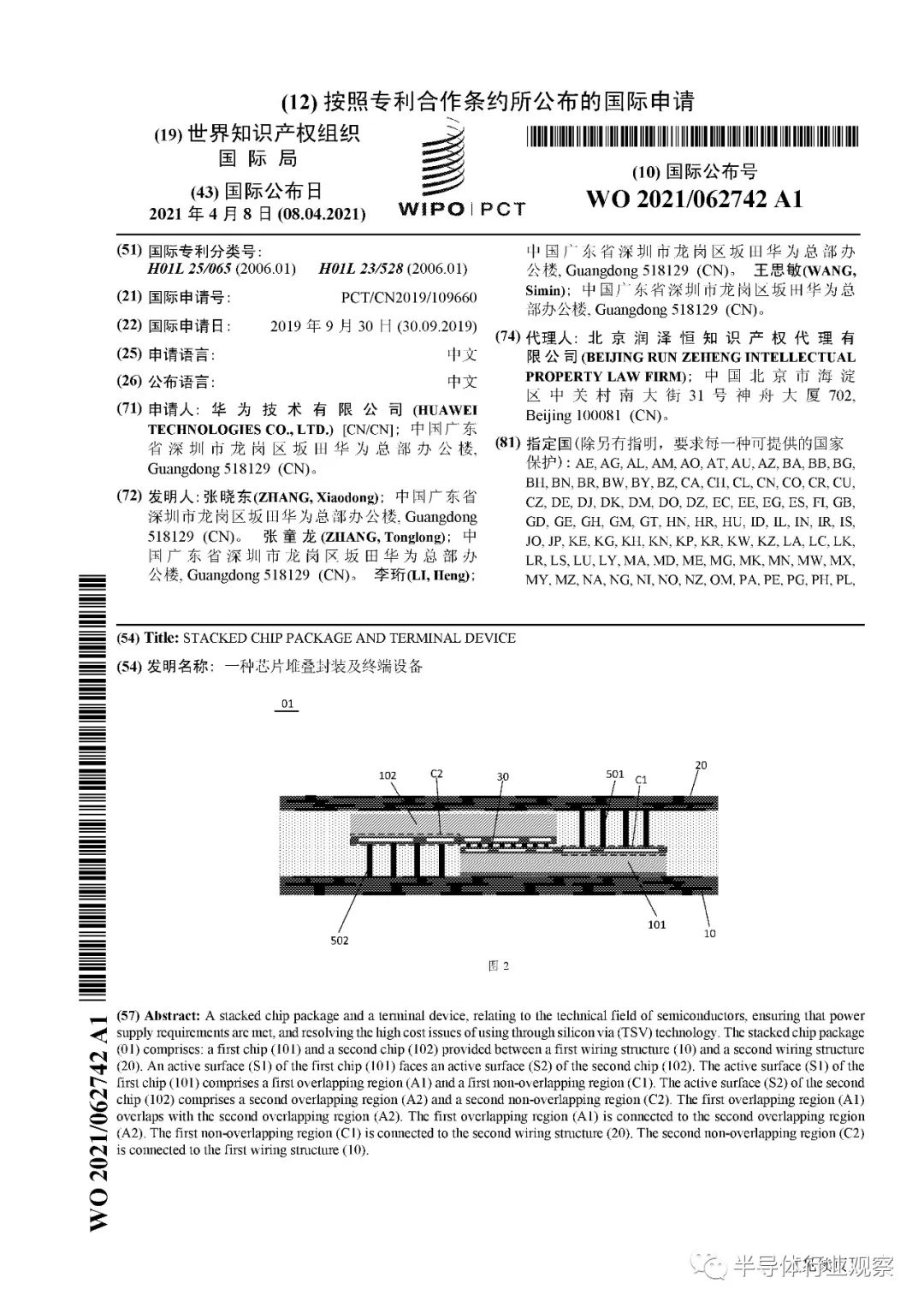

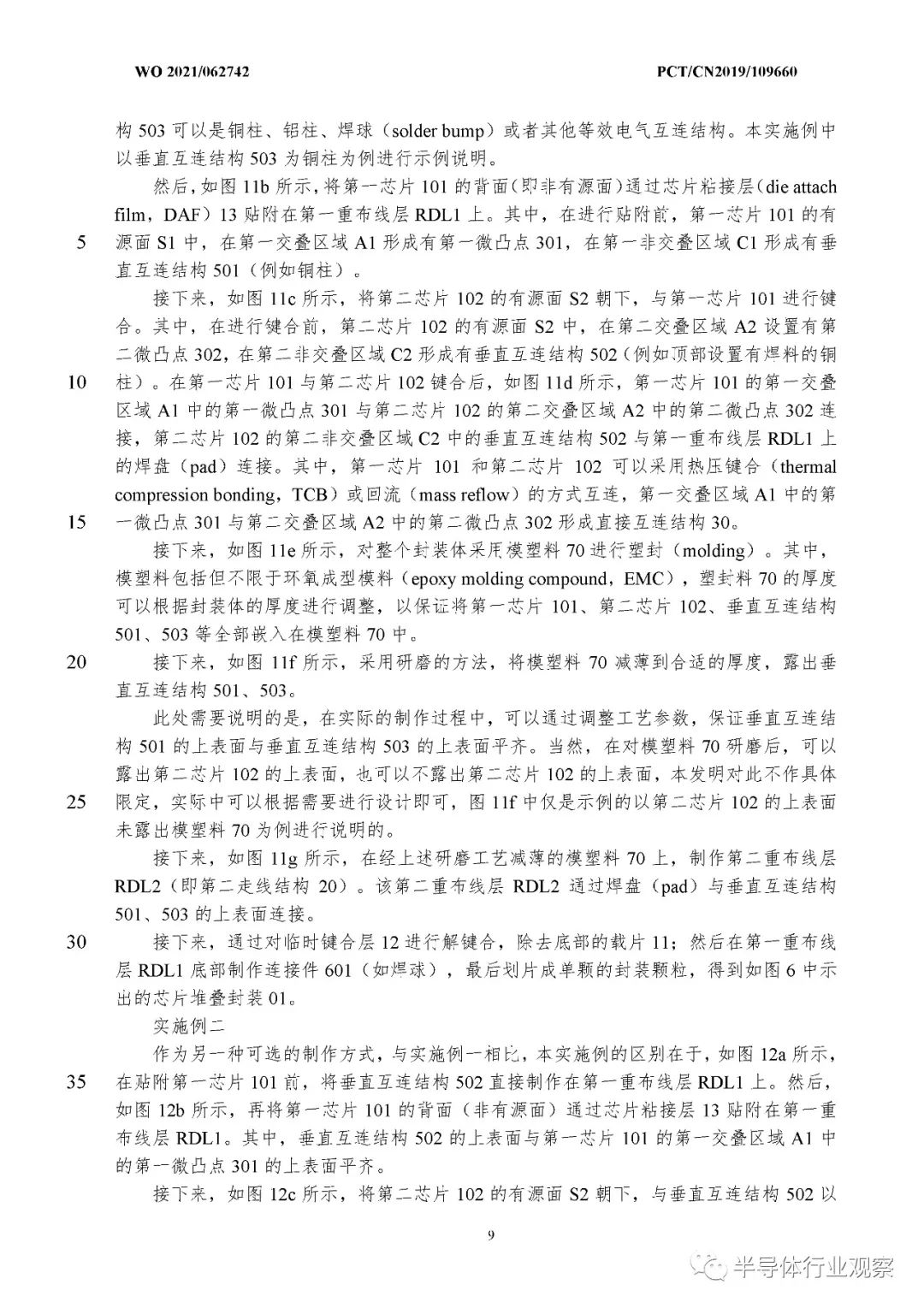

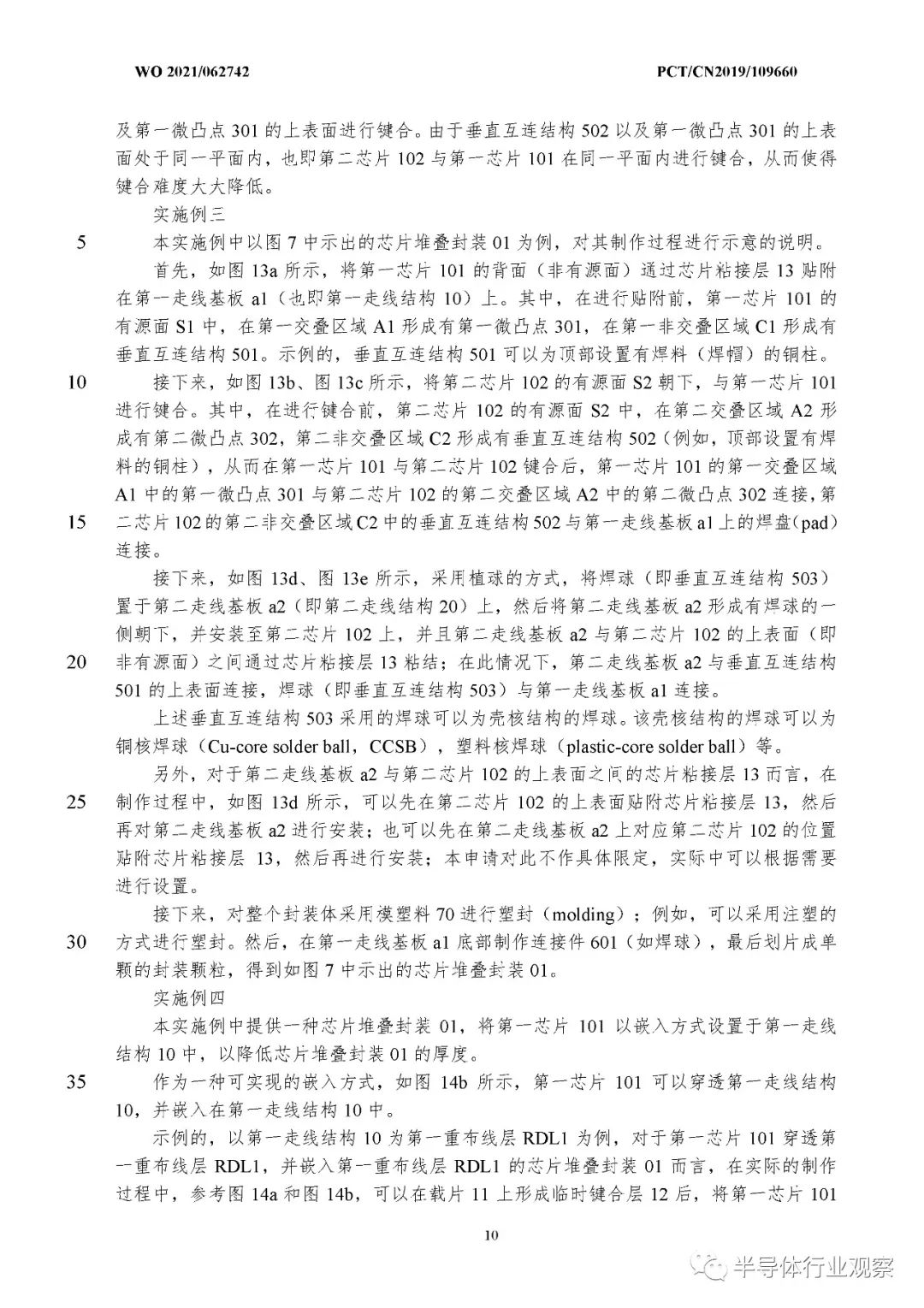

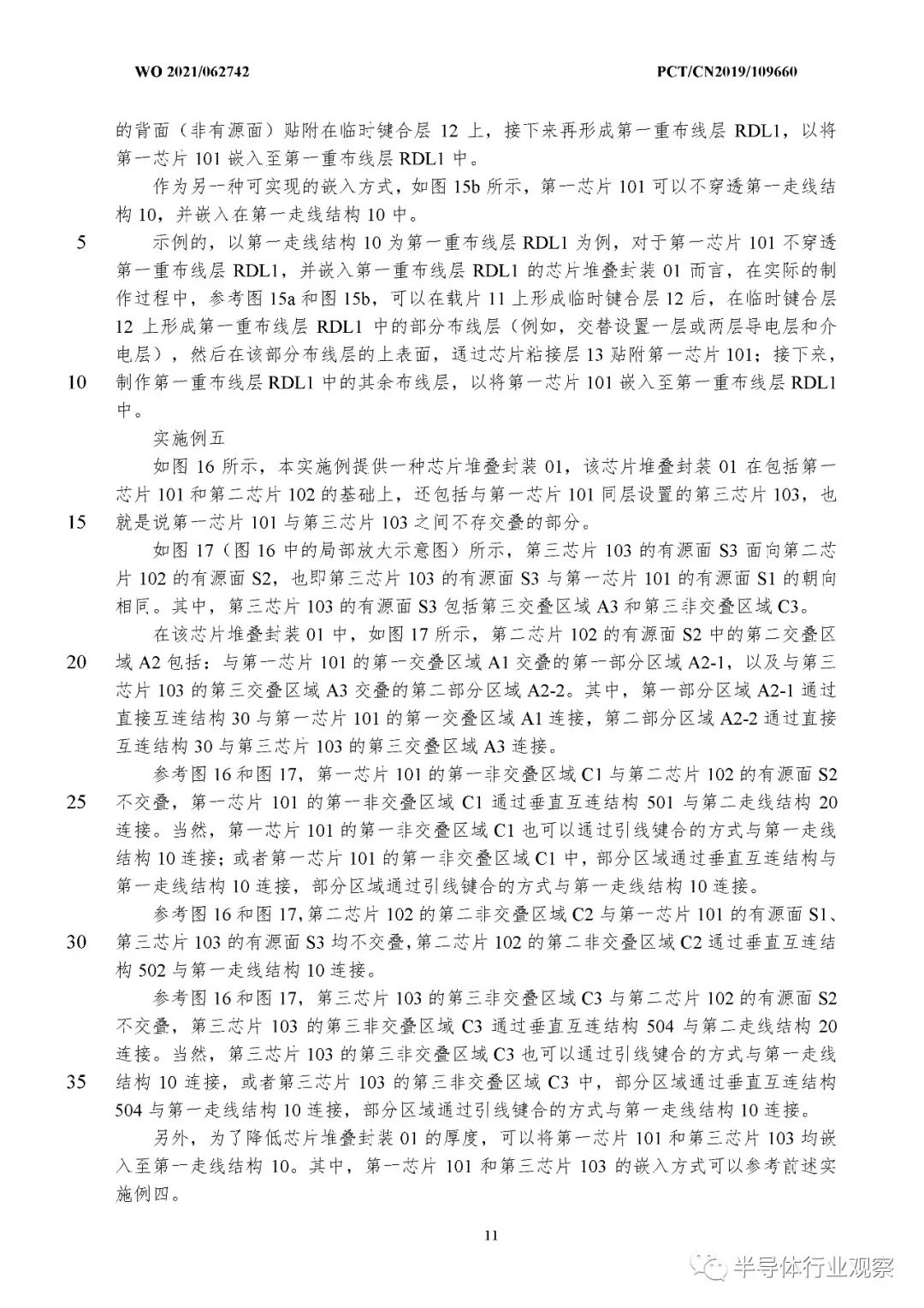

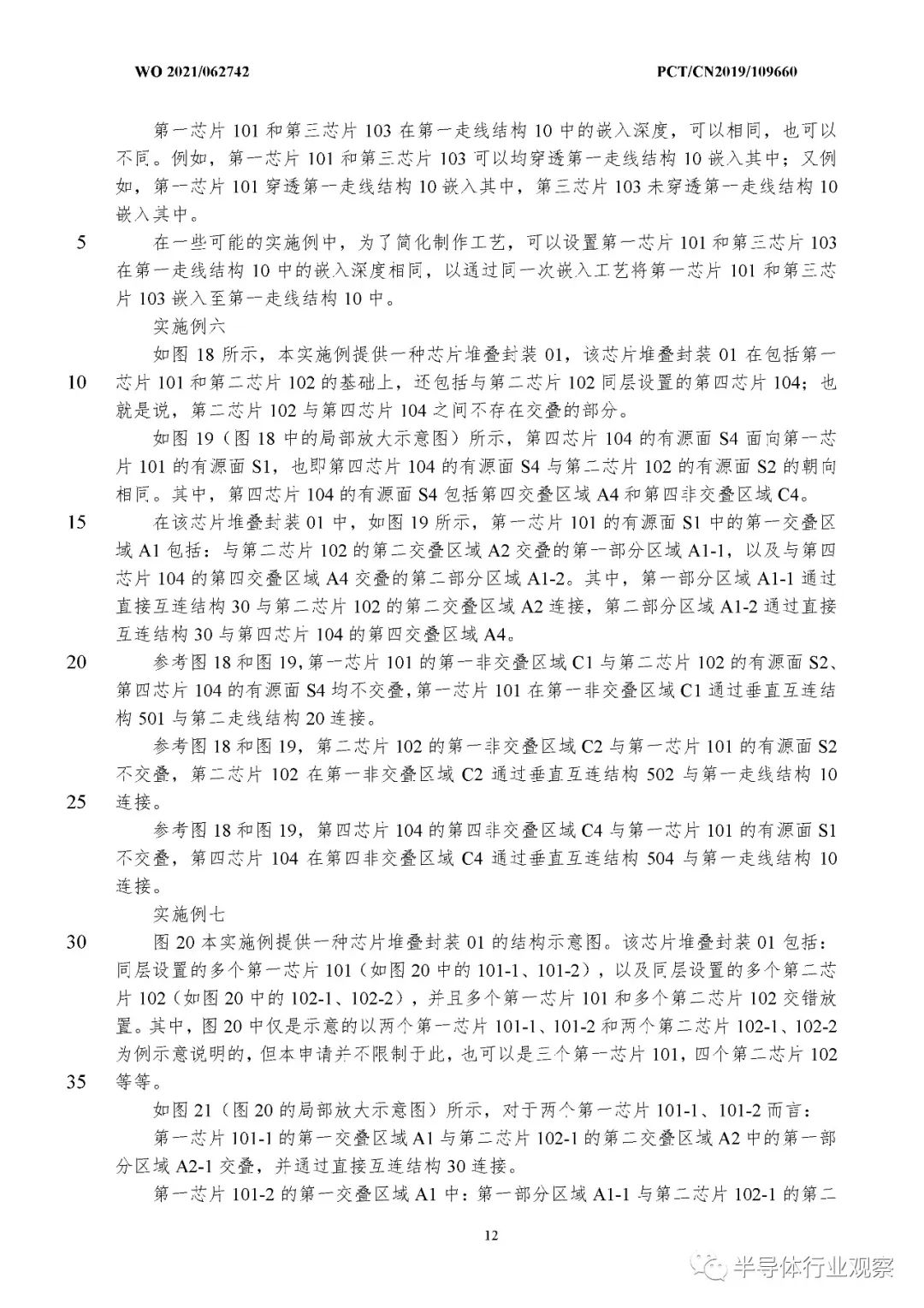

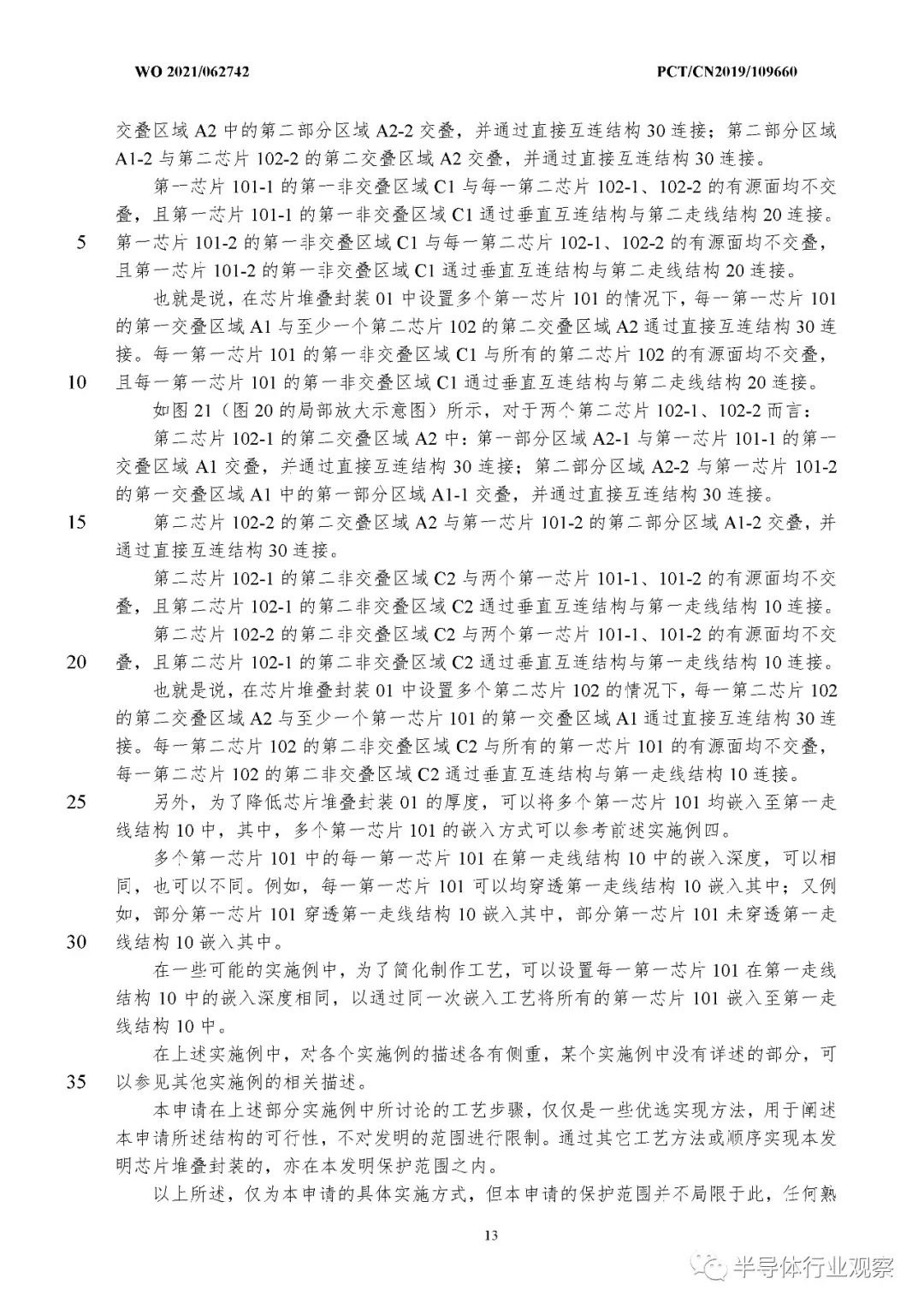

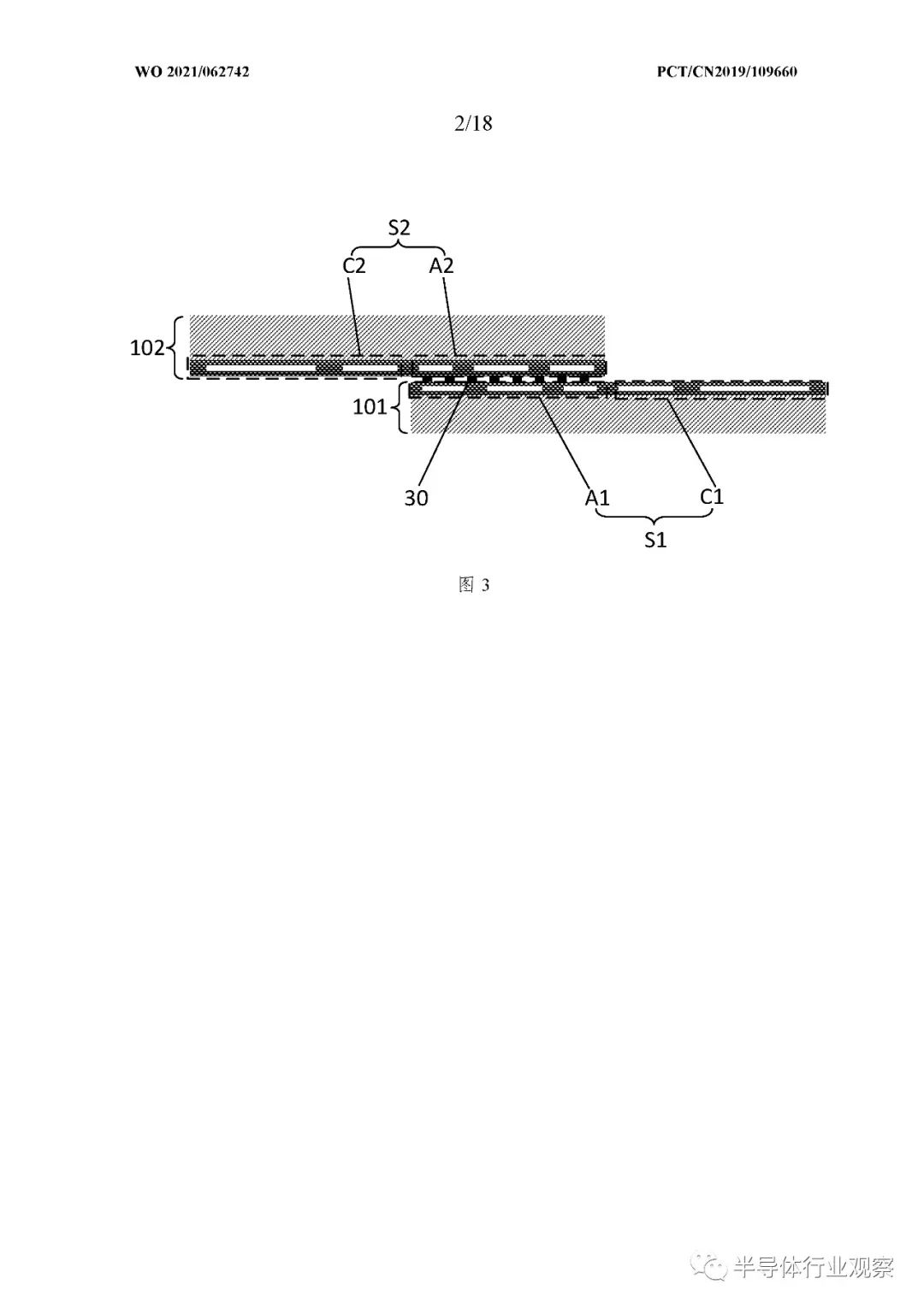

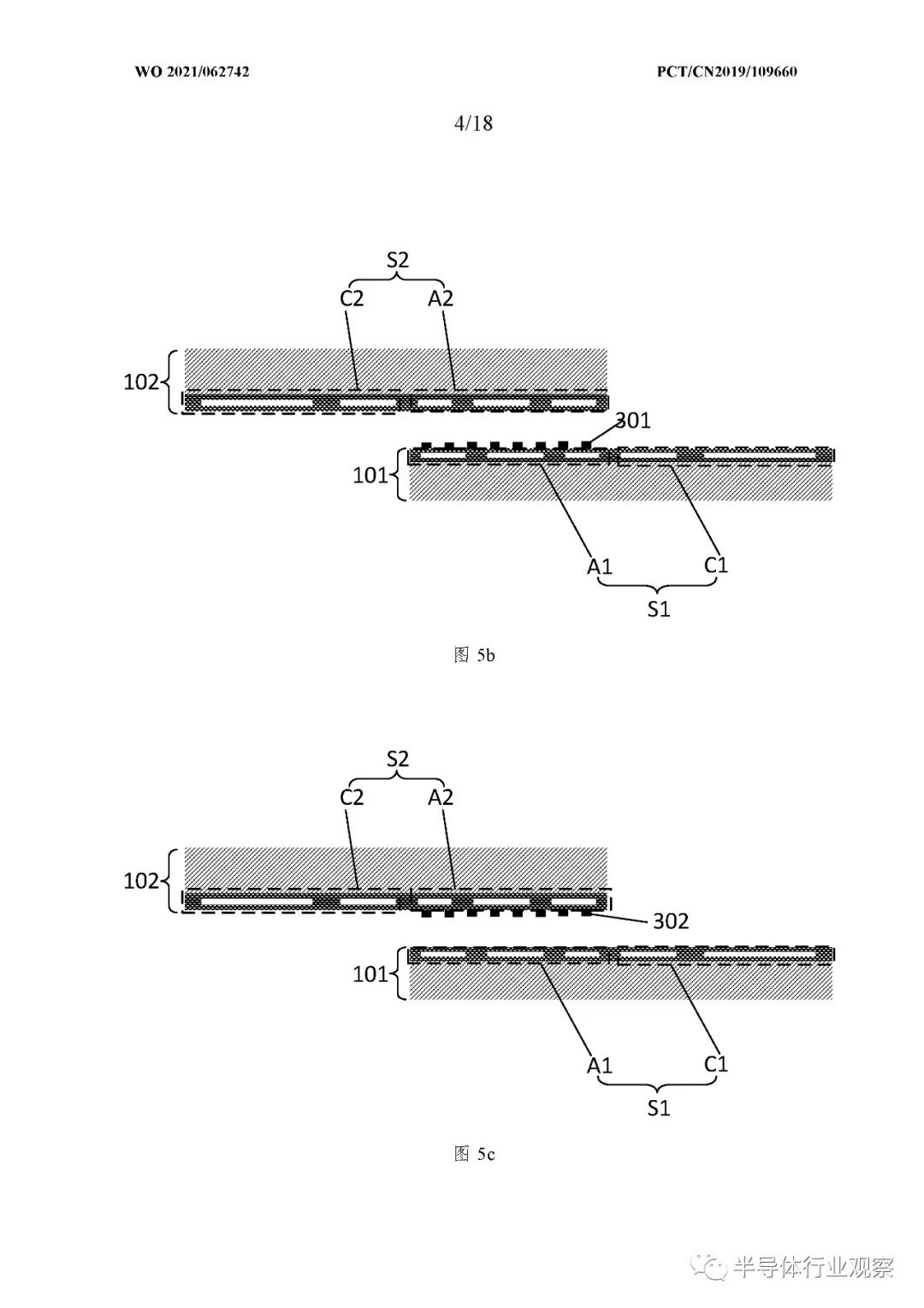

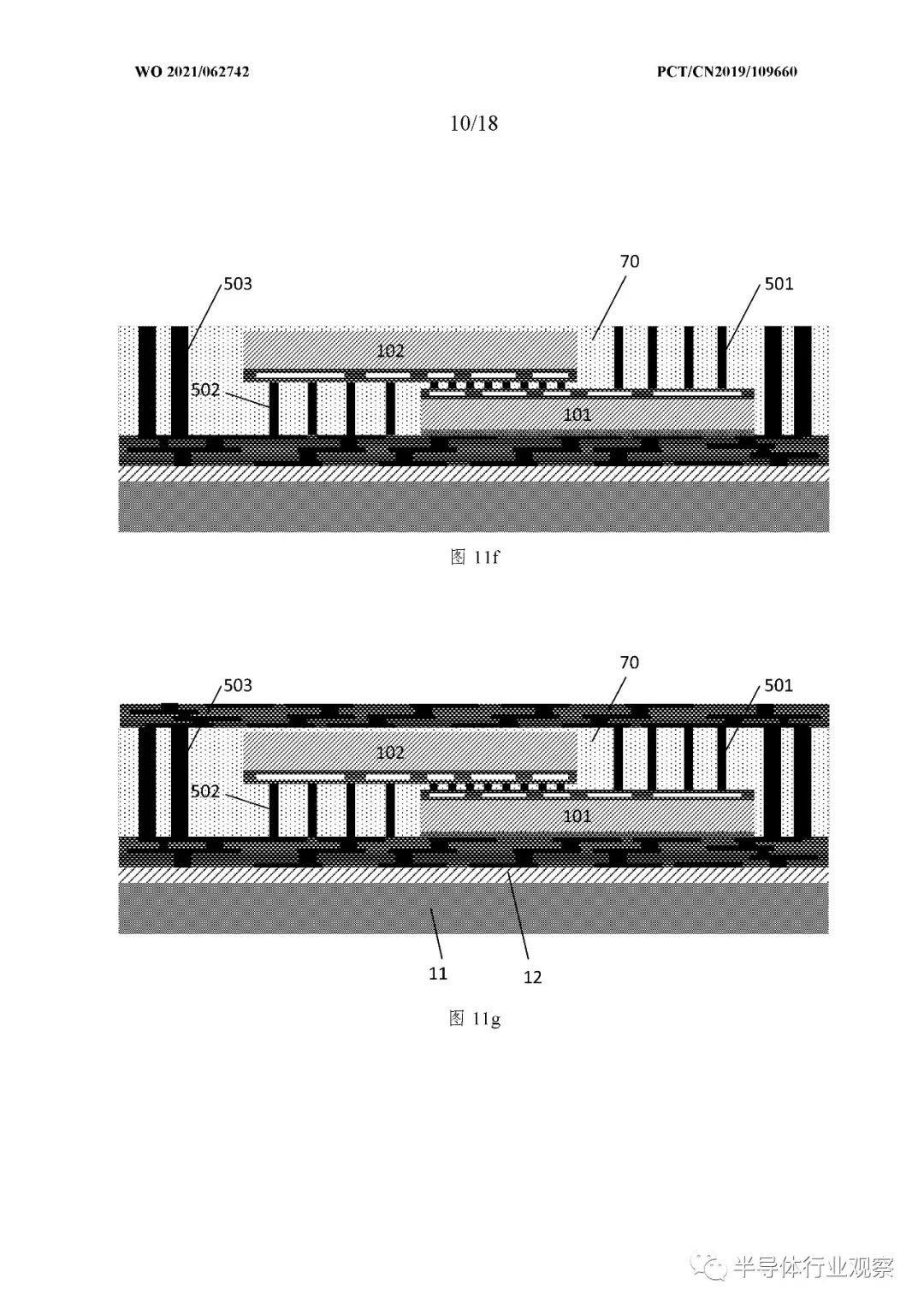

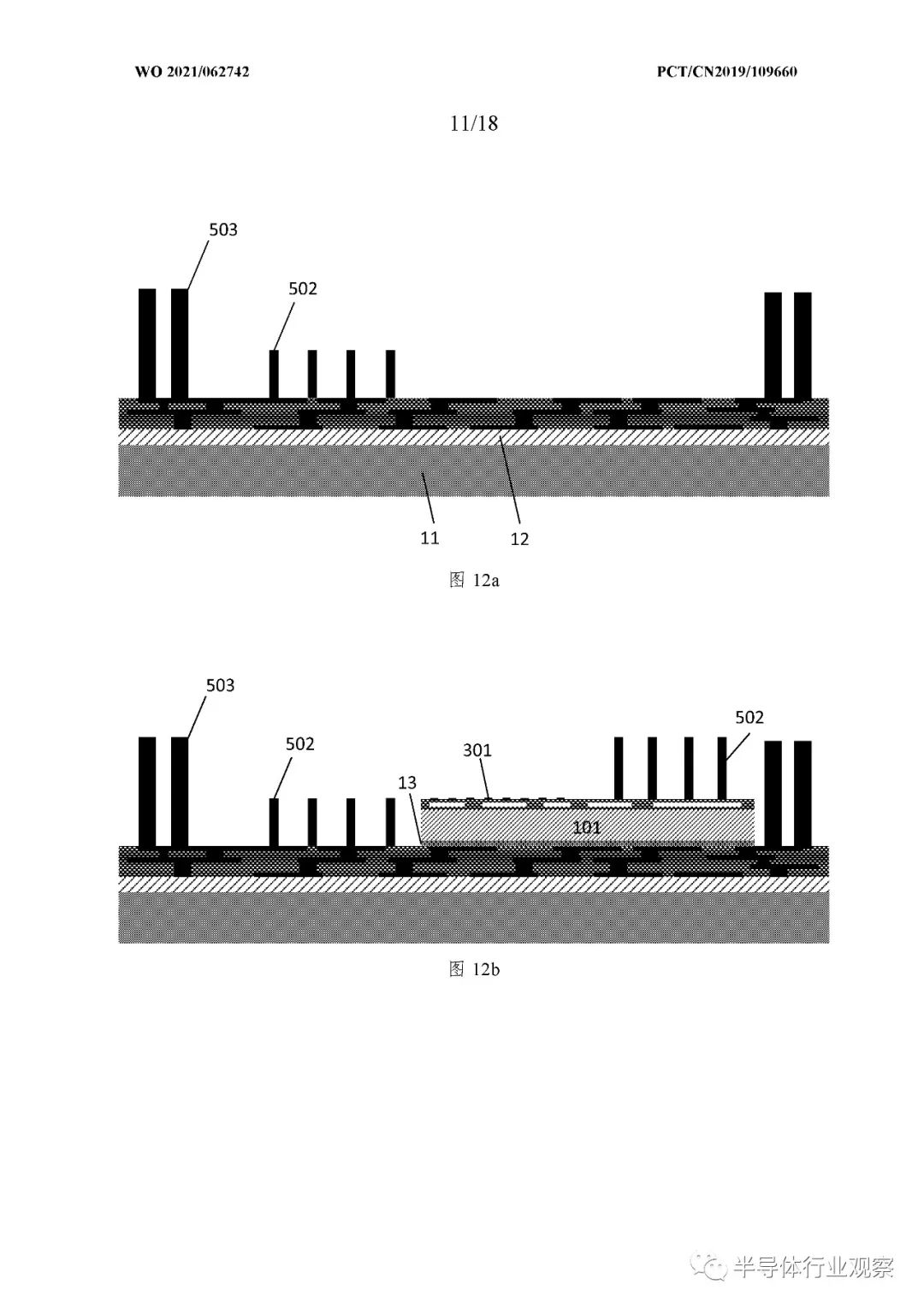

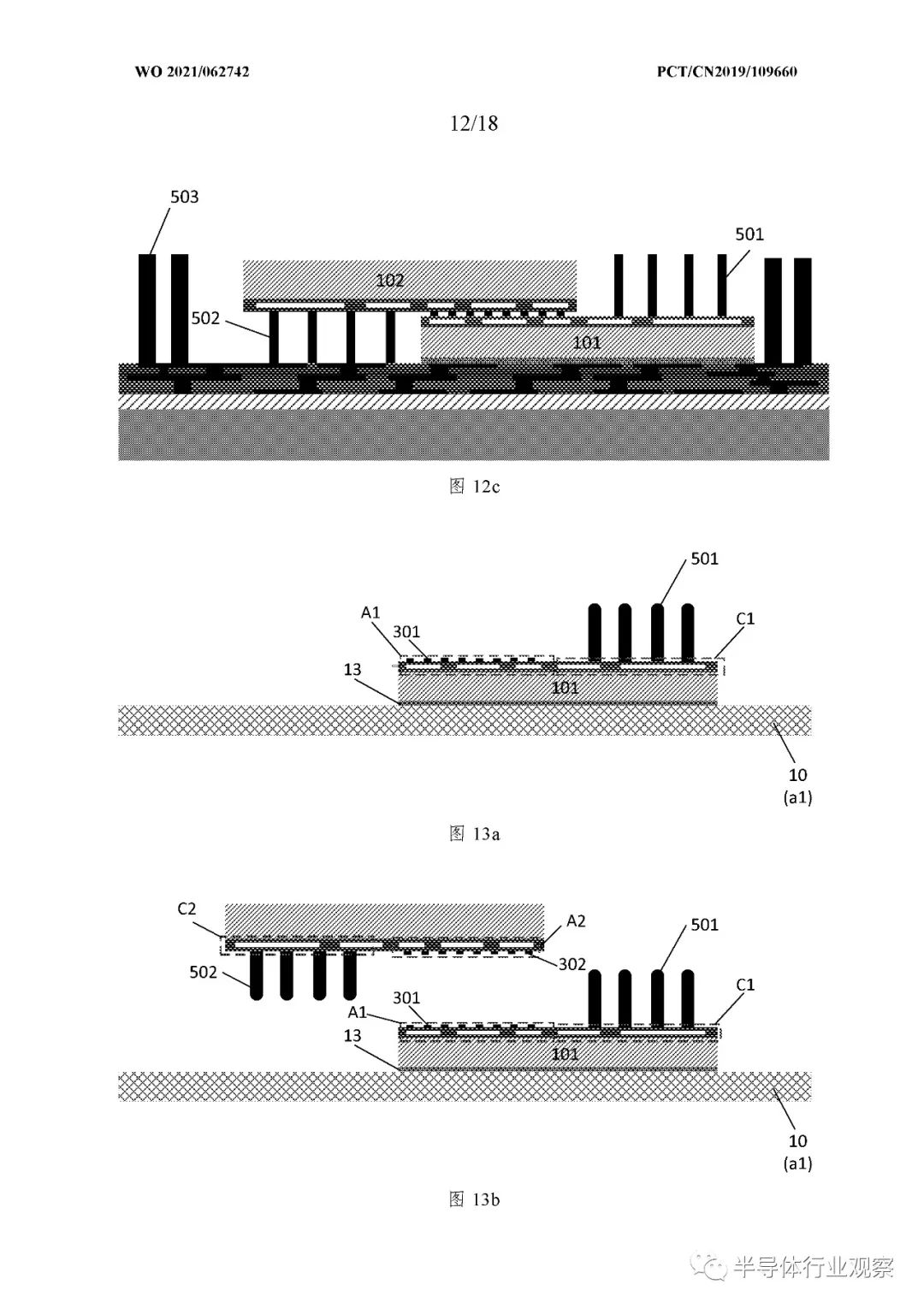

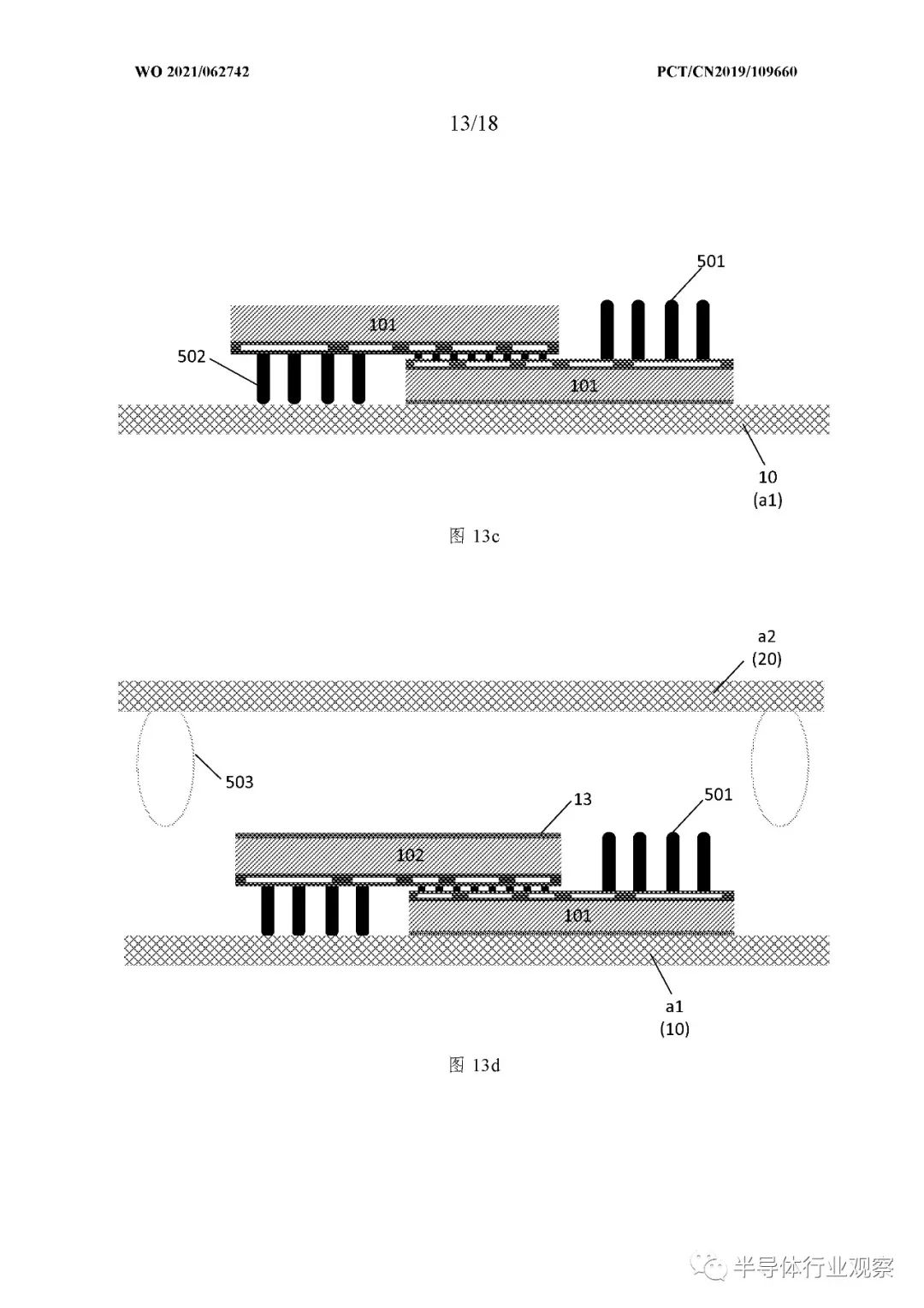

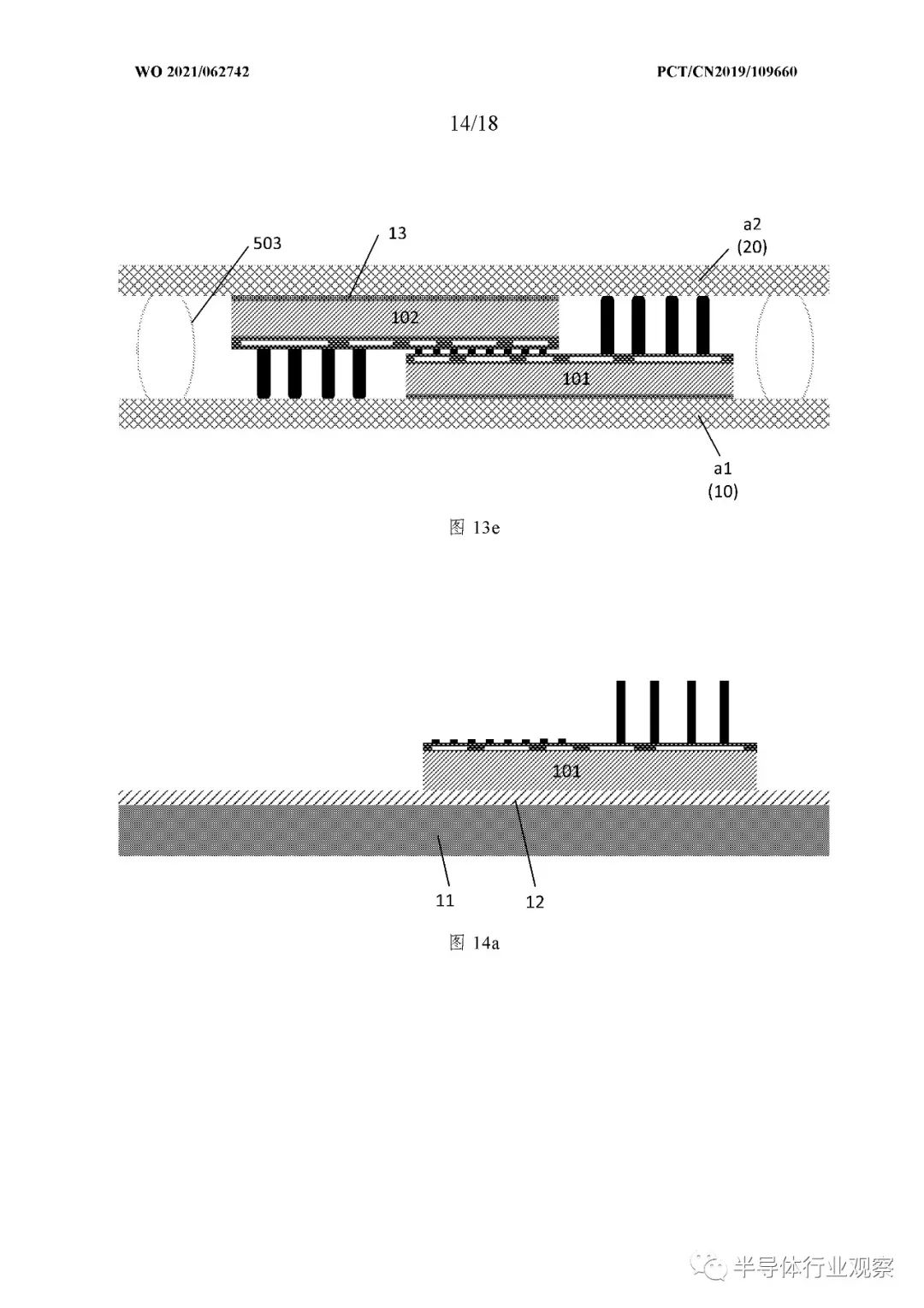

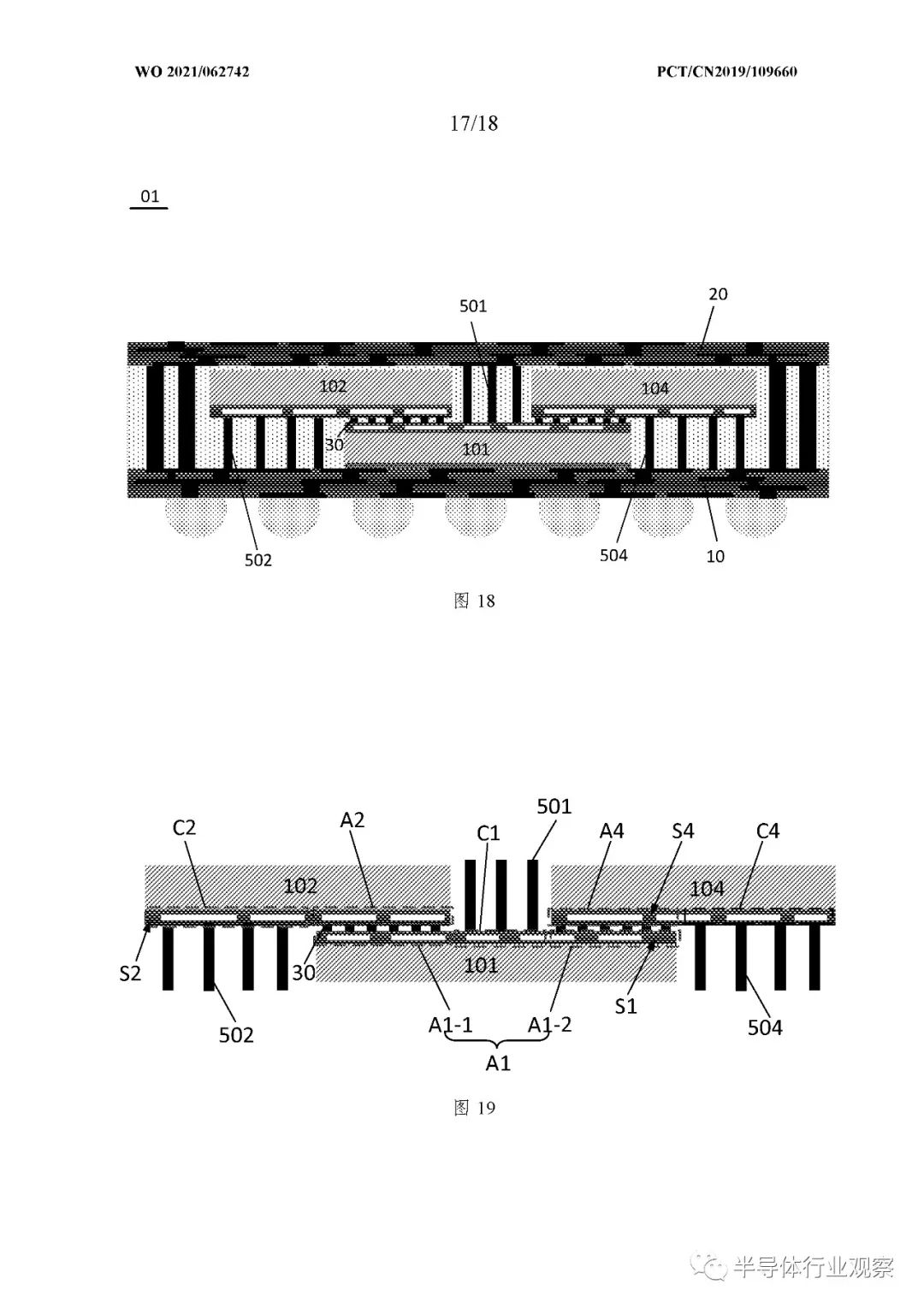

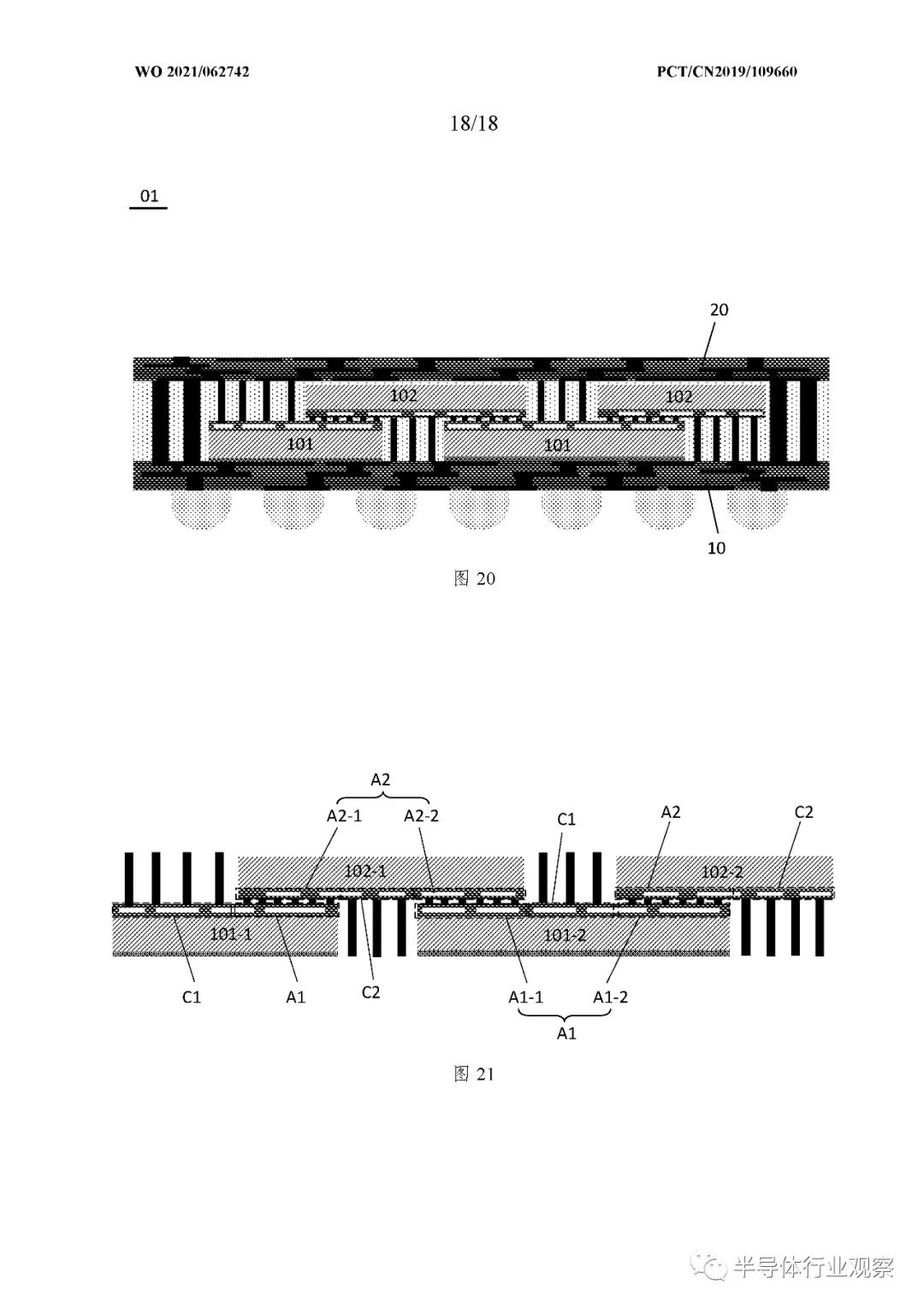

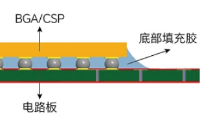

芯片制造商通常使用兩種封裝和互連方法:2.5D 封裝為彼此相鄰的小芯片實(shí)現(xiàn)高密度/高帶寬的封裝內(nèi)互連,3D 封裝通過(guò)將不同的小芯片堆疊在一起使處理器更小. 然而,3D 封裝通常需要相當(dāng)復(fù)雜的布線,因?yàn)樾⌒酒枰?a href="http://www.1cnz.cn/v/tag/1301/" target="_blank">通信并且必須使用 TSV 提供電力。 雖然 TSV 已在芯片制造中使用了十多年,但它們?cè)黾恿朔庋b過(guò)程的復(fù)雜性和成本,因此華為決定發(fā)明一種不使用 TSV 的替代解決方案。華為專家設(shè)計(jì)的本質(zhì)上是 2.5D 和 3D 堆疊的混合體,因?yàn)閮蓚€(gè)小芯片在封裝內(nèi)相互重疊,節(jié)省空間,但不像經(jīng)典 3D 封裝那樣完全疊放。

重疊的 3D 堆疊

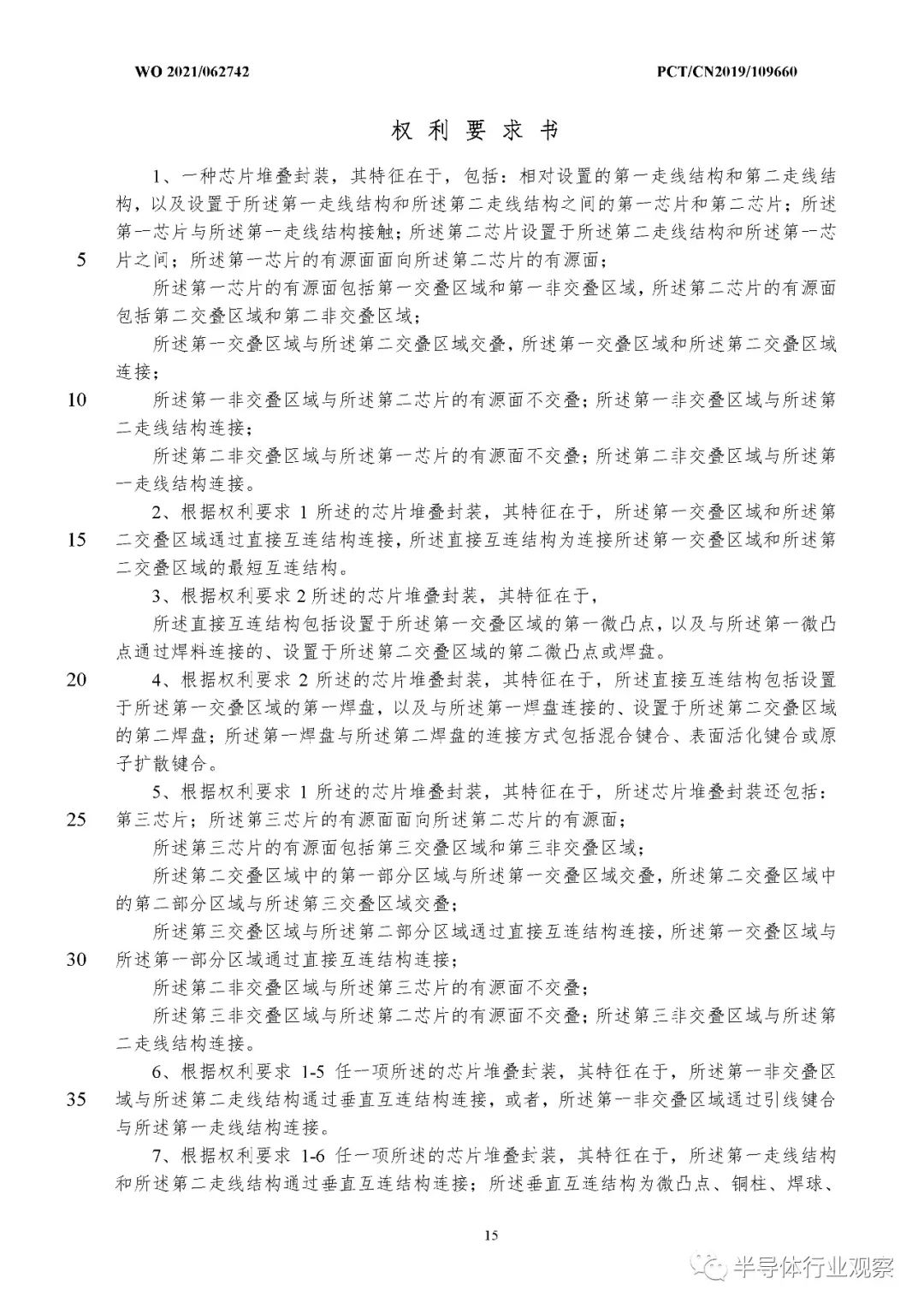

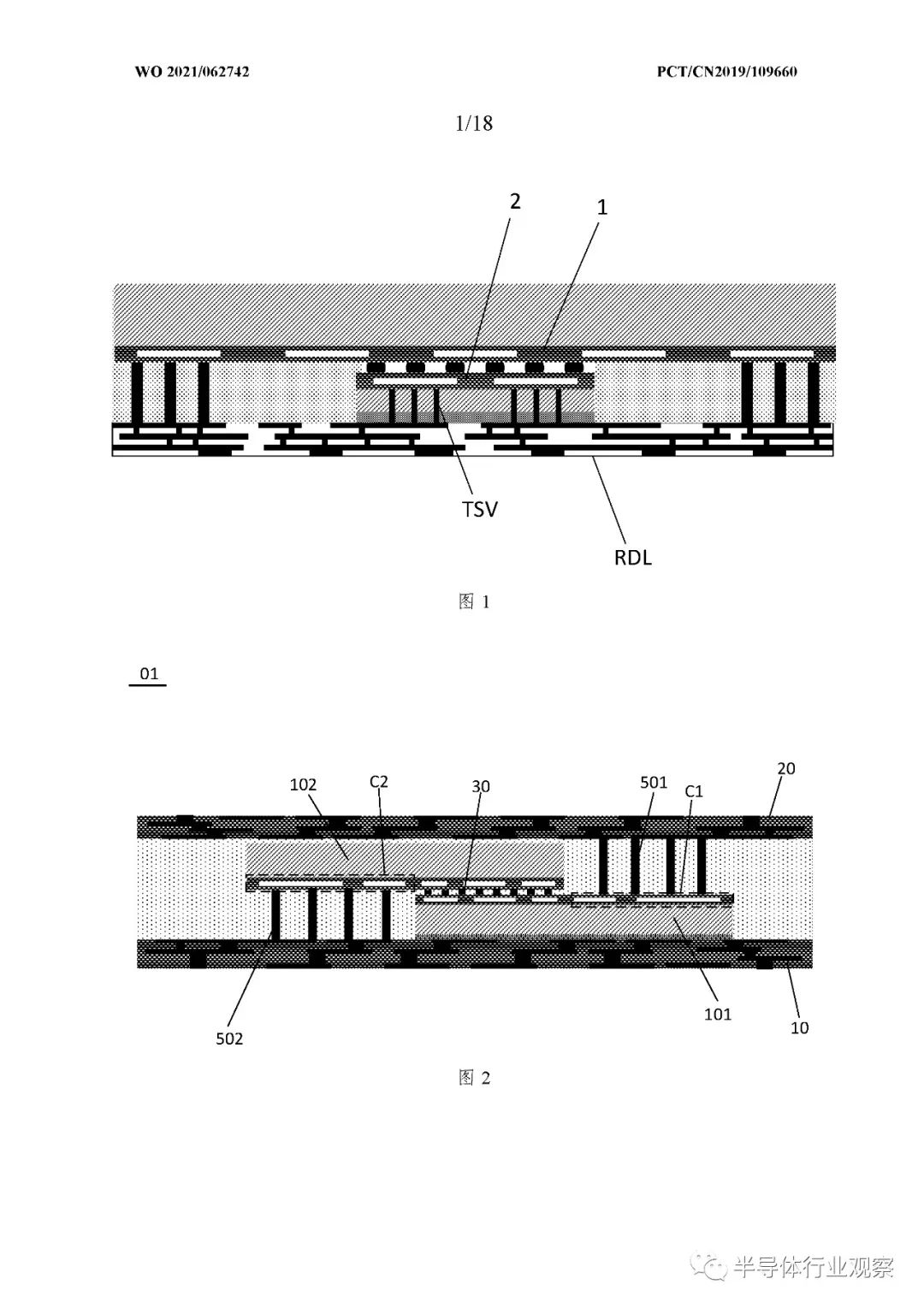

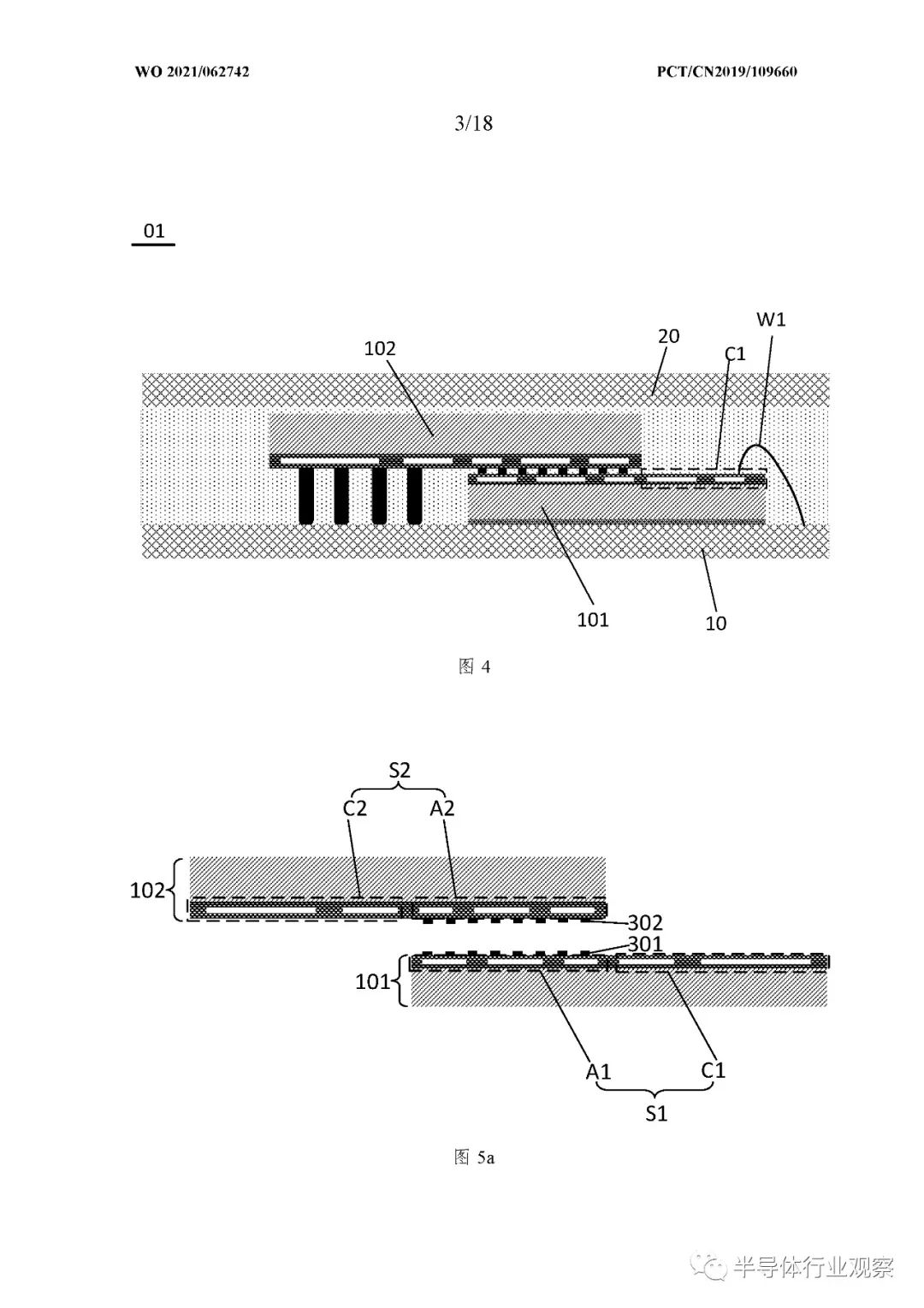

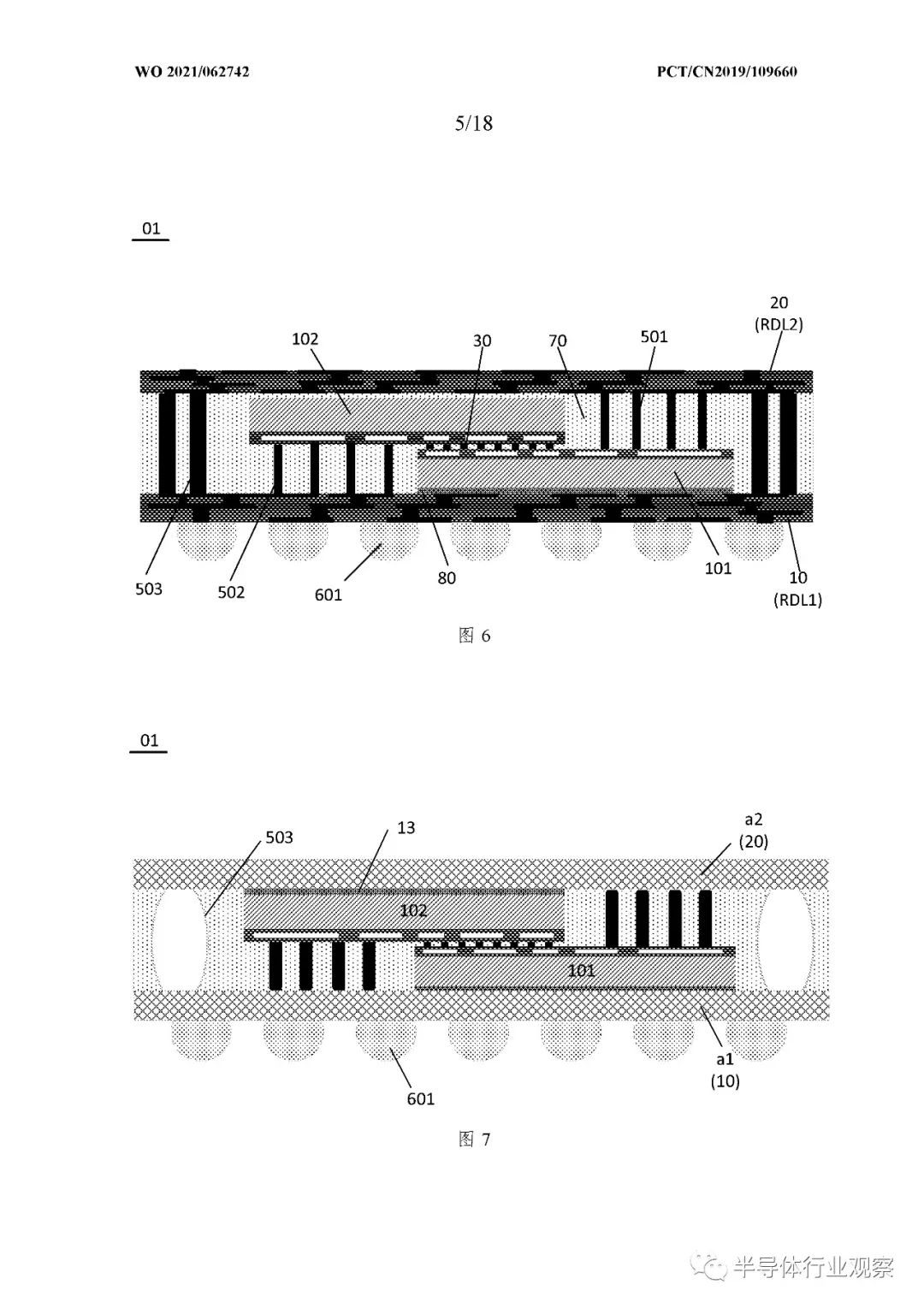

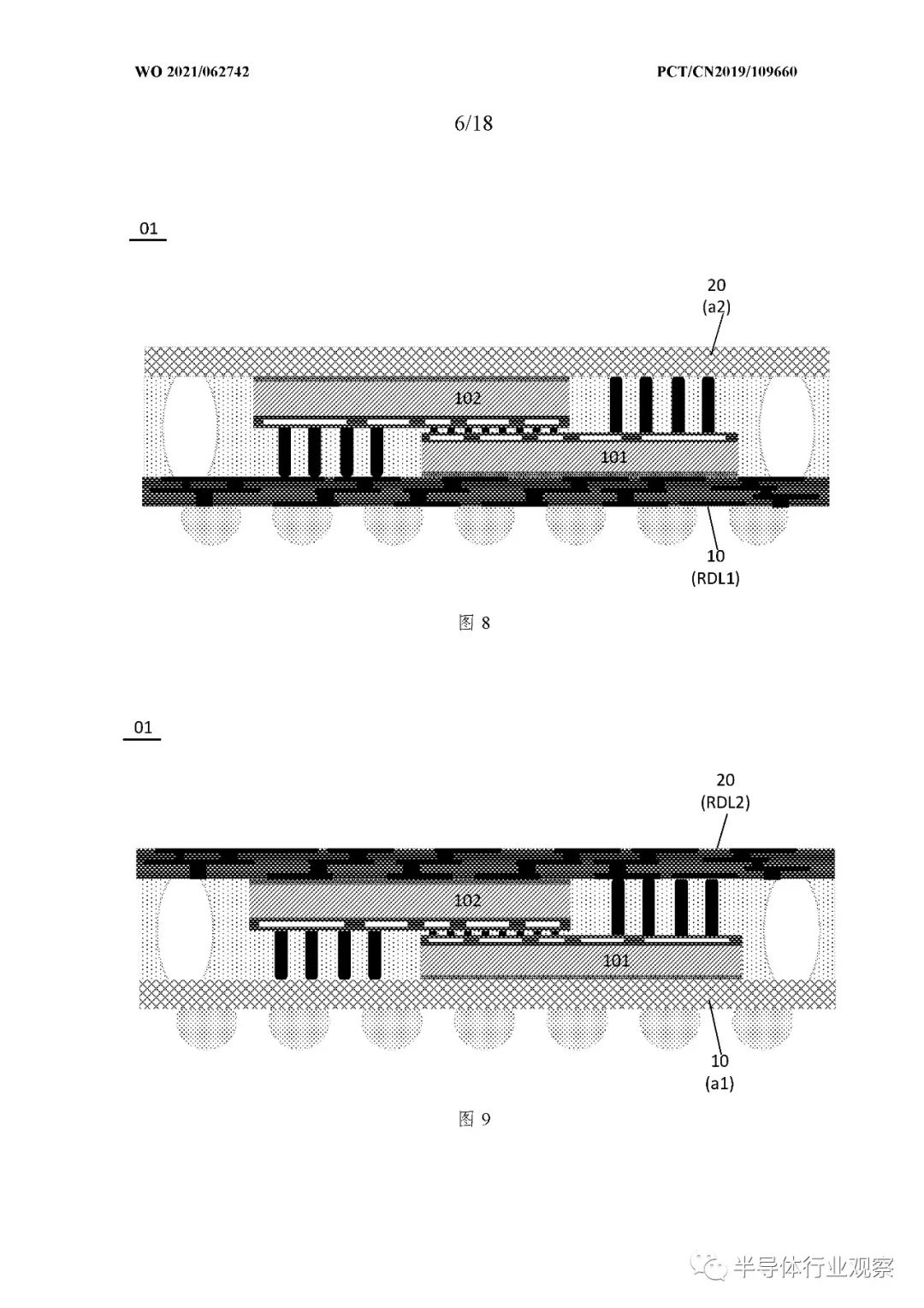

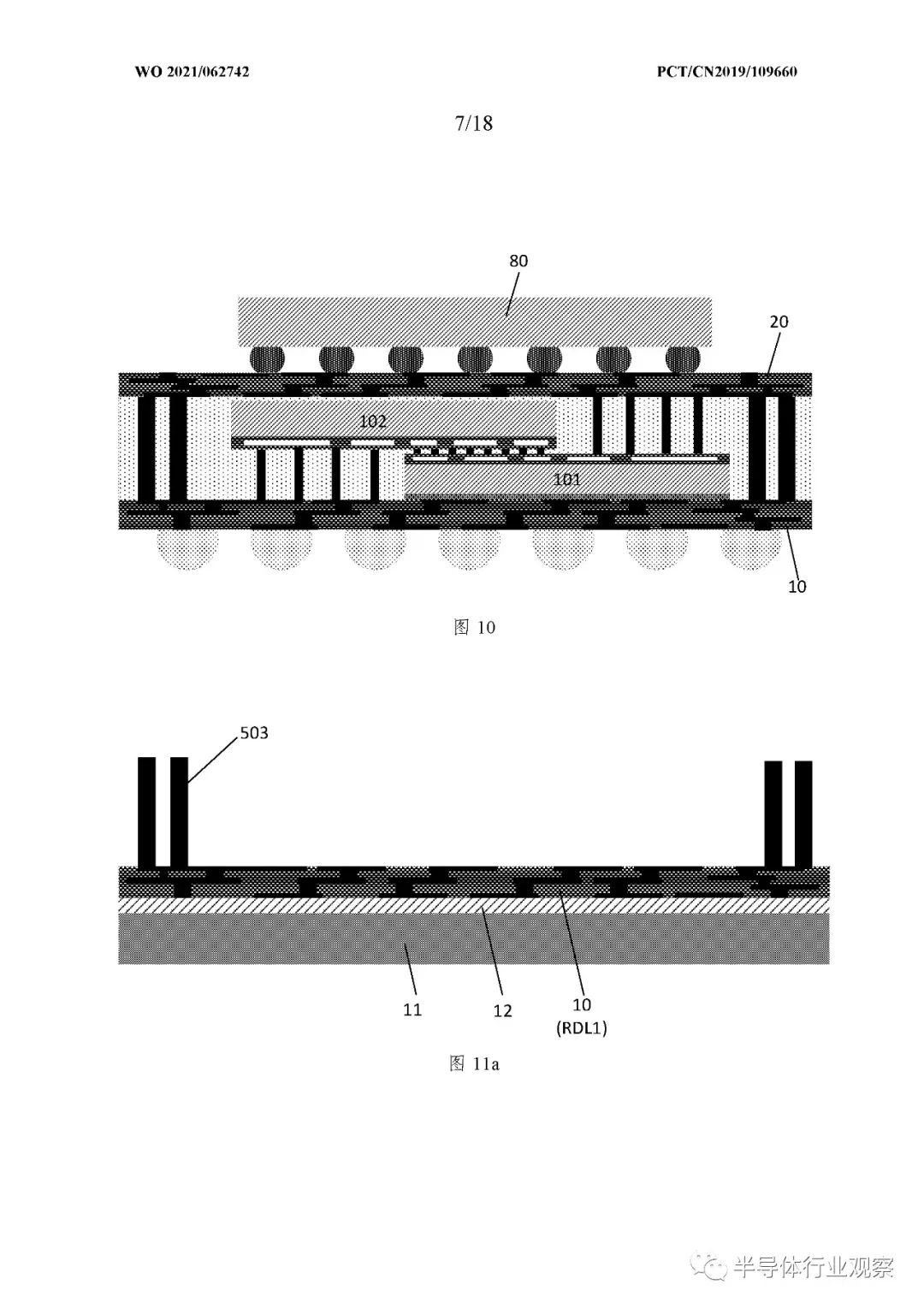

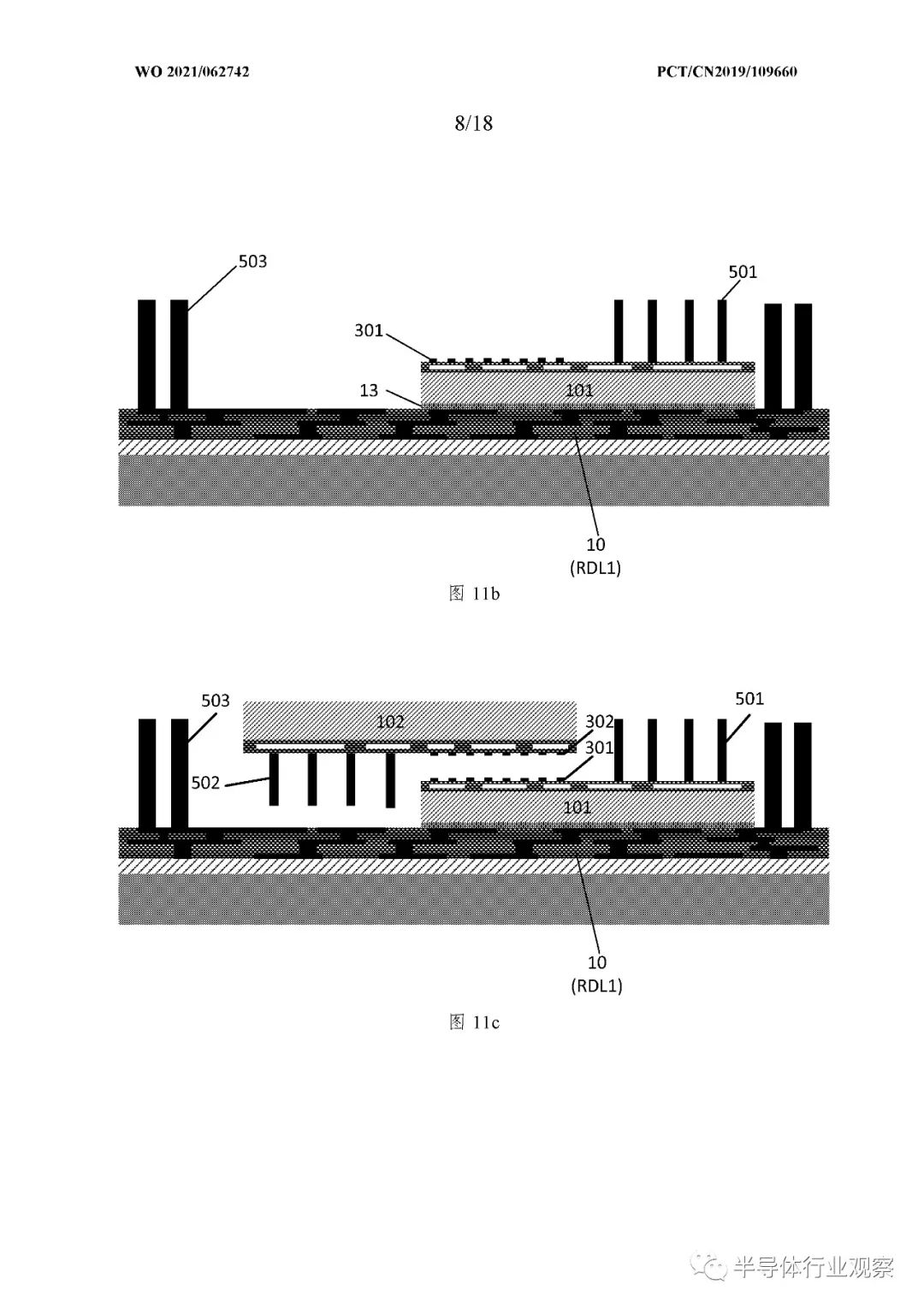

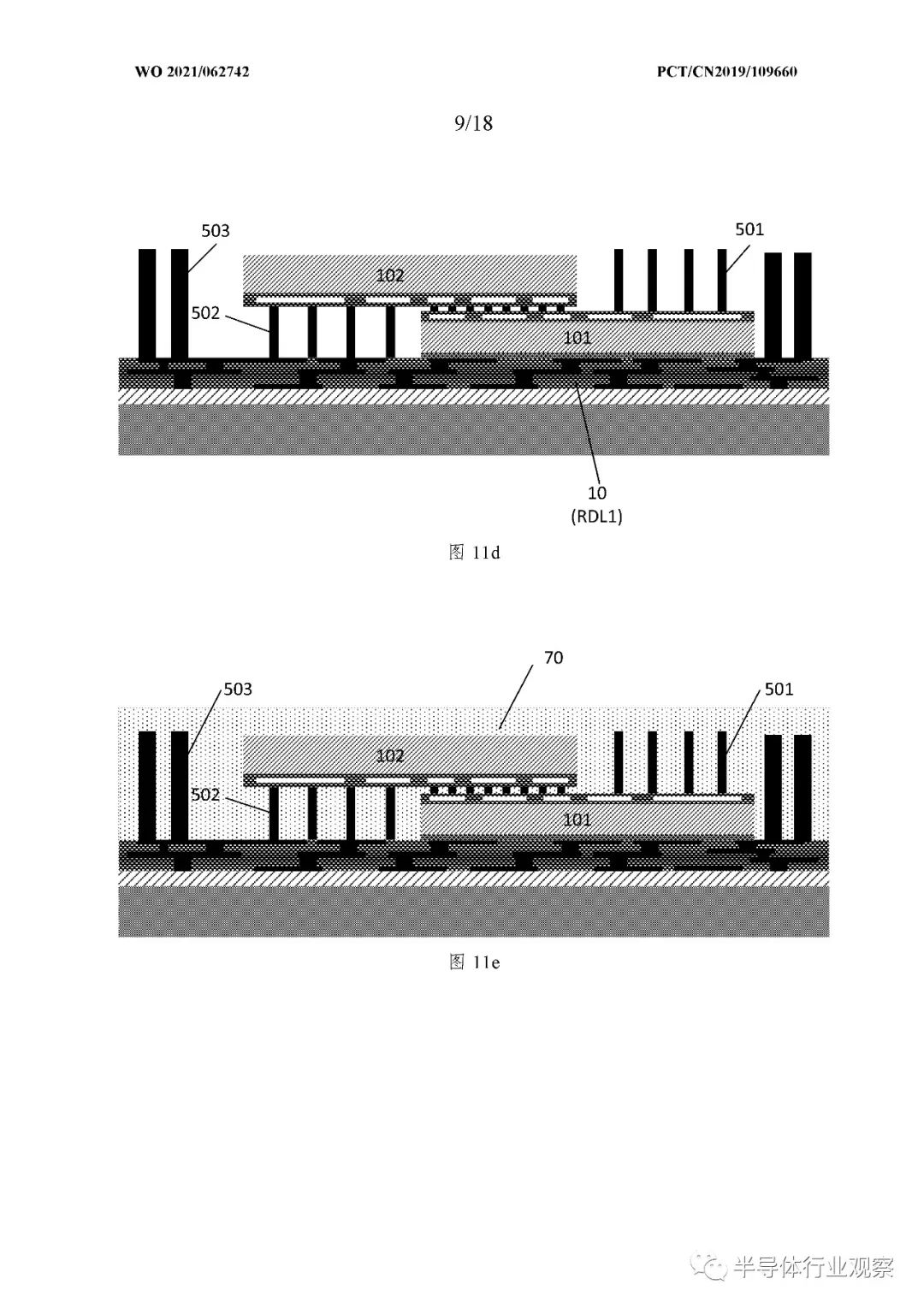

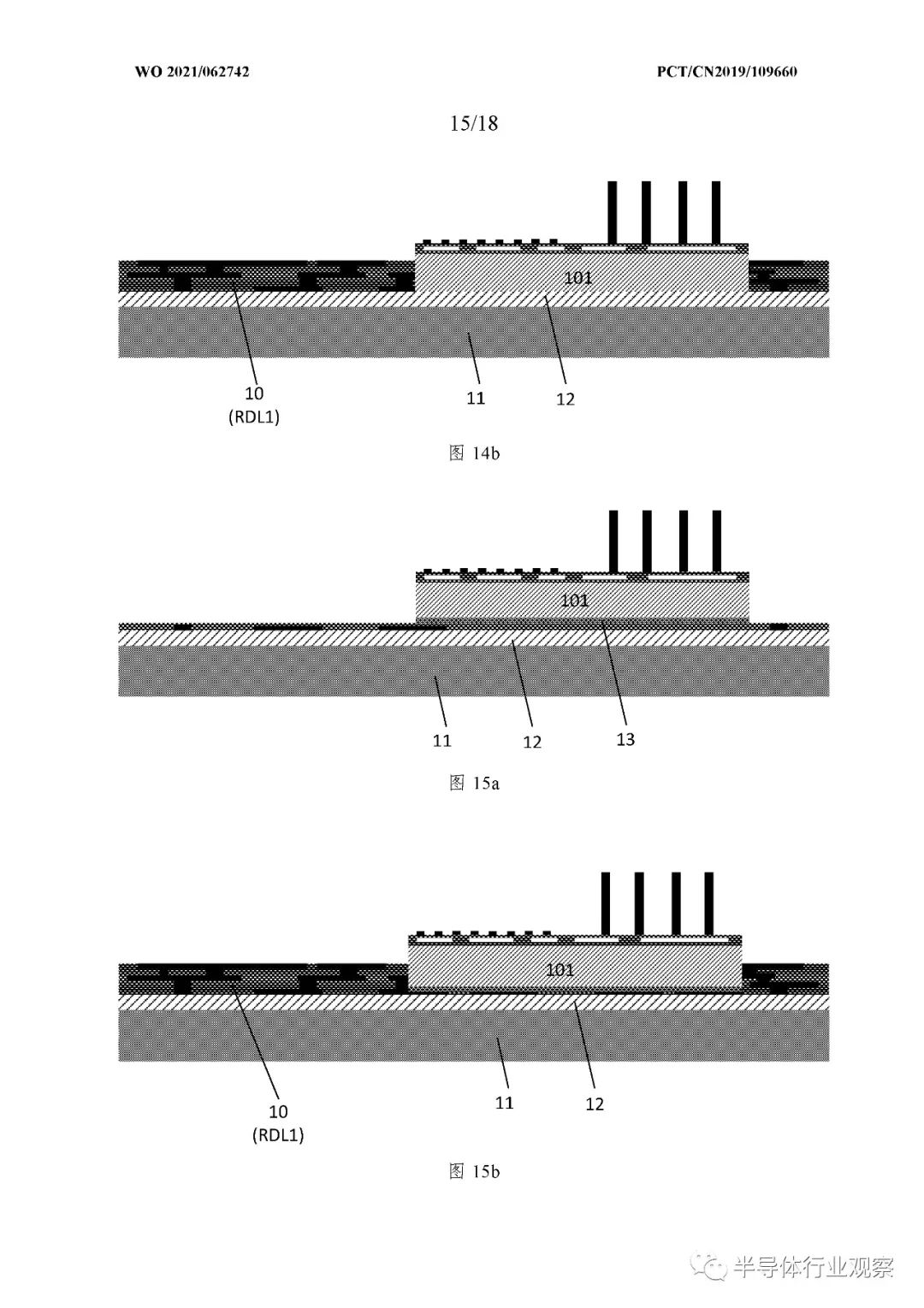

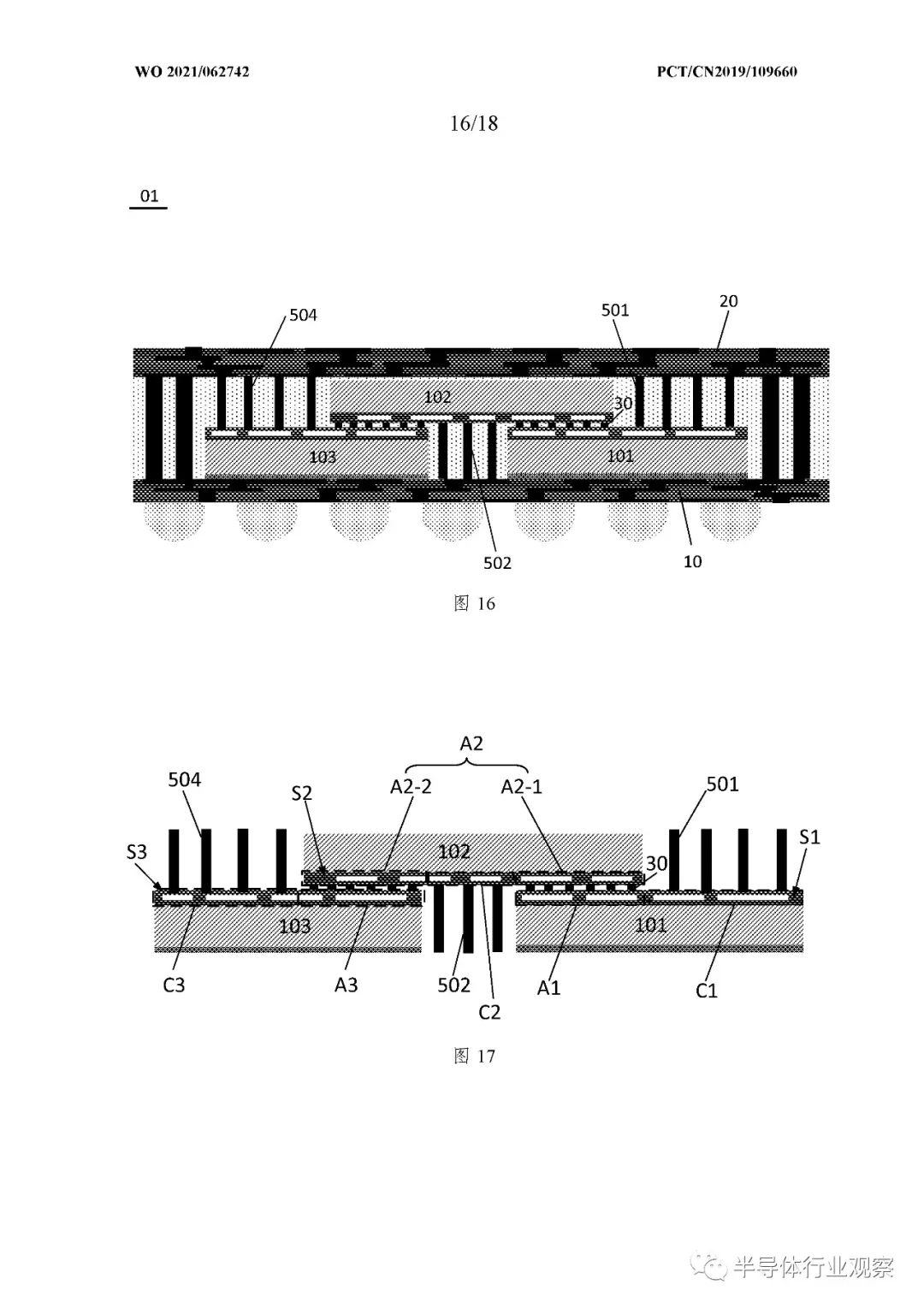

華為的方法使用小芯片的重疊部分來(lái)建立邏輯互連。同時(shí),兩個(gè)或更多小芯片仍然有自己的電力傳輸引腳,使用各種方法連接到自己的再分配層 (RDL)。但是,雖然華為的專利技術(shù)避免使用 TSV,但實(shí)施起來(lái)并不容易且便宜。

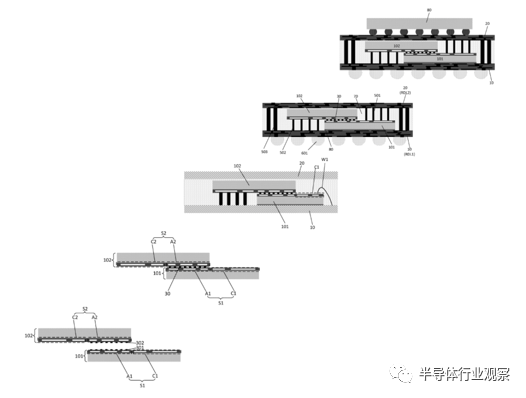

(圖片來(lái)源:華為) 華為的流程涉及在連接到另一個(gè)(或其他)之前將其中一個(gè)小芯片倒置。它還需要構(gòu)建至少兩個(gè)重新分配層來(lái)提供電力(例如,兩個(gè)小芯片意味著兩個(gè) RDL,三個(gè)小芯片仍然可以使用兩個(gè) RDL,所以四個(gè),請(qǐng)參閱文章末尾的專利文檔以了解詳細(xì)信息),這并不是特別便宜,因?yàn)樗黾恿藥讉€(gè)額外的工藝步驟。好消息是其中一個(gè)芯片的再分配層可以用來(lái)連接內(nèi)存等東西,從而節(jié)省空間。

事實(shí)上,華為的混合 3D 堆疊方式可以說(shuō)比其他公司傳統(tǒng)的 2.5D 和 3D 封裝技術(shù)更通用。例如,很難將兩個(gè)或三個(gè)耗電且熱的邏輯裸片堆疊在一起,因?yàn)槔鋮s這樣的堆棧將非常復(fù)雜(這最終可能意味著對(duì)時(shí)鐘和性能的妥協(xié))。華為的方法增加了堆棧的表面尺寸,從而簡(jiǎn)化了冷卻。同時(shí),堆棧仍然小于 2.5D 封裝,這對(duì)于智能手機(jī)、筆記本電腦或平板電腦等移動(dòng)應(yīng)用程序很重要。 從產(chǎn)業(yè)來(lái)看,其他半導(dǎo)體合同制造商(臺(tái)積電、GlobalFoundries)、集成設(shè)計(jì)制造商(英特爾、三星),甚至可以使用領(lǐng)先的晶圓廠工具和工藝技術(shù)的無(wú)晶圓廠芯片開發(fā)商(AMD)也開發(fā)了自己的 2.5D 和 3D 小芯片堆疊和互連方法為他們的客戶或他們未來(lái)的產(chǎn)品提供服務(wù)。因此,華為只是順勢(shì)而為。

審核編輯 :李倩

-

處理器

+關(guān)注

關(guān)注

68文章

19312瀏覽量

230030 -

華為

+關(guān)注

關(guān)注

216文章

34470瀏覽量

251928 -

3D芯片

+關(guān)注

關(guān)注

0文章

52瀏覽量

18425

原文標(biāo)題:華為3D芯片堆疊專利解讀

文章出處:【微信號(hào):ZHISHIKU-Pro,微信公眾號(hào):知識(shí)酷Pro】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【「大話芯片制造」閱讀體驗(yàn)】+ 芯片制造過(guò)程和生產(chǎn)工藝

芯片濕法蝕刻工藝

雙芯片磁性位置傳感器中堆疊芯片和并排芯片實(shí)施方案之間的比較

芯片底部填充工藝流程有哪些?

解讀MIPI A-PHY與車載Serdes芯片技術(shù)與測(cè)試

plc是一種什么的電子裝置

fdm成型工藝的優(yōu)缺點(diǎn)

underfill是什么工藝?

華為集成芯片怎么樣

介紹一種用于絕對(duì)定量的微腔式數(shù)字PCR微流控芯片

華為一種芯片堆疊工藝解讀

華為一種芯片堆疊工藝解讀

評(píng)論