讓PCIe總線保證足夠的帶寬、供電也成為了不斷追求的目標,對更高速度的需求推動了標準機構定義下一代PCI Express,PCIe 5.0速度從PCIe 4.0 的16GT/s翻倍至32GT/s;到了剛發布的PCIe 6.0,實現了帶寬速率全面翻倍,而且PCIe6.0對底層信令進行了改進。

是德科技剛剛發布了針對PCIe5.0/6.0的完整測試方案,至此能夠提供全方位的物理層測試解決方案,成為目前僅有的完整提供從建模、仿真、互連參數表征、Tx、PLL 和 Rx 測試解決方案的公司。通過是德科技租賃合作伙伴益萊儲/Electro Rent的聯合支持,客戶可以以測試儀器購買價格的一小部分、找到最新的產品,并以最快的速度獲得。在最近跟需要PCIe5.0測試方案的客戶的互動中,我們深切感受到來自客戶的急迫需求和對我們服務的欣慰,同心協力幫助客戶贏得未來市場先機。

向下一代PCIe標準的演進

PCI Express 5.0代表了使用非歸零(NRZ)信令的最新PCI標準,速度從PCIe 4.0 的16GT/s翻倍至32GT/s,PCIe 5.0標準在2019年完成。為了應對日益增長的高性能計算、人工智能加速器、高性能存儲等快速發展的需求,PCI-SIG著手開發制定下一代PCIe 6.0規范,PCIe 6.0 v1.0版本規范上已于2022年1月正式發布。

PCIe 6.0擁有了超低延遲、超高帶寬、超快速率,而且PCIe6.0對底層信令進行了改進,也是PCIe歷史上改進最大的一次。通過PCIe鏈路速度提升一倍,PCIe 6.0在實際上獲得了帶寬速率全面翻倍的效果,x1通道從4GB/s提升到了8GB/s,x16通道則一直擴展到了單向128GB/s,雙向達到256GB/s。這相當于設備可以使用更少的通道數量,達到更高的速率,從而獲得實現降低硬件成本效果。

雖然PCIe6.0相關標準已經發布,但不可否認從消費者市場來看,PCIe5.0市場還處于早期階段。大部分消費者還停留在PCIe4.0,主要是因為目前支持PCIe5.0的產品價格都十分高昂,對消費者而言,PCIe4.0并不會影響工作和游戲體驗,因此PCIe5.0的普及率還比較低。不過PCIe5.0相關產品的測試驗證正在火熱進行中。

新一代PCIe5.0測試的挑戰

PCIe5.0測試挑戰隨著速度翻倍而增加,最大挑戰來自于通道長度,信號速度越快,在PC板上傳輸的信號載頻越高。有兩類物理損傷會限制工程師傳輸PCIe信號的預期距離:一個是通道的衰減,一個是由于管腳、連接器、通孔和其他結構中發現的阻抗不連續而在通道內發生的反射。

PCIe 5.0規范使用的信道在16 GHz時衰減為-36分貝,16 GHz的頻率代表32 GT/s數字信號的奈奎斯特頻率。例如,當PCIe 5.0信號開始時,它可能具有800 mV的典型峰間電壓。然而,在通過建議的-36分貝通道后,就找不到任何與睜開眼睛的相似之處。只有通過應用基于發射機的均衡(去加重)和接收機均衡(CTLE和DFE的組合),PCIe 5.0信號才能通過系統通道并被接收機準確地解釋。

對于PCIe 5.0信號,眼睛高度的最低預期為10 mV(均衡后)。即使有一個近乎完美的低抖動發射器,信道的顯著衰減也會降低信號振幅,以至于由反射和串擾引起的任何其他類型的信號損傷都會關閉可恢復眼。

為了幫助確保支持PCIe5.0的產品取得成功,是德科技積極提供測試解決方案。在物理層系統仿真、物理層互連以及發射端(Tx)和接收端(Rx)測試基礎上,又最新增加了PCIE5.0協議分析測試方案,至此能夠提供從設計仿真到物理層再到協議層的測試和驗證。

UXR+M8040 PCIe5.0測試升級平臺

是德科技UXR0334A+M8040A實現了PCIe5.0高速接口測試平臺升級,這也是益萊儲客戶最近的熱門需求。

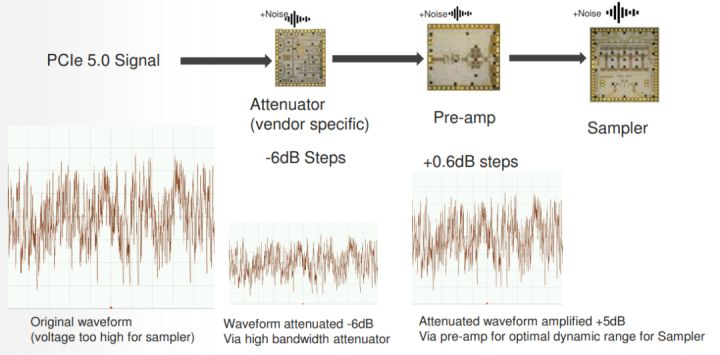

信號進入示波器后,經過模擬前端包括衰減器、放大器、采樣器,再進入到 ADC,示波器中所使用的半導體工藝、封裝設計、互連設計,ADC 的垂直有效位數等的差異,會導致信噪比會存在差距。所以,降低儀器底噪、提升 ADC 的位數會為提升測量精度帶來非常大的幫助,在足夠采樣率的條件下,這些性能超過了采用更高采樣率對測量結果的影響。

圖1 示波器前端信號采集鏈路

基于 InP HB2C 工藝 MMIC 前端、多芯片三維封裝互連和 10bit ADCUXR系列示波器在 PCIe 5.0 的基于 1e-12 條件下的眼高、眼寬、TJ 等結果有明顯更高的裕量。以33GHz帶寬的UXR0334A示波器為例,在相同垂直滿量程的條件下,UXR的底噪指標是同行33GHz帶寬示波器的一半水平。

另外從測量方法上來說,垂直刻度的設定會影響到測量的信噪比,測量時有一點比較重要的是,要優化垂直刻度,讓信號盡量充滿垂直滿量程,這樣會達到最佳的測量信噪比。從下表中可以看到,在相同的測試條件下:使用 M8040A誤碼儀,加入一定的壓力,經過 PCIe 5.0 Base夾具構建的36dB的損耗,設置相同的 Preset P9,使用相同的接收 CTLE DC Gain 10dB,示波器都優化調整了垂直刻度。

M8040A 高性能 BERT是一款高度綜合的比特誤碼率測試儀(BERT),M8040A 專為研發和測試工程師設計,幫助他們表征芯片、器件、收發信機模塊和子組件、電路板以及系統。不僅能夠測試 PCIe 5.0,還能為新興的 PCIe 6.0技術探索發展路線,適用于物理層表征和合規性測試,它支持 PAM4 和 NRZ 信號,以及高達 64 GBaud 的數據速率,覆蓋 400 GbE 標準的所有特性。

作為是德科技租賃合作伙伴,面對諸多不確定性和復雜多變的產業形勢,益萊儲/Electro Rent在租賃服務及測試資產管理方面為客戶提供更大價值、更高靈活性,并讓努力不斷落地,更好地服務客戶。了解益萊儲PCIe5.0及高速數字接口測試解決方案更多庫存與報價信息,https://www.electrorent.com/cn/solutions/digital-computing。

-

帶寬

+關注

關注

3文章

939瀏覽量

40968 -

PCI

+關注

關注

4文章

670瀏覽量

130337 -

PCIe

+關注

關注

15文章

1243瀏覽量

82775

發布評論請先 登錄

相關推薦

銀翼新境 致態TiPro9000引領個人存儲PCIe 5.0新時代

預決賽節點公布丨第七屆CCF開源創新大賽火熱進行中!

國產MCU有推薦嗎?最好是經過市場驗證的!

愛立信消費者實驗室解讀未來五年AR消費者趨勢

PCIe 5.0 SerDes 測試

亞馬遜云科技賦能Shulex打造基于生成式AI的客服和消費者洞察

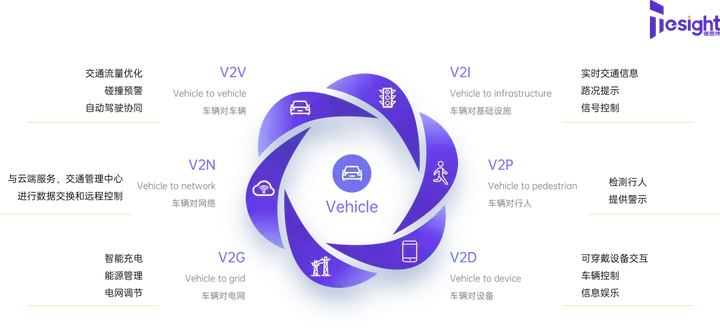

深度解析消費者最關心的車聯網核心問題

愛立信消費者實驗室:2030年代十大熱門消費者趨勢 AI賦能的未來

AI浪潮下的十大消費者新趨勢

2024年小米汽車產業鏈分析及新品上市全景洞察報告

愛立信消費者實驗室報告發布

梯云物聯:革新未來電梯物聯網行業,您做好準備了嗎?

PCIe 5.0產品測試驗證火熱進行中,為未來引領消費者市場做好準備

PCIe 5.0產品測試驗證火熱進行中,為未來引領消費者市場做好準備

評論