三星周四表示,它有望在本季度(即未來(lái)幾周內(nèi))使用其 3GAE (早期 3 納米級(jí)柵極全能)制造工藝開(kāi)始大批量生產(chǎn)。該公告不僅標(biāo)志著業(yè)界首個(gè)3nm級(jí)制造技術(shù),也是第一個(gè)使用環(huán)柵場(chǎng)效應(yīng)晶體管(GAAFET)的節(jié)點(diǎn)。

三星在財(cái)報(bào)說(shuō)明中寫道:“通過(guò)世界上首次大規(guī)模生產(chǎn) GAA 3 納米工藝來(lái)增強(qiáng)技術(shù)領(lǐng)先地位 。”(Exceed market growth by sustaining leadership in GAA process technology,adopt pricing strategies to ensure future investments, and raise the yield and portion of our advanced processe)

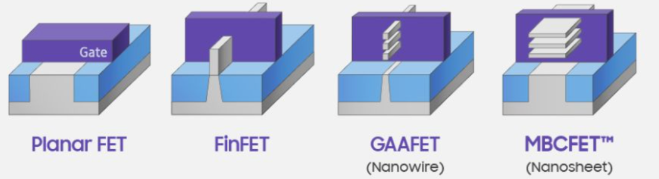

三星代工的 3GAE 工藝技術(shù) 是該公司首個(gè)使用 GAA 晶體管的工藝,三星官方將其稱為多橋溝道場(chǎng)效應(yīng)晶體管 (MBCFET)。

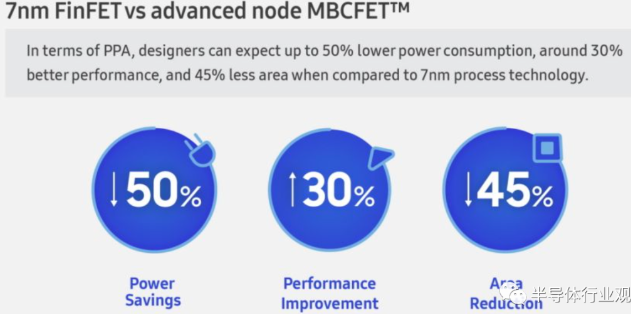

三星大約在三年前正式推出了其 3GAE 和 3GAP 節(jié)點(diǎn)。三星表示,該工藝將實(shí)現(xiàn) 30% 的性能提升、50% 的功耗降低以及高達(dá) 80% 的晶體管密度(包括邏輯和 SRAM 晶體管的混合)。不過(guò),三星的性能和功耗的實(shí)際組合將如何發(fā)揮作用還有待觀察。

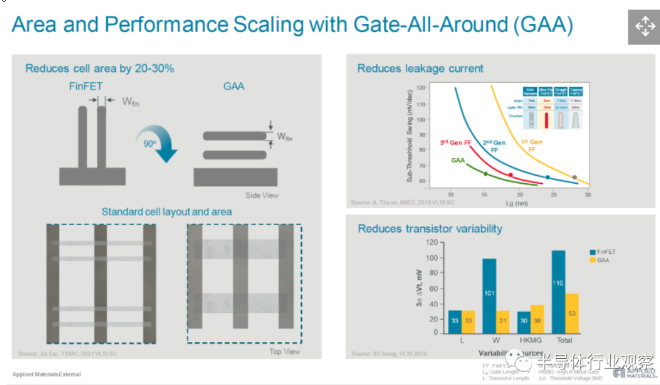

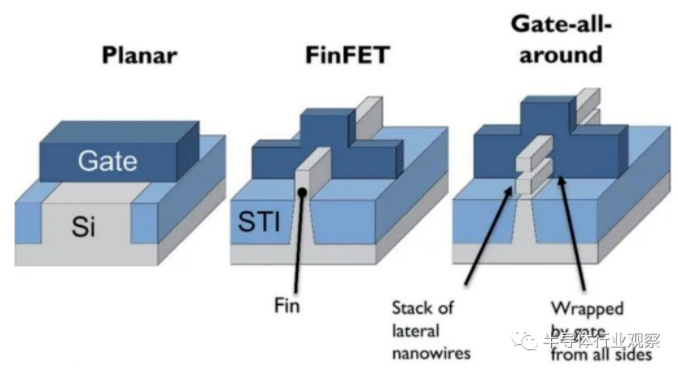

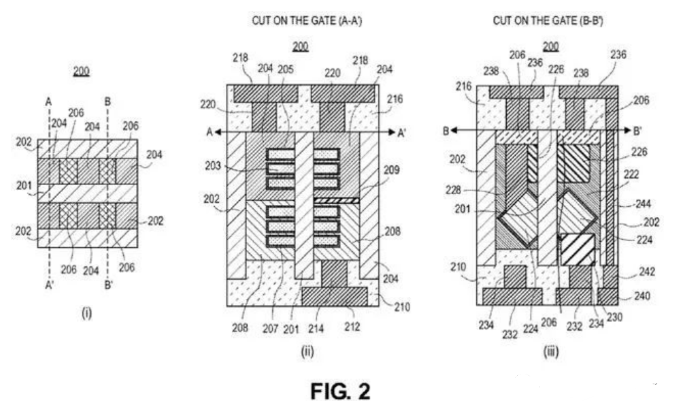

理論上,與目前使用的 FinFET 相比,GAAFET 具有許多優(yōu)勢(shì)。在 GAA 晶體管中,溝道是水平的并且被柵極包圍。GAA 溝道是使用外延和選擇性材料去除形成的,這允許設(shè)計(jì)人員通過(guò)調(diào)整晶體管通道的寬度來(lái)精確調(diào)整它們。通過(guò)更寬的溝道獲得高性能,通過(guò)更窄的溝道獲得低功耗。這種精度大大降低了晶體管泄漏電流(即降低功耗)以及晶體管性能可變性(假設(shè)一切正常),這意味著更快的產(chǎn)品交付時(shí)間、上市時(shí)間和更高的產(chǎn)量。此外,根據(jù)應(yīng)用材料公司最近的一份報(bào)告,GAAFET 有望將cell面積減少 20% 至 30% 。

說(shuō)到應(yīng)用,它最近推出的用于形成柵極氧化物疊層的高真空系統(tǒng) IMS(集成材料解決方案)系統(tǒng)旨在解決 GAA 晶體管制造的主要挑戰(zhàn),即溝道之間的空間非常薄以及沉積多晶硅的必要性。在很短的時(shí)間內(nèi)在溝道周圍形成層?xùn)叛趸瘜雍徒饘贃暖B層。應(yīng)用材料公司的新型 AMS 工具可以使用原子層沉積 (ALD)、熱步驟和等離子體處理步驟沉積僅 1.5 埃厚的柵極氧化物。高度集成的機(jī)器還執(zhí)行所有必要的計(jì)量步驟。

三星的 3GAE 是一種“早期”的 3nm 級(jí)制造技術(shù),3GAE 將主要由三星 LSI(三星的芯片開(kāi)發(fā)部門)以及可能一兩個(gè) SF 的其他 alpha 客戶使用。請(qǐng)記住,三星的 LSI 和 SF 的其他早期客戶傾向于大批量制造芯片,預(yù)計(jì) 3GAE 技術(shù)將得到相當(dāng)廣泛的應(yīng)用,前提是這些產(chǎn)品的產(chǎn)量和性能符合預(yù)期。

過(guò)渡到全新的晶體管結(jié)構(gòu)通常是一種風(fēng)險(xiǎn),因?yàn)樗婕叭碌闹圃旃に囈约叭碌墓ぞ摺F渌魬?zhàn)是所有新節(jié)點(diǎn)引入并由新的電子設(shè)計(jì)自動(dòng)化 (EDA) 軟件解決的新布局方法、布局規(guī)劃規(guī)則和布線規(guī)則。最后,芯片設(shè)計(jì)人員需要開(kāi)發(fā)全新的 IP,價(jià)格昂貴。

外媒:三星3nm良率僅有20%

據(jù)外媒Phonearena報(bào)道,三星代工廠是僅次于巨頭臺(tái)積電的全球第二大獨(dú)立代工廠。換句話說(shuō),除了制造自己設(shè)計(jì)的 Exynos 芯片外,三星還根據(jù)高通等代工廠客戶的第三方公司提交的設(shè)計(jì)來(lái)制造芯片。

Snapdragon 865 應(yīng)用處理器 (AP) 由臺(tái)積電使用其 7nm 工藝節(jié)點(diǎn)構(gòu)建。到了5nm Snapdragon 888 芯片組,高通回到了三星,并繼續(xù)依靠韓國(guó)代工廠生產(chǎn) 4nm Snapdragon 8 Gen 1。這是目前為三星、小米、摩托羅拉制造的高端 Android 手機(jī)提供動(dòng)力的 AP。

三星代工繼續(xù)在良率上苦苦掙扎

但在 2 月份,有報(bào)道稱三星 Foundry 在其 4nm 工藝節(jié)點(diǎn)上的良率僅為 35%。這意味著只有 35% 的從晶圓上切割下來(lái)的芯片裸片可以通過(guò)質(zhì)量控制。相比之下,臺(tái)積電在生產(chǎn) 4nm Snapdragon 8 Gen 1 Plus 時(shí)實(shí)現(xiàn)了 70% 的良率。換句話說(shuō),在所有條件相同的情況下,臺(tái)積電在同一時(shí)期制造的芯片數(shù)量是三星代工的兩倍。

這就導(dǎo)致臺(tái)積電最終收到高通的訂單,以構(gòu)建其剩余的 Snapdragon 8 Gen1 芯片組以及 Snapdragon 8 Gen 1 Plus SoC。我們還假設(shè)臺(tái)積電將獲得制造 3nm Snapdragon 8 Gen 2 的許可,即使高通需要向臺(tái)積電支付溢價(jià)以讓該芯片組的獨(dú)家制造商在短時(shí)間內(nèi)制造足夠的芯片。

盡管三星最近表示其產(chǎn)量一直在提高,但《商業(yè)郵報(bào)》的一份報(bào)告稱,三星 3nm 工藝節(jié)點(diǎn)的產(chǎn)量仍遠(yuǎn)低于公司的目標(biāo)。雖然三星代工廠的全環(huán)柵極 (GAA) 晶體管架構(gòu)首次推出其 3 納米節(jié)點(diǎn),使其在臺(tái)積電(臺(tái)積電將推出其 2 納米節(jié)點(diǎn)的 GAA 架構(gòu))上處于領(lǐng)先地位,但三星代工廠在其早期 3 納米生產(chǎn)中的良率一直處于10% 至 20%的范圍 。

這不僅是三星需要改進(jìn)的極低良率,而且比 Sammy 在 4nm Snapdragon 8 Gen 1 中所經(jīng)歷的上述 35% 良率還要糟糕。

Wccftech 表示,據(jù)消息人士稱,三星將從明年開(kāi)始向客戶發(fā)貨的 3nm GAA 芯片組的第一個(gè)“性能版本”實(shí)際上可能是新的內(nèi)部 Exynos 芯片。據(jù)報(bào)道,三星一直在為其智能手機(jī)開(kāi)發(fā)新的 Exynos 芯片系列,但現(xiàn)階段尚不清楚它們是否會(huì)使用 3nm GAA 工藝節(jié)點(diǎn)制造。

臺(tái)積電和三星在制程領(lǐng)導(dǎo)力方面很快就會(huì)有新的挑戰(zhàn)者

臺(tái)積電和三星很快就會(huì)有新的挑戰(zhàn)者,因?yàn)?a href="http://www.1cnz.cn/tags/英特爾/" target="_blank">英特爾曾表示,其目標(biāo)是在 2024 年底之前接管行業(yè)的制程領(lǐng)導(dǎo)地位。它還率先獲得了更先進(jìn)的極紫外 (EUV) ***。

第二代 EUV 機(jī)器被稱為High NA 或高數(shù)值孔徑。當(dāng)前的 EUV 機(jī)器的 NA 為 0.33,但新機(jī)器的 NA 為 0.55。NA 越高,蝕刻在晶圓上的電路圖案的分辨率就越高。這將幫助芯片設(shè)計(jì)人員和代工廠制造出新的芯片組,其中包含的晶體管數(shù)量甚至超過(guò)了當(dāng)前集成電路上使用的數(shù)十億個(gè)晶體管。

它還將阻止代工廠再次通過(guò) EUV 機(jī)器運(yùn)行晶圓以向芯片添加額外的功能。ASML 表示,第二代 EUV 機(jī)器產(chǎn)生的更高分辨率圖案將提供更高的分辨率將使芯片特征小 1.7 倍,芯片密度增加 2.9 倍。

通過(guò)首先獲得這臺(tái)機(jī)器,英特爾將能夠朝著從臺(tái)積電和三星手中奪回制程領(lǐng)導(dǎo)地位的目標(biāo)邁出一大步。

臺(tái)積電3nm投產(chǎn)時(shí)間曝光

據(jù)臺(tái)媒聯(lián)合報(bào)報(bào)道,在晶圓代工三強(qiáng)爭(zhēng)霸中,臺(tái)積電和三星在3納米爭(zhēng)戰(zhàn),始終吸引全球半導(dǎo)體產(chǎn)業(yè)的目光。據(jù)調(diào)查,一度因開(kāi)發(fā)時(shí)程延誤,導(dǎo)致蘋果新一代處理器今年仍采用5納米加強(qiáng)版N4P的臺(tái)積電3納米,近期獲得重大突破。臺(tái)積電決定今年率先以第二版3納米制程N(yùn)3B,今年8月于今年南北兩地,即新竹12廠研發(fā)中心第八期工廠及南科18廠P5廠同步投片,正式以鰭式場(chǎng)效電晶體(FinFET)架構(gòu),對(duì)決三星的環(huán)繞閘極(GAA)制程。

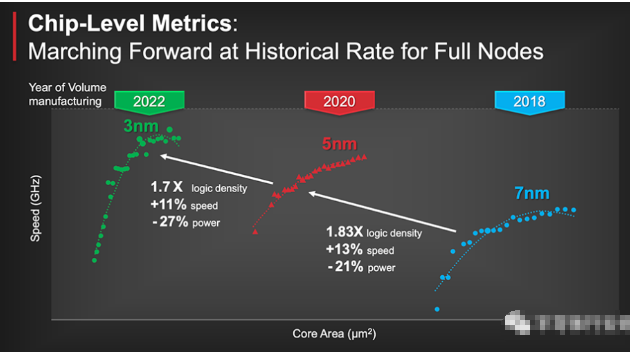

據(jù)臺(tái)積電介紹,公司的3納米(N3)制程技術(shù)將是5納米(N5)制程技術(shù)之后的另一個(gè)全世代制程,在N3制程技術(shù)推出時(shí)將會(huì)是業(yè)界最先進(jìn)的制程技術(shù),具備最佳的PPA及電晶體技術(shù)。相較于N5制程技術(shù),N3制程技術(shù)的邏輯密度將增加約70%,在相同功耗下速度提升10-15%,或者在相同速度下功耗降低25-30%。N3制程技術(shù)的開(kāi)發(fā)進(jìn)度符合預(yù)期且進(jìn)展良好,未來(lái)將提供完整的平臺(tái)來(lái)支援行動(dòng)通訊及高效能運(yùn)算應(yīng)用,預(yù)期2021年將接獲多個(gè)客戶產(chǎn)品投片。此外,預(yù)計(jì)于2022下半年開(kāi)始量產(chǎn)。

而如上所述,晶圓18廠將是臺(tái)積電3nm的主要生產(chǎn)工廠。資料系那是,臺(tái)積電南科的Fab 18是現(xiàn)下的擴(kuò)產(chǎn)重心,旗下有P1~P4共4座5納米及4奈廠,以及P5~P8共4座3納米廠,而P1~P3的Fab 18A均處于量產(chǎn)狀態(tài),至于P4~P6的Fab 18B廠生產(chǎn)線則已建置完成,而Fab 18B廠,即3納米制程產(chǎn)線,早在去年年年底就已開(kāi)始進(jìn)行測(cè)試芯片的下線投片。

代工廠的“3nm之戰(zhàn)”

在芯片設(shè)計(jì)企業(yè)還在為產(chǎn)能“明爭(zhēng)暗斗”的時(shí)候,晶圓制造領(lǐng)域又是另外一番景象。對(duì)晶圓制造廠來(lái)說(shuō),眼下更重要的是3nm的突破。誰(shuí)率先量產(chǎn)了3nm,誰(shuí)就將占領(lǐng)未來(lái)晶圓制造產(chǎn)業(yè)的制高點(diǎn),甚至還會(huì)影響AMD、英偉達(dá)等芯片巨頭的產(chǎn)品路線圖。

毫無(wú)疑問(wèn),在3nm這個(gè)節(jié)點(diǎn),目前能一決雌雄的只有臺(tái)積電和三星,但英特爾顯然也在往先進(jìn)制程方面發(fā)力。不過(guò)從近日的消息來(lái)看,臺(tái)積電和三星兩家企業(yè)在量產(chǎn)3nm這件事上進(jìn)行的都頗為坎坷。Gartner 分析師 Samuel Wang表示,3nm 的斜坡將比之前的節(jié)點(diǎn)花費(fèi)更長(zhǎng)的時(shí)間。

臺(tái)積電

近日,一份引用半導(dǎo)體行業(yè)消息來(lái)源的報(bào)告表明,據(jù)報(bào)道,臺(tái)積電在其 3nm 工藝良率方面存在困難。消息來(lái)源報(bào)告的關(guān)鍵傳言是臺(tái)積電發(fā)現(xiàn)其 3nm FinFET 工藝很難達(dá)到令人滿意的良率。但到目前為止,臺(tái)積電尚未公開(kāi)承認(rèn)任何 N3 延遲,相反其聲稱“正在取得良好進(jìn)展”。

眾所周知,臺(tái)積電3nm在晶體管方面采用鰭式場(chǎng)效應(yīng)晶體管(FinFET)結(jié)構(gòu),F(xiàn)inFET運(yùn)用立體的結(jié)構(gòu),增加了電路閘極的接觸面積,進(jìn)而讓電路更加穩(wěn)定,同時(shí)也達(dá)成了半導(dǎo)體制程持續(xù)微縮的目標(biāo)。其實(shí),F(xiàn)inFET晶體管走在3nm多多少少已是極限了,再向下將會(huì)遇到制程微縮而產(chǎn)生的電流控制漏電等物理極限問(wèn)題,而臺(tái)積電之所以仍選擇其很大部分原因是不用變動(dòng)太多的生產(chǎn)工具,也能有較具優(yōu)勢(shì)的成本結(jié)構(gòu)。特別對(duì)于客戶來(lái)說(shuō),既不用有太多設(shè)計(jì)變化還能降低生產(chǎn)成本,可以說(shuō)是雙贏局面。

從此前公開(kāi)數(shù)據(jù)顯示,與5nm芯片相比,臺(tái)積電3nm芯片的邏輯密度將提高75%,效率提高15%,功耗降低30%。據(jù)悉,臺(tái)積電 3nm 制程已于2021年3 月開(kāi)始風(fēng)險(xiǎn)性試產(chǎn)并小量交貨,預(yù)計(jì)將在2022年下半年開(kāi)始商業(yè)化生產(chǎn)。

來(lái)源:臺(tái)積電

從工廠方面來(lái)看,中國(guó)臺(tái)灣南科18廠四至六期是臺(tái)積電3nm量產(chǎn)基地。客戶方面,從上文可以看出,英特爾、蘋果、高通等都選擇了臺(tái)積電。大摩分析師Charlie Chan日前發(fā)表報(bào)告稱,臺(tái)積電在2023年的3nm芯片代工市場(chǎng)上幾乎是壟斷性的,市場(chǎng)份額接近100%。

三星

不同于臺(tái)積電在良率方面的問(wèn)題,三星在3nm的困難是3 納米GAA 制程建立專利IP 數(shù)量方面落后。據(jù)南韓媒體報(bào)道,三星缺乏3 納米GAA 制程相關(guān)專利,令三星感到不安。

三星在晶體管方面采用的是柵極環(huán)繞型 (Gate-all-around,GAA) 晶體管架構(gòu)。相比臺(tái)積電的FinFET晶體管,基于GAA的3nm技術(shù)成本肯定較高,但從性能表現(xiàn)上來(lái)看,基于GAA架構(gòu)的晶體管可以提供比FinFET更好的靜電特性,滿足一定的珊極寬度要求,可以表現(xiàn)為同樣工藝下,使用GAA架構(gòu)可以將芯片尺寸做的更小。

平面晶體管、FinFET與GAA FET

與5nm制造工藝相比,三星的3nm GAA技術(shù)的邏輯面積效率提高了35%以上,功耗降低了50%,性能提高了約30%。三星在去年6月正式宣布3nm工藝制程技術(shù)已經(jīng)成功流片。此外,三星還曾宣布將在 2022 年推出 3nm GAA 的早期版本,而其“性能版本”將在 2023 年出貨。

目前,在工廠方面,此前有消息稱三星可能會(huì)在美國(guó)投資170億美元建設(shè)3nm芯片生產(chǎn)線。在客戶方面,三星未有具體透露,但曾有消息稱高通、AMD 等臺(tái)積電重量級(jí)客戶都有意導(dǎo)入三星 3nm 制程,但介于上述提到的韓媒報(bào)道高通已將其3nm AP處理器的代工訂單交給臺(tái)積電,三星3nm客戶仍成謎。

英特爾

在Pat Gelsinger于去年擔(dān)任英特爾CEO之后,這家曾經(jīng)在代工領(lǐng)域試水的IDM巨頭又重新回到了這個(gè)市場(chǎng)。同時(shí),他們還提出了很雄壯的野心。

在本月18日投資人會(huì)議上,英特爾CEO Pat Gelsinger再次強(qiáng)調(diào),英特爾2nm制程將在2024年上半年可量產(chǎn),這個(gè)量產(chǎn)時(shí)間早于臺(tái)積電,意味2年后晶圓代工業(yè)務(wù)與臺(tái)積電競(jìng)爭(zhēng)態(tài)勢(shì)會(huì)更白熱化。

雖然在3nm工藝方面,英特爾沒(méi)有過(guò)多的透露,但是Digitimes去年的研究報(bào)告分析了臺(tái)積電、三星、Intel及IBM四家廠商在相同命名的半導(dǎo)體制程工藝節(jié)點(diǎn)上的晶體管密度問(wèn)題,并對(duì)比了各家在10nm、7nm、5nm、3nm及2nm的晶體管密度情況。

報(bào)告顯示,到了3nm節(jié)點(diǎn),臺(tái)積電的晶體管密度大約是2.9億個(gè)/mm2,三星只有1.7億個(gè)/mm2,英特爾將達(dá)到5.2億個(gè)/mm2。英特爾的晶體管密度比臺(tái)積電高出了超過(guò)79%,達(dá)到了三星2倍以上。因此就摩爾定律關(guān)注的晶體管密度指標(biāo)來(lái)看,在同一制程工藝節(jié)點(diǎn)上,英特爾相比臺(tái)積電、三星更新一代的制程工藝具有一定的優(yōu)勢(shì)。

在工廠方面,英特爾曾強(qiáng)調(diào)將斥資800億歐元在歐洲設(shè)廠,英特爾德國(guó)負(fù)責(zé)人Christin Eisenschmid受訪時(shí)透露,將在歐洲生產(chǎn)2nm或推進(jìn)更小的芯片。英特爾將2nm作為擴(kuò)大歐洲生產(chǎn)能力的重要關(guān)鍵,以避免未來(lái)在先進(jìn)技術(shù)競(jìng)爭(zhēng)中落后。

總的來(lái)說(shuō),在3nm節(jié)點(diǎn),臺(tái)積電、三星和英特爾誰(shuí)會(huì)是最后的贏家可能只有交給時(shí)間來(lái)判定,但從目前情勢(shì)來(lái)看,臺(tái)積電或略勝一籌。

3nm后的解法

3nm已經(jīng)到了摩爾定律的物理極限,往后又該如何發(fā)展?這已經(jīng)成為全球科研人員亟待尋求的解法。目前,研究人員大多試圖在晶體管技術(shù)、材料方面尋求破解之法。

GAA晶體管

上述三星在3nm制程中使用的GAA晶體管就是3nm后很好的選擇,GAA設(shè)計(jì)通道的四個(gè)面周圍有柵極,可減少漏電壓并改善對(duì)通道的控制,這是縮小工藝節(jié)點(diǎn)時(shí)的關(guān)鍵。據(jù)報(bào)道,臺(tái)積電在2nm工藝上也將采用GAA晶體管。

納米線

納米線是直徑在納米量級(jí)的納米結(jié)構(gòu)。納米線技術(shù)的基本吸引力之一是它們表現(xiàn)出強(qiáng)大的電學(xué)特性,包括由于其有效的一維結(jié)構(gòu)而產(chǎn)生的高電子遷移率。

最近,來(lái)自 HZDR 的研究人員宣布,他們已經(jīng)通過(guò)實(shí)驗(yàn)證明了長(zhǎng)期以來(lái)關(guān)于張力下納米線的理論預(yù)測(cè)。在實(shí)驗(yàn)中,研究人員制造了由 GaAs 核心和砷化銦鋁殼組成的納米線。最后,結(jié)果表明,研究人員確實(shí)可以通過(guò)對(duì)納米線施加拉伸應(yīng)變來(lái)提高納米線的電子遷移率。測(cè)量到未應(yīng)變納米線和塊狀 GaAs 的相對(duì)遷移率增加約為 30%。研究人員認(rèn)為,他們可以在具有更大晶格失配的材料中實(shí)現(xiàn)更顯著的增加。

堆疊叉片式晶體管技術(shù)

最近,英特爾一項(xiàng)關(guān)于“堆疊叉片式晶體管(stacked forksheet transistors)”的技術(shù)專利引起了人們的注意。

英特爾表示,新的晶體管設(shè)計(jì)最終可以實(shí)現(xiàn)3D和垂直堆疊的CMOS架構(gòu),與目前最先進(jìn)的三柵極晶體管相比,該架構(gòu)允許增加晶體管的數(shù)量。在專利里,英特爾描述了納米帶晶體管和鍺薄膜的使用,后者將充當(dāng)電介質(zhì)隔離墻,在每個(gè)垂直堆疊的晶體管層中重復(fù),最終取決于有多少個(gè)晶體管被相互堆疊在一起。

據(jù)了解,英特爾并不是第一家引用這種制造方法的公司,比利時(shí)研究小組Imec在2019年就曾提出這個(gè)方法,根據(jù) Imec 的第一個(gè)標(biāo)準(zhǔn)單元模擬結(jié)果,當(dāng)應(yīng)用于 2nm 技術(shù)節(jié)點(diǎn)時(shí),與傳統(tǒng)的納米片方法相比,該技術(shù)可以顯著提高晶體管密度。

垂直傳輸場(chǎng)效應(yīng)晶體管

垂直傳輸場(chǎng)效應(yīng)晶體管(VTFET)由IBM和三星共同公布,旨在取代當(dāng)前用于當(dāng)今一些最先進(jìn)芯片的FinFET技術(shù)。新技術(shù)將垂直堆疊晶體管,允許電流在晶體管堆疊中上下流動(dòng),而不是目前大多數(shù)芯片上使用的將晶體管平放在硅表面上,然后電流從一側(cè)流向另一側(cè)。

據(jù) IBM 和三星稱,這種設(shè)計(jì)有兩個(gè)優(yōu)點(diǎn)。首先,它將允許繞過(guò)許多性能限制,將摩爾定律擴(kuò)展到 1 納米閾值之外。同時(shí)還可以影響它們之間的接觸點(diǎn),以提高電流并節(jié)約能源。他們表示,該設(shè)計(jì)可能會(huì)使性能翻倍,或者減少85%的能源消耗。

其實(shí),對(duì)于3nm以后先進(jìn)制程如何演進(jìn),晶體管制造只是解決方案的一部分,芯片設(shè)計(jì)也至關(guān)重要,需要片上互連、組裝和封裝等對(duì)器件和系統(tǒng)性能的影響降至最低。

文章來(lái)源:半導(dǎo)體行業(yè)觀察(ID:icbank)綜合自tomshardware等

-

臺(tái)積電

+關(guān)注

關(guān)注

44文章

5646瀏覽量

166589 -

晶體管

+關(guān)注

關(guān)注

77文章

9698瀏覽量

138297 -

場(chǎng)效應(yīng)晶體管

+關(guān)注

關(guān)注

6文章

364瀏覽量

19523 -

三星

+關(guān)注

關(guān)注

1文章

1537瀏覽量

31274

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

三星宣布:DRAM工藝可達(dá)10nm

三星電子宣布開(kāi)發(fā)出業(yè)界首個(gè)12層3D-TSV技術(shù) 將鞏固其在高端半導(dǎo)體市場(chǎng)的領(lǐng)先地位

三星正式宣布3nm成功流片,性能將完勝臺(tái)積電

三星3nm芯片良品率僅達(dá)2成,與臺(tái)積電的差距更大了

三星3nm芯片開(kāi)始量產(chǎn),采用GAA晶體管,提升巨大

三星3nm芯片量產(chǎn) 2nm芯片還遠(yuǎn)嗎

三星即將公布首顆3nm芯片,或?qū)⑴まD(zhuǎn)訂單數(shù)量

三星正式宣布3nm芯片出貨,首位客戶為一家中國(guó)企業(yè)

三星已找到第二家3nm芯片客戶 產(chǎn)能開(kāi)始供不應(yīng)求

三星在3nm率先使用GAA 是否更具競(jìng)爭(zhēng)力

臺(tái)積電3nm和5nm同期良率相當(dāng),3nm將大量生產(chǎn)

三星3nm GAA商業(yè)量產(chǎn)已經(jīng)開(kāi)始,首個(gè)客戶是中國(guó)礦機(jī)芯片公司

三星宣布業(yè)界首個(gè)3nm級(jí)制造技術(shù)開(kāi)始大量生產(chǎn)

三星宣布業(yè)界首個(gè)3nm級(jí)制造技術(shù)開(kāi)始大量生產(chǎn)

評(píng)論