芯片制造商開始重新審視異構(gòu)系統(tǒng)中應(yīng)該使用多少暗硅,在哪里工作得最好,以及有哪些替代方案可用——這是摩爾定律擴(kuò)展放緩以及SoC日益分解的直接后果。

暗硅的概念已經(jīng)存在了幾十年,但隨著物聯(lián)網(wǎng)的引入,所有東西都必須安裝在單個(gè)芯片上,并使用小電池工作,暗硅才真正開始發(fā)展起來(lái)。事實(shí)證明,對(duì)于智能手表和手機(jī)的初始版本來(lái)說(shuō),這種做法是存疑的。而當(dāng)時(shí)最好的解決方案是關(guān)閉任何基本應(yīng)用不需要的電路。

然而,其他問(wèn)題接踵而至。例如,當(dāng)設(shè)備重新通電時(shí),浪涌電流(特別是那些需要更快打開的設(shè)備)會(huì)給電路帶來(lái)壓力,從而導(dǎo)致芯片損壞。因此,雖然關(guān)閉芯片的某些部件的電源可以減少老化,但快速打開它們也可能引發(fā)問(wèn)題。在過(guò)去十年中,通過(guò)低功耗芯片的工程設(shè)計(jì),其中大部分問(wèn)題已經(jīng)得到解決,并且暗硅加上極其高效的設(shè)計(jì),推動(dòng)了下一代移動(dòng)設(shè)備的發(fā)展,同時(shí)也對(duì)極大縮減了數(shù)據(jù)中心的能源成本。

現(xiàn)在的問(wèn)題是,除了延長(zhǎng)兩次充電之間的時(shí)間之外,還能做些什么,而僅僅添加更多的暗硅并不能解決這個(gè)問(wèn)題。相反,人們更加關(guān)注滿足應(yīng)用需求的芯片設(shè)計(jì),而這得益于從設(shè)計(jì)到制造流程的一系列開發(fā)。其中:

整個(gè)生態(tài)系統(tǒng)一直在圍繞先進(jìn)封裝發(fā)展和高效設(shè)計(jì)工具,OSAT和代工廠提供了經(jīng)過(guò)硅驗(yàn)證的分立元件(如Chiplet)以及各種封裝方法。這使得芯片制造商能夠開發(fā)更復(fù)雜的器件,同時(shí)還可以更有效地為特定領(lǐng)域應(yīng)用進(jìn)行分區(qū)和優(yōu)先排序。

先進(jìn)的封裝為更短的信號(hào)路徑和更快的互連開辟了道路。與大型平面芯片相比,信號(hào)在封裝中的傳播距離可能更短,并且這些信號(hào)可以通過(guò)利用先進(jìn)的互連和新材料,從而在驅(qū)動(dòng)時(shí)實(shí)現(xiàn)更快速、功耗更低的數(shù)據(jù)傳輸。

超低功耗設(shè)計(jì)和各種功能(例如接近閾值計(jì)算)在很大程度上仍處于觀望狀態(tài),然而目前卻正在受到更廣泛的關(guān)注。此外,在過(guò)去十年中,電池內(nèi)部的密度以每年平均5%至6%的速度增長(zhǎng),使設(shè)備能夠使用相同尺寸甚至更小的電池做更多的事情。雖然終端設(shè)備的外形尺寸往往相對(duì)一致,但可以在不影響電池壽命的情況下將更多設(shè)備封裝在設(shè)備內(nèi)部。

所有這些變化都是日積月累的。因此,與其關(guān)閉芯片的大部分電源,不如使用較小的芯片或Chiplet來(lái)完成更多工作,這可以更具成本和能效。此外,芯片中的各種功能可以在最佳工藝節(jié)點(diǎn)上開發(fā),權(quán)衡成本、用例、靜態(tài)電流泄漏和尺寸等因素。

“還有更多各種各樣的解決方案,”Arm的研發(fā)研究員Rob Aitken表示。“暗硅背后的部分想法是有一個(gè)固定的功率預(yù)算,特別是對(duì)于移動(dòng)計(jì)算。但是,如果縮小設(shè)備,同時(shí)提高頻率,那么功率就不會(huì)真正改善。相反,最終會(huì)得到這個(gè)空白空間,并且有各種各樣的想法來(lái)解決這個(gè)問(wèn)題。

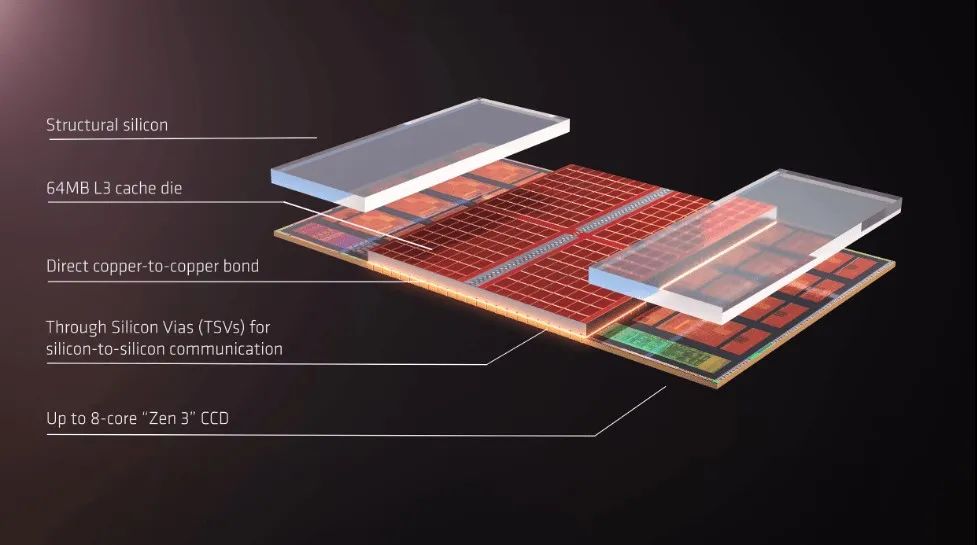

對(duì)于智能手機(jī)和可穿戴設(shè)備來(lái)說(shuō),暗硅是一種經(jīng)過(guò)驗(yàn)證的解決方案,但它不是最有效的解決方案。還有其他選擇,從限制各種組件尺寸到將它們分散在封裝中,從而在增加密度時(shí)減少熱效應(yīng)。這對(duì)于內(nèi)存尤其有價(jià)值,因?yàn)閮?nèi)存在較低溫度下可以更有效地運(yùn)行。因此,當(dāng)附近的電路斷電時(shí),內(nèi)存可能會(huì)保持冷卻,但浪涌電流會(huì)很快使其過(guò)熱。更好的選擇是將內(nèi)存與先進(jìn)封裝中的主動(dòng)邏輯物理分離。

“如果溫度太接近最大允許的工作范圍,你可能不得不更頻繁地刷新內(nèi)存,”Rambus的杰出發(fā)明家Steven Woo指出。“當(dāng)內(nèi)存器件過(guò)熱時(shí),最終可能會(huì)失效。如果器件溫度升高,那就不得不做所謂的節(jié)流。注意縮短以最佳性能運(yùn)行的時(shí)間,或者在短時(shí)間內(nèi)運(yùn)行,讓其再次冷卻下來(lái)。”

所有這些技術(shù)以及其他發(fā)展使移動(dòng)設(shè)備能夠進(jìn)行比過(guò)去更密集的計(jì)算,而不會(huì)耗盡。“在移動(dòng)領(lǐng)域,功率實(shí)際上升了,”Arm的Aitken認(rèn)為。“與15年前相比,如今的芯片消耗了更多的功率。由于電池技術(shù)的發(fā)展,以及更多的物理區(qū)域,可以讓器件更有效地散熱,從而提高了芯片功率。”

通過(guò)三維層級(jí)規(guī)劃隔離芯片的各個(gè)部分,并采用各種技術(shù),如動(dòng)態(tài)電壓頻率調(diào)節(jié),以及一些暗硅,可以更有效地進(jìn)行熱管理。它也可以使用更少的硅面積來(lái)完成,這提高了性能,并為相同器件中的其他功能和特性打開了大門。

這種方法還有其他好處。“過(guò)去有理由選擇越來(lái)越大的芯片,這樣你就可以將更多的功能集成到單個(gè)芯片中,”Fraunhofer IIS自適應(yīng)系統(tǒng)部門工程設(shè)計(jì)方法負(fù)責(zé)人Roland Jancke表示。“如果你不需要硅的某些部分,那么你可以關(guān)閉它們以節(jié)省電力。但是還有其他原因使用較小的芯片。例如,相較于數(shù)字電路,如果在設(shè)計(jì)中包含模擬電路,則通常位于成熟工藝節(jié)點(diǎn)中,因此它會(huì)占用更多區(qū)域(這使得減小數(shù)字元件的尺寸更具優(yōu)勢(shì))。而對(duì)于RF而言,則需要大量的功率。Chiplet也有安全優(yōu)勢(shì),很難復(fù)制整體系統(tǒng)功能,僅在以相同方式將相同部分集成到相同封裝中時(shí),它才有效。如果你使用這些芯片中的任何一個(gè)都失敗了,那么你就錯(cuò)過(guò)了整體功能。

人工智能的影響

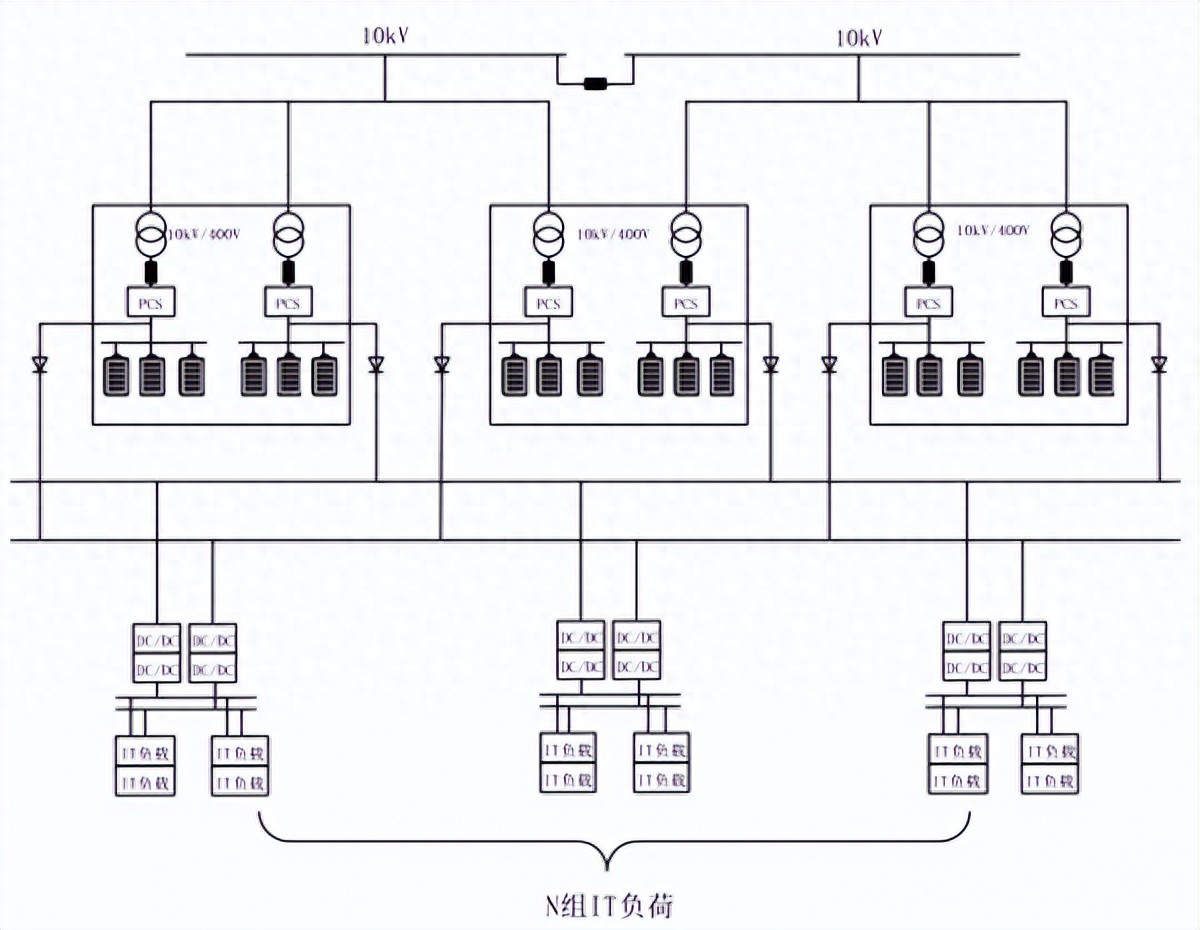

重新思考關(guān)閉部件以及關(guān)閉時(shí)間的驅(qū)動(dòng)因素之一涉及人工智能和機(jī)器學(xué)習(xí),其中芯片設(shè)計(jì)旨在實(shí)現(xiàn)最大的性能和吞吐量。對(duì)于需要非常快速地處理大量數(shù)據(jù)的大型數(shù)據(jù)中心尤其如此。通常,這涉及并行工作的強(qiáng)大處理器內(nèi)核,其中一些內(nèi)核是專門為這些數(shù)據(jù)中心工作負(fù)載設(shè)計(jì)的,通常與GPU、CPU、某種類型的NPU和DSP結(jié)合使用。問(wèn)題是這些設(shè)備依賴于穩(wěn)定的數(shù)據(jù)流,并且該數(shù)據(jù)流并不總是一致地流動(dòng)。

“如果有兩種解決方案,其中一種解決方案更有效地使用晶體管,那么每美元和每瓦特將獲得更多的吞吐量,”Flex Logix首席執(zhí)行官Geoff Tate指出。“因此,從客戶的角度來(lái)看,采用暗硅是不可取的。很難開發(fā)出高利用率的架構(gòu),但利用率越高越好。

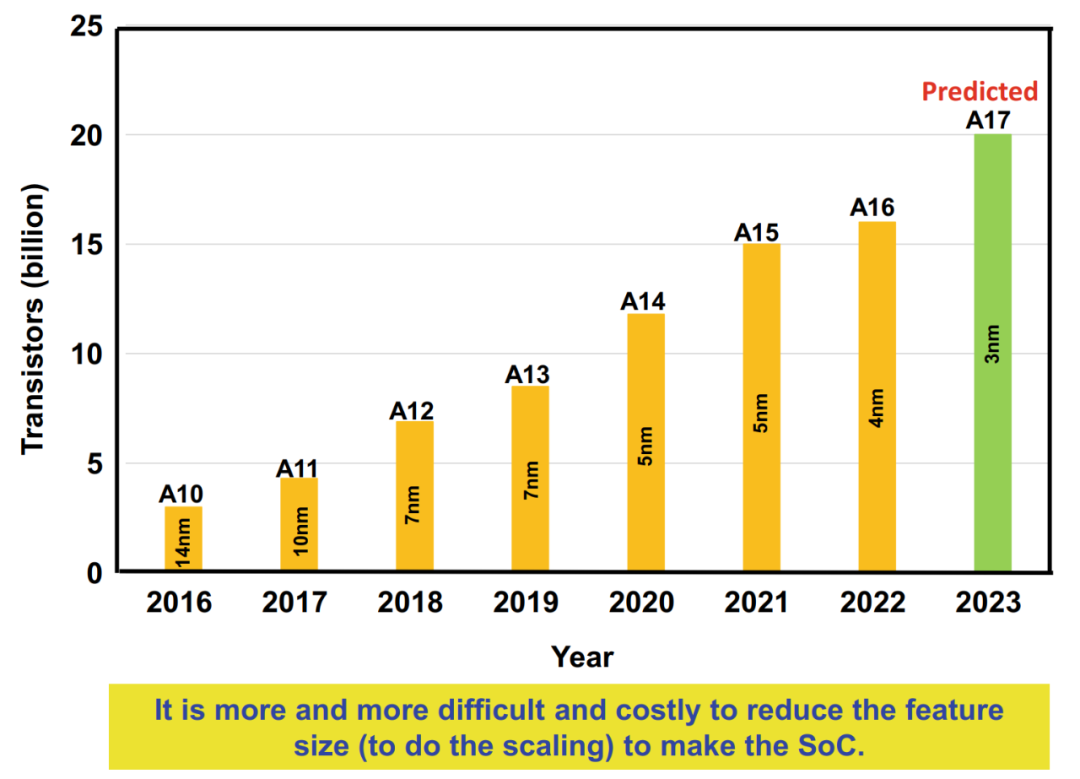

在過(guò)去的五年里,隨著人工智能變得越來(lái)越普遍,人們對(duì)什么是最佳方案的看法改變了。“在人工智能的早期階段,第一個(gè)挑戰(zhàn)就是讓一些功能發(fā)揮作用并改進(jìn)模型,使它們?cè)絹?lái)越好,并沿著學(xué)習(xí)曲線上升,” Tate指出。“在數(shù)據(jù)中心領(lǐng)域,其擁有巨大的預(yù)算和巨額利潤(rùn),這使他們能夠做一些以前無(wú)法做到的事情。但是,當(dāng)我們尋求將AI部署到大批量應(yīng)用,且對(duì)價(jià)格更敏感的解決方案中時(shí),客戶將尋找能夠?yàn)槠涔β暑A(yù)算和金錢預(yù)算提供最大的推理性能的供應(yīng)商,我們看到的大多數(shù)企業(yè)在達(dá)到他們的資金預(yù)算之前就達(dá)到了功率預(yù)算。這不僅僅是出于成本原因而有效地使用晶體管。擁有的晶體管越多,泄漏就越多。因此,如果你能用更少的晶體管完成工作,它將更加節(jié)能。”

在人工智能世界中,“暗硅”也可以具有另一種含義。“盡管供應(yīng)商試圖提供所有芯片和所有馬力,但當(dāng)你試圖運(yùn)行實(shí)際的神經(jīng)網(wǎng)絡(luò)模型時(shí),甚至無(wú)法獲得接近40%的系統(tǒng),”AMD數(shù)據(jù)中心人工智能和計(jì)算市場(chǎng)高級(jí)總監(jiān)Nick Ni表示。“引擎可以非常快,但如果你沒(méi)有要處理的數(shù)據(jù),那么它們就閑置了。這就是導(dǎo)致暗硅的原因。”

圖 1:AMD 的 3D V-Cache 使用堆疊在處理器上的緩存小芯片(圖源:AMD)

挑戰(zhàn)在于徹底了解需要處理的上下文和數(shù)據(jù)量,然后圍繞這些因素設(shè)計(jì)芯片。AMD收購(gòu)Xilinx的原因之一,以及英特爾收購(gòu)Altera的原因之一,是能夠微調(diào)其中一些設(shè)備的使用方式。可編程邏輯可以根據(jù)需要?jiǎng)討B(tài)重新配置和調(diào)整大小,因此可以根據(jù)需要使用小型FPGA,而不是巨型FPGA。雖然巨型FPGA的效率永遠(yuǎn)不如硬連線ASIC,但較小的可編程邏輯芯片可用于減少未充分利用或未利用的硅的數(shù)量。

“雖然能夠?yàn)槊總€(gè)市場(chǎng)構(gòu)建定制ASIC會(huì)很好,但其中一些用例是如此多樣化,以至于市場(chǎng)變得越來(lái)越小,而構(gòu)建ASIC的成本正在上升,”Rambus的Woo表示。“因此,F(xiàn)PGA與x86結(jié)合使用是有意義的。您可以加載位文件以用于特定于市場(chǎng)的工作,然后利用 x86 的通用基礎(chǔ)結(jié)構(gòu)來(lái)完成其他所有操作。”

Chiplet架構(gòu)的影響

Chiplet增加了另一個(gè)級(jí)別的靈活性,因?yàn)樾酒叽缈梢愿鶕?jù)特定功能所需的任何條件進(jìn)行調(diào)整。這意味著可以完全消除芯片中未使用的部分,而不是將其置于睡眠狀態(tài),并且可以將附加功能放在不同的小芯片上。

“芯片尺寸是采用Chiplet的主要驅(qū)動(dòng)力之一,”TechSearch總裁Jan Vardaman在最近的一次演講中說(shuō)。“如今,GPU和CPU的芯片尺寸非常大,我們確實(shí)必須擁有更多的晶體管。只是我們必須弄清楚如何經(jīng)濟(jì)地將所有這些晶體管放在一起并發(fā)揮作用。因此,我們?cè)谕苿?dòng)Chiplet采用方面所做的額外工作將使我們能夠制作出更高密度的更精細(xì)的封裝。您可以做一些提高電源效率的事情,這在我們的許多應(yīng)用中都非常重要。”

關(guān)鍵是能夠以最有效的方式將各個(gè)部分組合在一起。“我們必須能夠以一種新的方式思考設(shè)計(jì)。這是一個(gè)系統(tǒng)架構(gòu),“Vardaman表示。“因?yàn)槟愕玫降氖且粋€(gè)更小的模具,這可以提高產(chǎn)量,所以你將使用最先進(jìn)的節(jié)點(diǎn)來(lái)制造需要這些節(jié)點(diǎn)的零件。您不會(huì)在高性能邏輯節(jié)點(diǎn)中制造芯片的模擬部分。您將在其他節(jié)點(diǎn)中將其鑄造,因?yàn)樗阋恕D阋阉羞@些放在一起。小芯片是硬 IP 塊。它必須共同優(yōu)化。所有這些東西都可以一起工作。你不能孤立地設(shè)計(jì)這些東西。”

在這種情況下,暗硅只是降低功耗的另一種選擇,而不一定是最好的選擇。雖然它可以為特定功能提供儲(chǔ)備計(jì)算能力,但它不是設(shè)計(jì)復(fù)雜系統(tǒng)的最有效方法。

總結(jié)

將更多功能封裝到芯片上的能力不斷削弱,但功耗和性能優(yōu)勢(shì)也在不斷縮小。因此,芯片制造商正在尋求通過(guò)先進(jìn)封裝來(lái)繼續(xù)降低功耗、提升性能。但在封裝中,暗硅并不如單個(gè)高性能芯片那么有吸引力,后者的尺寸更具普適性,并且數(shù)量在十億芯片范圍內(nèi)。即使在最理想的條件下,暗硅似乎也顯示出它的年齡。

“我們正處于這種暗硅軌跡中,”Aitken稱。“有一堆東西進(jìn)入了暗硅思維過(guò)程,這些東西已經(jīng)逐漸成為主流。您將構(gòu)建一個(gè)具有許多不同核心功能的芯片。但是,如何始終打開所有功能以最大化提高計(jì)算性能仍然是一個(gè)非常困難的問(wèn)題。這是你可能不想回答的問(wèn)題,因?yàn)樗鼤?huì)產(chǎn)生大量的熱量,無(wú)論如何你都無(wú)法處理。”

審核編輯 :李倩

-

芯片

+關(guān)注

關(guān)注

456文章

51075瀏覽量

425873 -

生態(tài)系統(tǒng)

+關(guān)注

關(guān)注

0文章

703瀏覽量

20759 -

異構(gòu)系統(tǒng)

+關(guān)注

關(guān)注

0文章

8瀏覽量

7652 -

異構(gòu)集成

+關(guān)注

關(guān)注

0文章

34瀏覽量

1910

原文標(biāo)題:異構(gòu)集成趨勢(shì)下,如何解決暗硅效應(yīng)?

文章出處:【微信號(hào):CloudBrain-TT,微信公眾號(hào):云腦智庫(kù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

磁集成趨勢(shì),平面變壓器寄生參數(shù)如何解決?

先進(jìn)封裝技術(shù)-17硅橋技術(shù)(下)

先進(jìn)封裝技術(shù)-16硅橋技術(shù)(上)

人工智能應(yīng)用中的異構(gòu)集成技術(shù)

磁極是如何解決磁集成產(chǎn)品電磁干擾的?

異構(gòu)集成封裝類型詳解

實(shí)現(xiàn)異構(gòu)集成與小芯片優(yōu)勢(shì)的關(guān)鍵“互連”

日月光應(yīng)邀出席SEMICON China異構(gòu)集成(先進(jìn)封裝)國(guó)際會(huì)議

硅光集成芯片的用途有哪些

Cadence與Intel代工廠攜手革新封裝技術(shù),共推異構(gòu)集成多芯粒架構(gòu)發(fā)展

Cadence與Intel代工廠合作通過(guò)EMIB封裝技術(shù)實(shí)現(xiàn)異構(gòu)集成

多核異構(gòu)通信框架(RPMsg-Lite)

一文解析異構(gòu)集成技術(shù)中的封裝天線

入門:霍爾效應(yīng)傳感器的基礎(chǔ)知識(shí)

異構(gòu)集成趨勢(shì)下,如何解決暗硅效應(yīng)?

異構(gòu)集成趨勢(shì)下,如何解決暗硅效應(yīng)?

評(píng)論