調試是嵌入式設計的重要組成部分;必須跨越硬件/軟件鴻溝的一種。在系統級別,嵌入式設計的功能越來越多地由固件定義,因此避免錯誤需要具有特定學科的工程師在項目的設計階段密切合作。這也可能意味著在不可避免地出現錯誤時抵制指責的沖動。

或許正是軟件定義硬件的本質使現代嵌入式設計成為一個如此有趣的職業。每個新的微控制器 (MCU) 似乎都提供了更高的集成度和更高級的功能,但在它被編程之前它完全沒有意義。雖然這種級別的集成和配置顯然是一個促成因素,并且正在為產品設計帶來巨大的進步,但它有時會給工程師帶來無法預料的問題。

MCU 等嵌入式組件提供的功能級別和可配置特性也在不斷提高,這些組件提供了許多并非所有設計都需要的特性。這些額外的功能可能會被忽略,很少會引起問題。

正如大多數工程師所理解的那樣,這些功能通常由可以通過軟件修改的寄存器控制。因此,它們在上電時將具有默認設置,如果保持不變,將繼續在這些默認設置下運行。在許多情況下,這可能不會造成問題,但如果這些功能仍未使用并且可能未經測試,那么它們的影響可能會以某種無法預料的方式感受到。系統中可能會出現錯誤,這是由可能被忽略的完全合法的功能引起的。

即使在理想條件下,查找故障也可能很困難、耗時且成本高昂。通常,故障將通過其影響來識別,這將提供足夠的證據讓工程師能夠追蹤原因。這個原因是硬件還是軟件相關在很大程度上無關緊要,但也許仍然存在爭議;重要的是它被找到并糾正了。

如果故障的原因是未正確初始化的低級功能,那么找到它可能會變得更具挑戰性。了解硬件平臺的初始狀態如何影響整個設計需要對整個系統有更高的了解,并且追蹤這些難以捉摸的條件確實會消耗資源。

例如,考慮訪問串行閃存的 MCU 上的 SPI 總線,這是在許多嵌入式系統中使用的相對簡單的功能。如果在存儲的值中檢測到錯誤,則表明內存而不是 MCU 出現了故障。當從閃存的狀態寄存器連續讀取顯示它正在檢測讀/寫錯誤時,這是一位客戶的經驗。可以理解的是,假設存儲設備出現故障,這一理論得到了證實,即如果在狀態寄存器讀取之間引入短暫的延遲,檢測到的故障數量似乎會減少。此外,電源循環似乎可以暫時清除故障。

工程師們認為這些癥狀表明串行存儲器出現故障,盡管它仍然在其指定的周期限制內,僅完成了大約 60k 的寫入周期。當串行閃存設備返回 Adesto 進行進一步測試時,即使執行了超過 300k 的寫入周期,也沒有發現故障。

為了追查真正的故障,Adesto 工程師調查了客戶的應用并探測了 SPI 信號。看起來是內存設備的故障,實際上是系統噪音問題,而且很容易糾正。雖然部分原因是 MCU 和閃存之間的 PCB 走線阻抗不匹配,但噪聲并不完全是 PCB 設計不良或信號完整性問題的結果。

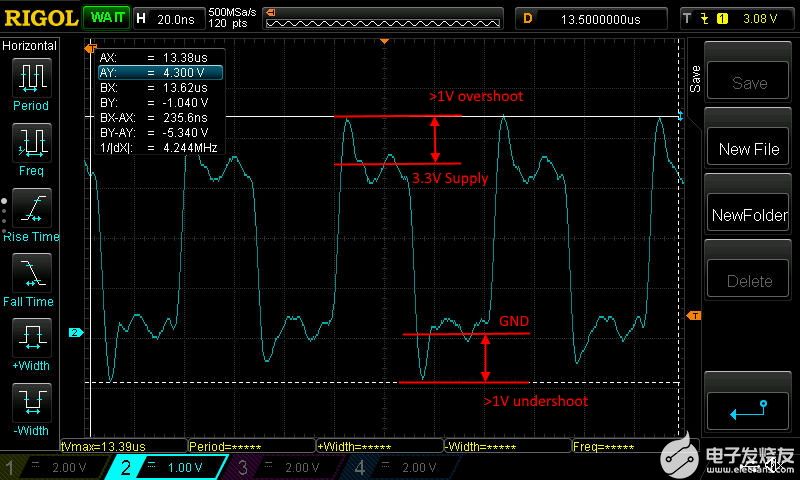

盡管看起來是 PCB 或電路設計問題,但噪聲實際上是 SPI 信號上的過沖和下沖,這是由信號驅動強度過大引起的。過沖足以破壞閃存設備的電荷泵并導致讀寫錯誤。在某些情況下,SPI 信號上的過沖和下沖也可以解釋為信號轉換,這也可能導致讀取或寫入錯誤。

顯示 SPI 線上存在的過沖和下沖的跟蹤圖像

一種可能的解決方案是在信號跡線上放置一個 RC 電路,以減慢轉換速度。然而,人們發現該設計基于一個相對較新的 MCU,它允許在固件中修改 I/O 引腳的驅動強度。降低信號的驅動強度足以消除 SPI 信號線上的過沖和下沖,有效消除系統級噪聲源。

這里最重要的一點并不是閃存設備正在盡最大努力應對大量系統噪聲,而是 MCU 上的可配置功能可能會引入很容易被解釋為單獨部件中的故障的影響的設計。在這種情況下,通過穩健的設計方法檢測到故障,并通過 Adesto 工程師的勤奮解決。

也許這里真正的教訓是,看似硬件故障的問題可以通過軟件輕松修復。一個組件中看似故障的情況可以追溯到另一個組件中的錯誤配置。硬件和軟件工程師以及客戶和供應商之間的工作關系應該足夠牢固,以承受最新技術設計可能帶來的挑戰。即使默認設置旨在提供幫助,也應該對其進行驗證。優化這些設置可以顯著提高系統性能和可靠性。

作者:Paul Hill Gordon MacNee

審核編輯:郭婷

-

mcu

+關注

關注

146文章

17301瀏覽量

352131 -

嵌入式

+關注

關注

5089文章

19169瀏覽量

306757 -

SPI

+關注

關注

17文章

1720瀏覽量

91914

發布評論請先 登錄

相關推薦

物聯網就業有哪些高薪崗位?

網關在物聯網中的應用

socket 在物聯網中的應用

物聯網學習路線來啦!

EDA在物聯網設計中的應用

MCU在物聯網中的應用前景

MQTT調試助手中文版(物聯網開發必備)

什么是物聯網技術?

調試跨越物聯網中的硬件

調試跨越物聯網中的硬件

評論