對于任何低功耗設計,設計人員都可以選擇選擇低功耗組件或關閉外圍設備的電源。在考慮非易失性閃存的選擇時,設計人員可以使用這兩個相同的選項——從系統操作、功耗和可靠性的角度來看,每個選項都有其優點和缺點。但是,還有另一種可用的低功耗解決方案具有簡化系統設計和提高可靠性的額外好處。

使用外部閃存的典型設計

盡管具有嵌入式閃存的微控制器 (MCU) 設備激增,并且它們可以在多種低功耗模式下運行,但出于擴展原因,越來越多的系統仍然需要外部閃存設備來補充片上閃存。無線 (OTA) 更新、數據記錄、用戶配置文件和其他應用程序都促成了這一點。

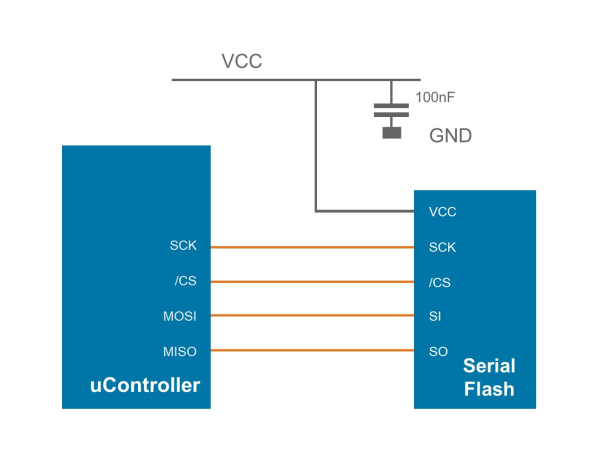

對于許多基本應用,圖 1 所示的典型設計是可接受的解決方案。

圖 1:使用外部閃存的典型設計

在該方案中,電源是持續提供給閃存設備的。當串行閃存芯片選擇信號 ( /CS ) 未置位且存儲器處于待機模式時,待機電流通常約為 ~10uA 至 ~20uA。還有一個選項可以進入命令驅動的深度掉電模式,該模式將待機功耗進一步降低到通常約為 2uA 至 ~5uA。

然而,在其他一些系統中,例如能量收集或小型電池供電設備,即使 2uA 也可能仍然代表過高的電流消耗值。而且,如果不經常使用閃光燈或很少使用閃光燈,則長時間待機 2uA 可能會過度消耗電源和能量儲備,從而降低整體電池/系統的使用壽命。

具有簡單電源開關控制電路的外置閃光燈

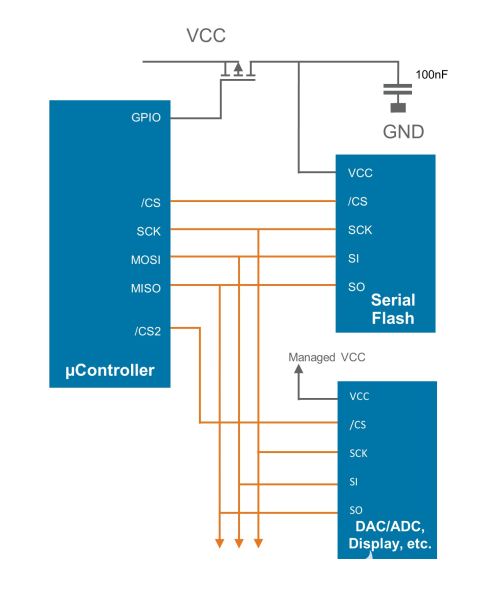

為了提高系統電池壽命,設計人員通常會實現一個簡單的電源開關控制電路,如圖 2 所示。閃存設備的電源通過一個備用 MCU GPIO 引腳在軟件控制下進行管理,以便僅在需要時為串行閃存供電。

圖2:串口閃光燈外接電源控制電路

不要太舒服!

加入 MOSFET 完全關斷串行存儲器 VCC 會使存儲器的待機功耗降低到零,但 MOSFET 本身有潛在的漏電流和漏電流,在某些情況下高達 1.5uA,僅好 500nA比正常待機時的內存高達 2uA。

可靠性問題

利用帶有控制柵極的外部 FET 或 LDO 來管理外圍設備 VCC 引腳的電源的解決方案正變得越來越普遍;但是,這也需要一個額外的 MCU GPIO 引腳。

更重要的是,當多個外圍設備共享一個公共 SPI 總線并且各個設備已切換 VCC 引腳時,必須小心。

在圖 2 所示的配置中,如果關閉 flash 的 VCC 并且 VCC = 0V,繼續訪問 SPI 總線上的其他 SPI 控制設備(例如 DAC/ADC/Display)將導致總線信號也出現在串行閃存 SPI 引腳。

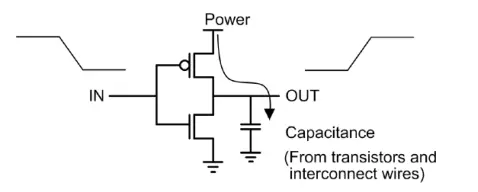

在這種情況下,當閃存(或其他設備)的 VCC 為零時,外圍 SPI 總線引腳上的高 VCC 將導致 I/O 保護二極管正向偏置,并且設備可能會通過 I/O 汲取電力自己別針。這可能會導致短期或長期的可靠性問題和操作問題。

對于任何其他可能在閃光燈關閉時通電的情況,雜散電容也應最小化,以使任何引腳上的電壓不超過 VCC 引腳上的電壓。或者,設計人員可以考慮更繁瑣的解決方案,并為可以關閉 VCC 的串行存儲器添加單獨的 SPI 總線。仔細的硬件和軟件設計和實施可以克服所有這些挑戰和問題。然而…

超深度斷電 (UDPD) 選項

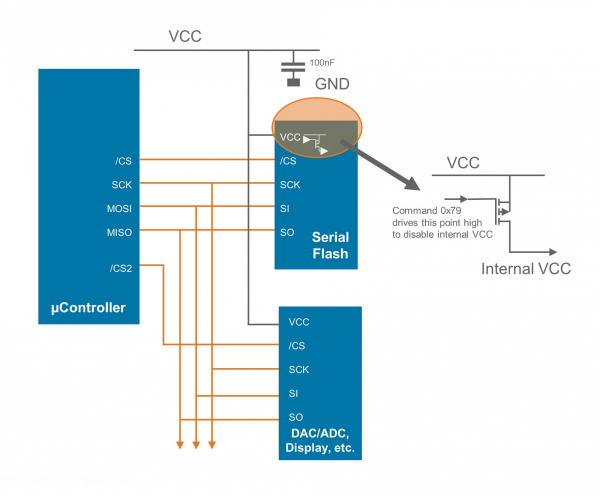

…通過將電源控制電路集成到存儲設備本身并允許主設備 (MCU) 通過串行閃存 SPI 命令接口控制電源模式,可以實現更高效的解決方案。這樣可以節省 GPIO 引腳用于其他用途。請參見圖 3 中的圖表。

該解決方案的好處是:

它比標準的深度掉電消耗更少的功率。

它不需要外部 MOSFET。

它允許設計人員將相同的 SPI 總線用于其他外設,從而簡化設計。

它減輕了可靠性問題,因為 VCC 引腳始終連接到 VCC,并且電源由內部控制。

圖 3:內部管理并通過 SPI 命令接口驅動的串行存儲器電源控制

此解決方案的其他好處是:

它節省了一個用于切換外部 MOSFET 或 LDO 的 GPIO 引腳。

它簡化了軟件,因為它消除了多余的 MOSFET/LDO 控制程序。

它提供了更簡潔的 PCB 設計并減少了 BoM。

除了待機和深度掉電模式外,Adesto Fusion、FusionHD? (AT25XExxx) 和 DataFlash? (AT45DBxxxE/F) 閃存器件還提供這種超深度掉電模式。待機和深度掉電模式導致的電流消耗與其他行業標準閃存設備相似或更低。

Ultra Deep Power Down 模式將 Fusion 的靜態電流降至 200nA 以下,FusionHD 的靜態電流降至 100nA,DataFlash 的靜態電流降至 400nA 以下。

使用超深度掉電

實現 UDPD 模式很簡單。我們在應用筆記 AN111中概述了詳細說明。

結論

選擇合適的低功耗存儲器可能是能量收集或小型電池供電設備的關鍵系統設計因素。了解和管理 SPI 總線上組件的交互對于提高功能和可靠性也很重要。通過考慮如何在實際系統中實現存儲器,Adesto 的串行閃存解決方案為設計人員提供了簡化設計、降低風險、提高可靠性和節省外部組件的選項,從而大大簡化了電路并降低了材料成本。

作者:Paul Hill ,Gordon MacNee

審核編輯:郭婷

-

存儲器

+關注

關注

38文章

7484瀏覽量

163772 -

ldo

+關注

關注

35文章

1941瀏覽量

153316 -

電池

+關注

關注

84文章

10564瀏覽量

129505

發布評論請先 登錄

相關推薦

MAX32675C超低功耗Arm? Cortex?-M4F MCU

物聯網系統中TCP低功耗產品長連接狀態下降低功耗功能的實現方案

柵極驅動芯片選型低功耗原因

利用超低功耗單片機 MSP430 作為系統伴隨芯片應用報告

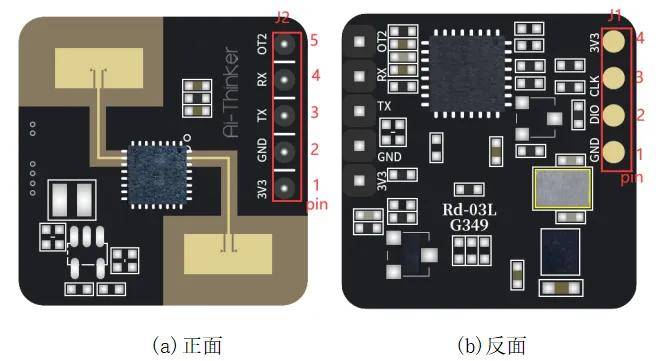

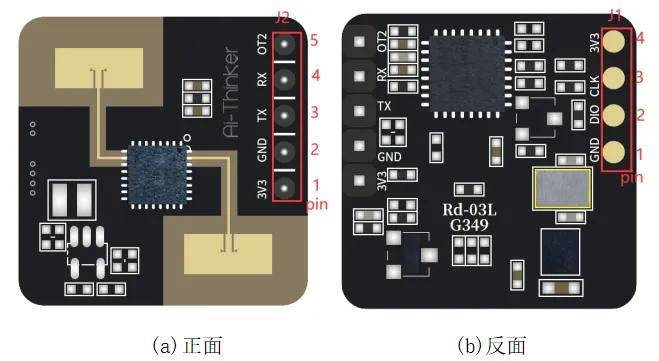

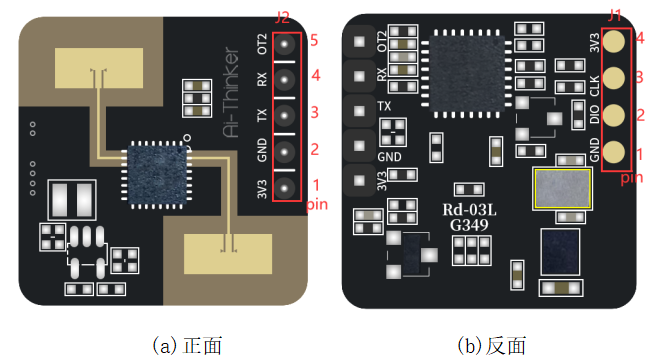

0.1mA!24GHz超低功耗人體存在毫米波雷達模組

適用于超低功耗和低功耗應用的獨特高效隔離式DC/DC轉換器

400nA超低功耗升壓DC/DC轉換器 大幅提升電池驅動時間

DA16600 超低功耗 Wi-Fi + 藍牙低功耗模塊開發套件數據手冊

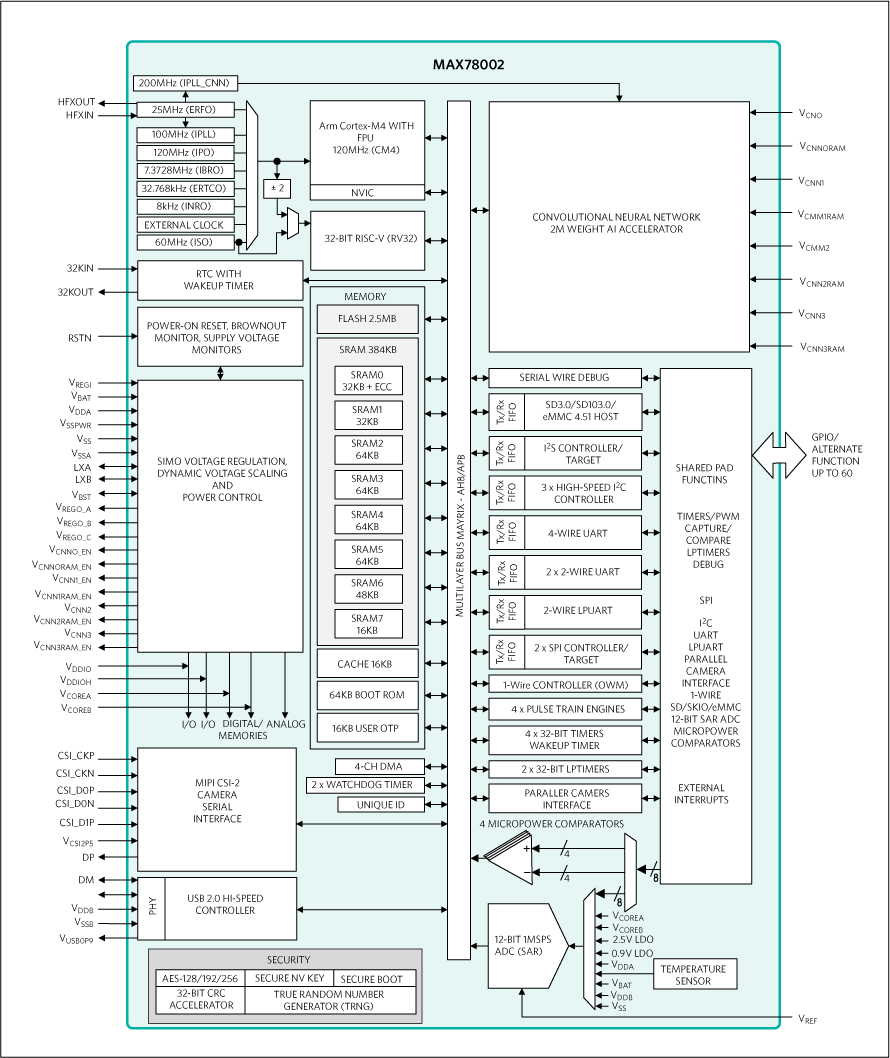

芯品#MAX78002 新型AI MCU,能夠使神經網絡以超低功耗運行

安信可Rd-03L檢測使用—— 超低功耗實現人體存在檢測,上位機配置快速上手

0.1毫安!超超超超超低功耗安信可雷達模組Rd-03L

在簡化系統設計的同時實現超低功耗運行

在簡化系統設計的同時實現超低功耗運行

評論