從歷史上看,服務器將時間聚合到系統板上。現代服務器更普遍地將功能模塊化并將設備遷移到不同的機架,例如 CPU、SSD、GPU、加速器、DRAM 卡等的托盤,如圖 1 所示。

圖 1. 分解系統

對系統進行電源循環是一種理想的能力,但在分解系統中,調整整個系統的輸入信號和電源序列變得更加復雜。理想情況下,系統始終通電;但在實踐中,電源開啟和輸出時鐘準備開啟之間的時間差會有所不同。讓我們來看一些與系統時鐘設計相關的示例案例:

情況 1:無 VDD

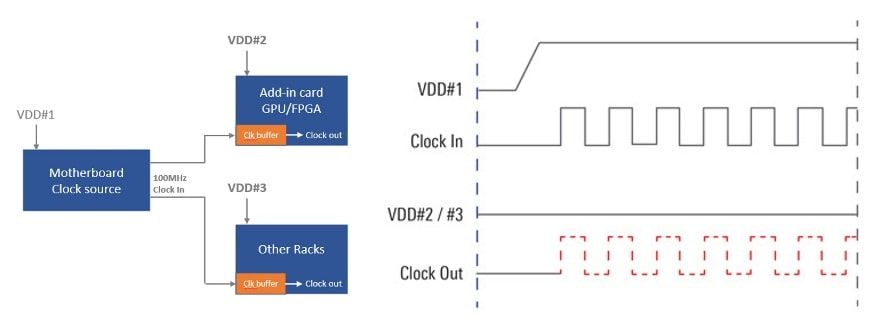

圖 2 描述了在電源準備好之前主板將其時鐘發送到其他機架和附加卡的場景。接收端的時鐘緩沖器可能在其 VDD 開啟之前就開始接收時鐘信號,從而輸出不良時鐘信號。

圖 2. 無 VDD 時的錯誤時鐘輸出

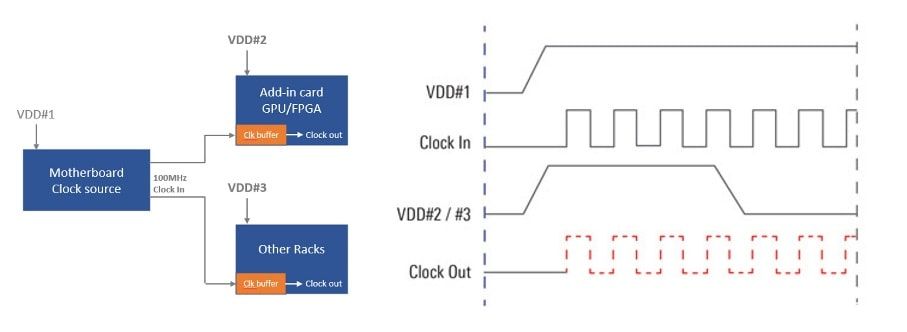

圖 3 描述了時鐘芯片在運行期間由于緊急中斷(如系統過熱、硬復位等)而斷電的情況。智能時鐘緩沖器可以在正確啟用輸出之前等待有效的 VDD。

圖 3. 系統關機時錯誤的時鐘輸出

案例 2:噪聲驅動時鐘緩沖器輸出振蕩

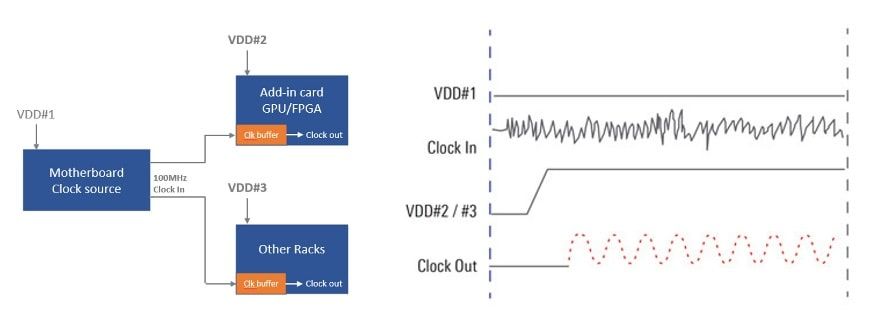

如果時鐘接收器側的附加卡或機架首先上電,則接收器側的附加卡或機架不一定會等待來自主主板的良好時鐘源。如果您的時鐘輸入沒有經過精心設計,您可能會觸發 ESD 事件,或者時鐘緩沖器輸出可能會開始振蕩以響應該刺激。智能時鐘緩沖器內部具有監控有效輸入時鐘源的機制。

圖 4. 噪聲輸入導致時鐘輸出振蕩

案例 3:泄漏問題

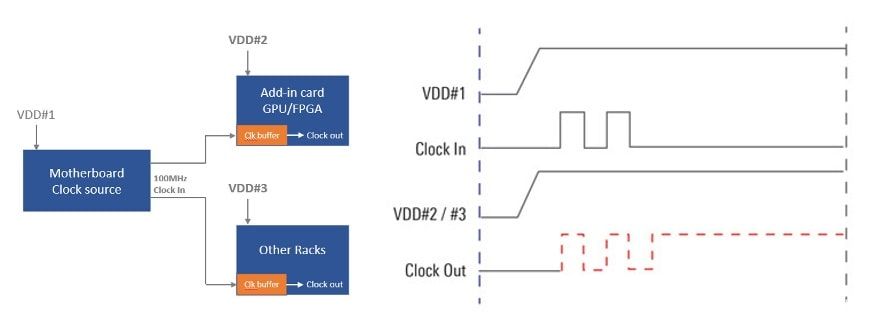

另一個常見問題是,當輸入參考時鐘消失時,時鐘芯片的輸出會停滯在高/低或低/高狀態。HCSL 拓撲具有自然關閉特性,當它們被禁用時使用低/低狀態。對于 LPHCSL 拓撲,如果沒有將輸入參考時鐘同步到 OE、電源正常或斷電引腳,這可能會導致問題。在這些情況下,系統應該斷電,但時鐘輸出可能仍以 850mV 驅動,如圖 5 所示。這種泄漏會給 CPU 增加不必要的熱量。當輸入上沒有信號時,智能時鐘緩沖器可以強制輸出為低/低狀態。

圖 5. 沒有時鐘輸入時,輸出仍以 850mV 驅動

幫助客戶解決諸如此類的現實世界場景幫助我們定義了這樣一個智能緩沖區。Renesas 的全新 PCIe Gen6 RC190024 / 20 / 16 / 13 / 08 / 04時鐘緩沖器系列和RC19216 / 08 / 04 / 02多路復用器系列具有克服所有這些情況的內置功能,包括斷電容限 (PDT )、靈活的啟動序列 (FSS) 和 (自動時鐘停放 (ACP)。所有這些對系統設計人員來說都是透明的,但可以在設計過程中輕松避免所有這些可能的陷阱。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17706瀏覽量

250002 -

接收器

+關注

關注

14文章

2468瀏覽量

71881 -

緩沖器

+關注

關注

6文章

1922瀏覽量

45473

發布評論請先 登錄

相關推薦

現代服務器系統上PCIe時序設計的解決方案

現代服務器系統上PCIe時序設計的解決方案

評論