瑞薩電子提供業內最廣泛、最深入的芯片時序產品組合。除了我們廣泛的緩沖器和時鐘合成器產品選擇外,我們還提供領先的系統時序解決方案,以解決幾乎任何應用中的時序挑戰。我們的產品組合在模擬和數字定時領域擁有超過 20 年久經考驗的專業知識,在先進的定時技術中具有最低的相位噪聲和最高的性能。

時序和時鐘 IC 廣泛用于網絡、射頻、物聯網、電信、圖像傳感器、醫療甚至音頻應用等應用。圍繞時序IC設計外部電路時,一定要注意電源設計。就像我們不應該用廉價的汽油填充蘭博基尼一樣,我們也不應該用嘈雜的電源為我們的低噪聲定時 IC 供電。

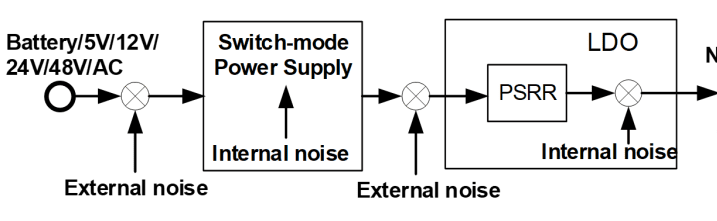

對于所有上述應用中使用的定時和時鐘 IC,電源通常是電池,或 5V 到 AC 之間的任何電壓總線。電源電壓通常通過開關模式電源降壓到適當的電平。在這里,一些外部輻射或傳導噪聲可能會耦合到系統中,并且電源可能會產生其自身的內部噪聲,從而導致其輸出電壓承載寬頻譜并生成不準確的時序/時鐘信號。在不添加強濾波器或低噪聲 LDO 的情況下,我們不應直接從此類噪聲電源饋送任何對噪聲敏感的時序或時鐘 IC,如圖 1 所示。由于尺寸原因,低噪聲 LDO 始終優于大型濾波器優點,準確的輸出電壓和更好的動態負載響應。

圖 1 為噪聲敏感電路供電的典型電源圖

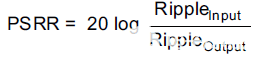

這種低噪聲 LDO 通常具有非常高的 PSRR(電源抑制比)來阻擋傳入噪聲,并且它還具有非常低的自生噪聲。PSRR 是特定頻率下 LDO 輸入電壓紋波與輸出電壓紋波的比率,通常以對數形式表示:

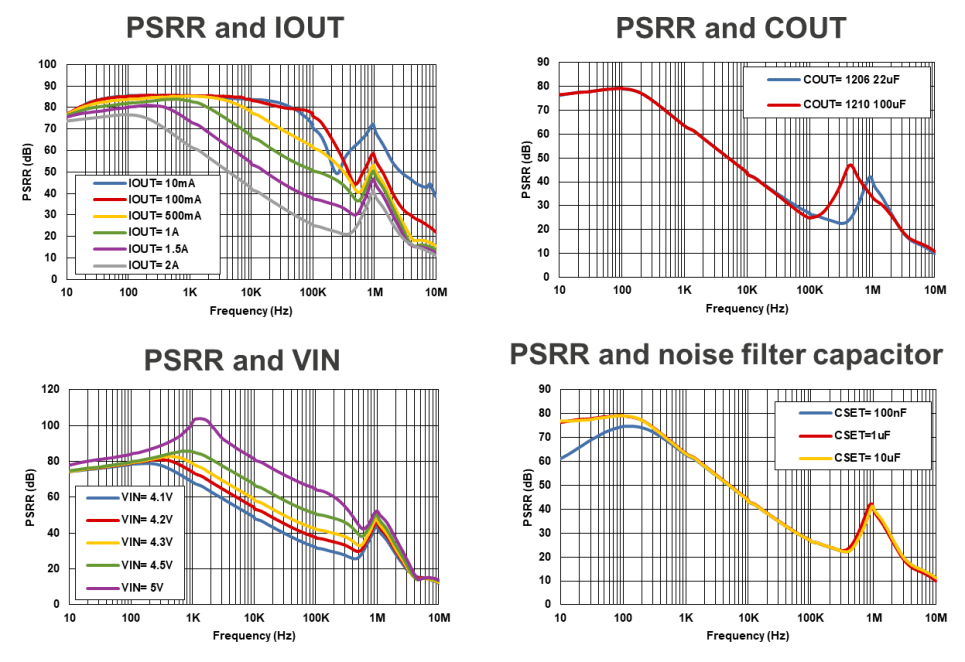

PSRR 通常隨負載電流、裕量電壓、輸出電容以及外部噪聲濾波電容和輸出電壓的不同而變化。高頻 PSRR 可以通過外部電容器輕松改善。然而,對于低頻濾波,電容可能會變得非常大且價格昂貴,因此選擇在低頻下具有非常高 PSRR 的 LDO 可能有助于減小電容尺寸。

圖 2 顯示了不同系統設置下的 PSRR 差異。根據圖 2B,PSRR 在高頻下隨著輸出電容器的增大而更高,并且 LDO 在低頻下已經具有非常高的 PSRR。根據圖 2D,如果需要在輕負載時更高的 PSRR,設計人員可以在帶隙引腳上添加一個小型低成本電容器,這不僅可以改善 PSRR,還可以改善內部噪聲。

圖 2 PSRR 與其他系統設置

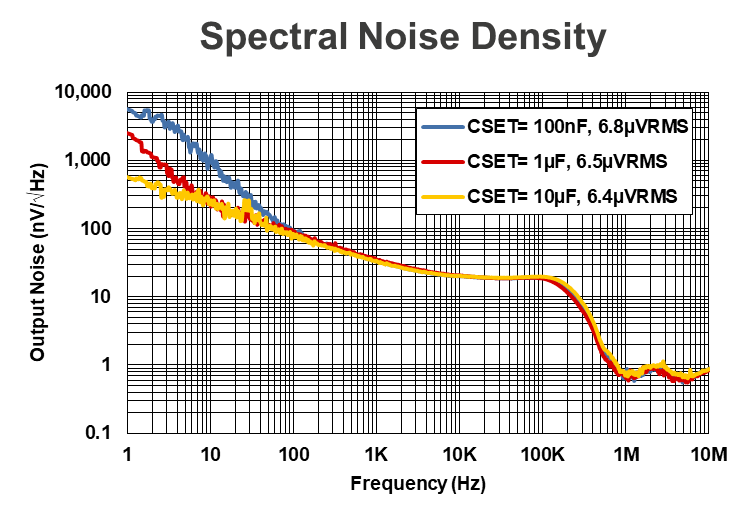

LDO 的另一個重要參數是內部噪聲,它以兩種方式表示。一個是頻譜噪聲密度,一條顯示噪聲與頻率的曲線。在對頻譜進行調節的射頻等應用中,必須將噪聲控制在“發射掩模”內才能通過認證測試。因此,用戶應該檢查感興趣的頻率周圍的頻譜噪聲密度曲線。典型的頻譜噪聲圖如圖 3 所示。

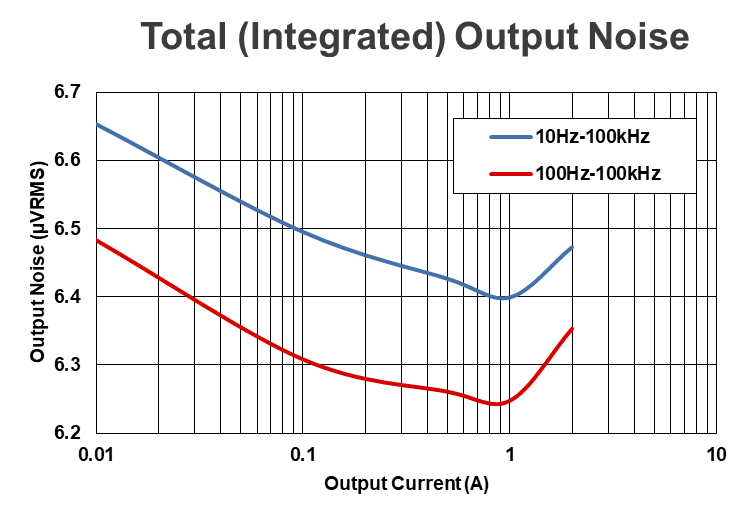

另一種是綜合輸出噪聲,通常也稱為輸出噪聲電壓。它是在一定頻率范圍內積分的頻譜噪聲密度。在 ADC 或 DAC 等應用中,從 DC 到系統帶寬的所有 LDO 噪聲都被集成并作為整體計算,以影響 ADC/DAC 精度。因此,總輸出噪聲對于此類應用很重要,典型的圖表如圖 4 所示。圖 3 和圖 4 取自瑞薩電子性能卓越的低噪聲 LDO。

圖 3

圖 4

瑞薩發布了兩款額定輸出為 5.5V 和 2A 的超低噪聲 LDO RAA214020和RAA214023,它們現在完全有資格為瑞薩時序和時鐘 IC 產品組合供電,并且包含在每個評估板的 BOM 中。下面顯示了一些具有匹配時鐘 IC 和 LDO 器件的示例。更多具有各種額定電流和性能的低噪聲 LDO 即將推出。

審核編輯:郭婷

-

ldo

+關注

關注

35文章

1945瀏覽量

153553 -

adc

+關注

關注

98文章

6513瀏覽量

545035 -

dac

+關注

關注

43文章

2299瀏覽量

191209

發布評論請先 登錄

相關推薦

LMK04208具有雙環PLL的低噪聲時鐘抖動消除器數據表

用于定時和時鐘IC的低噪聲電源

用于定時和時鐘IC的低噪聲電源

評論