雖然柵極間距(GP)和鰭片間距(FP)的微縮持續(xù)為FinFET平臺帶來更高的性能和更低的功耗,但在5nm及更先進節(jié)點上,兼顧寄生電容電阻的控制和實現(xiàn)更高的晶體管性能變得更具挑戰(zhàn)。

泛林集團在與比利時微電子研究中心(imec) 的合作中,使用了SEMulator3D?虛擬制造技術(shù)來探索端到端的解決方案,運用電路模擬更好地了解工藝變化的影響。我們首次開發(fā)了一種將SEMulator3D與BSIM緊湊型模型相耦合的方法,以評估工藝變化對電路性能的影響。

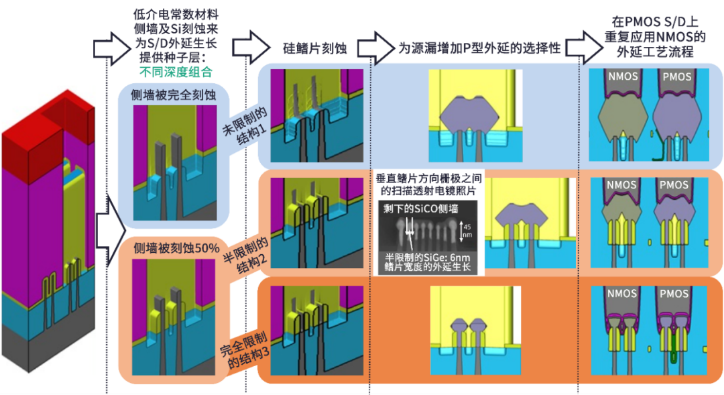

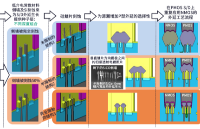

這項研究的目的是優(yōu)化先進節(jié)點FinFET設(shè)計的源漏尺寸和側(cè)墻厚度,以提高速度和降低功耗。為此,我們比較了具有三種不同外延 (epi) 生長形狀和源漏Si刻蝕深度的FinFET反向器結(jié)構(gòu)(圖1),研究低介電常數(shù)材料側(cè)墻厚度變化的影響,并確定了實現(xiàn)最佳性能的FinFET側(cè)墻厚度和源漏外延形狀組合。

圖1. 三種結(jié)構(gòu)的關(guān)鍵工藝步驟比較

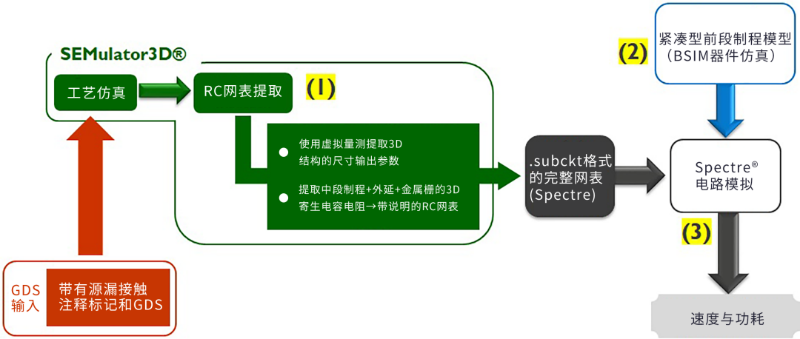

圖2對本研究方法進行了圖解。我們在建模中使用三種軟件:SEMulator3D、BSIM緊湊型建模和Spectre?電路模擬。首先將一個GDS輸入文件導(dǎo)入SEMulator3D,以便進行工藝模擬和RC網(wǎng)表提取。然后從SEMulator3D中提取各種數(shù)據(jù),包括幾何和寄生數(shù)據(jù),以創(chuàng)建帶說明的RC網(wǎng)表。該網(wǎng)表隨后與BSIM緊湊型前段制程 (FEOL) 器件模型相耦合,并被輸入到Spectre電路模擬模型。該Spectre模型隨后用于模擬正在評估的三種不同反向器的速度和功耗。

圖2. 本研究方法的流程圖

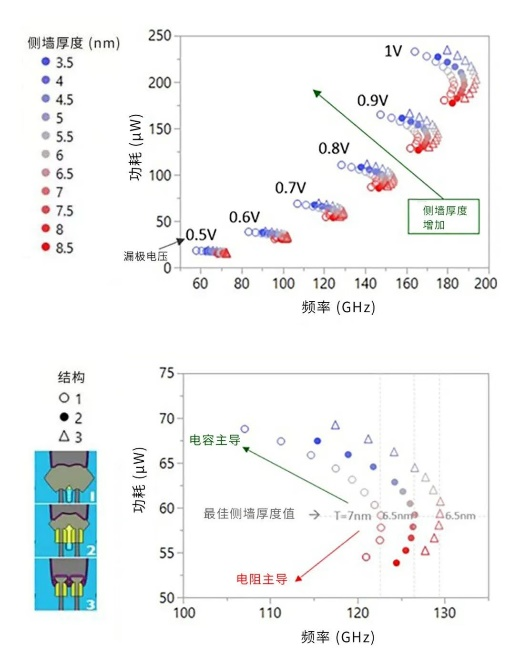

圖3顯示了三種結(jié)構(gòu)(在不同的漏極間電壓和側(cè)墻厚度下)的功耗與頻率的函數(shù)關(guān)系。我們注意到在不同漏極間電壓下,所有外延形狀幾何都呈類似的功耗-速度趨勢:側(cè)墻厚度增加導(dǎo)致功耗降低。每個外延尺寸都有一個可產(chǎn)生最大速度和最佳Reff×Ceff值(有效電阻值x有效電容值)的最佳側(cè)墻厚度。在各種側(cè)墻厚度下,有一個特定的外延形狀也提供了最高的整體性能。我們還研究了NMOS和PMOS結(jié)構(gòu)最佳側(cè)墻厚度下三種結(jié)構(gòu)的源漏接入電阻(S/D-R)和柵極到源漏(GT-S/D)的電容,以便更好地了解圖3中報告的結(jié)果。

圖3.三個反向器在漏極電壓為0.5V到1V時的功耗-速度比較(a)和放大后的漏極電壓等于0.7V時的功耗-速度比較(b)

這種建模方法為FinFET工藝變化對5nm以下器件和電路性能的影響提供了有價值的指導(dǎo)。我們通過RC網(wǎng)表提取將SEMulator3D與BSIM緊湊型建模和Spectre電路模擬相耦合,成功評估和比較了三種不同反向器幾何(使用不同側(cè)墻厚度)工藝流程變化的效果,以實現(xiàn)最佳晶體管性能,還探討了漏極間電壓和低介電常數(shù)材料側(cè)墻變化對速度和功耗性能的影響。

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28847瀏覽量

236628 -

電路仿真

+關(guān)注

關(guān)注

37文章

212瀏覽量

96272 -

FinFET

+關(guān)注

關(guān)注

12文章

257瀏覽量

91112

發(fā)布評論請先 登錄

三星使用EUV成功完成5nm FinFET工藝開發(fā)

FinFET是半導(dǎo)體工藝演進最佳選項?

NXP下一代汽車芯片選用臺積電5nm工藝

下一代高速芯片晶體管解制造問題解決了!

半導(dǎo)體制造企業(yè)未來分析

全球進入5nm時代

半導(dǎo)體工藝幾種工藝制程介紹

從7nm到5nm,半導(dǎo)體制程 精選資料分享

下一代晶體管露臉

臺積電5nm EUV工藝6月實現(xiàn)量產(chǎn),華為下一代旗艦處理器性能提升50%

早報:下一代iPhone芯片或?qū)⑹褂门_積電的5nm+工藝

評論