電子發燒友網報道(文/黃山明)近日,華為密集公布了多項技術專利,其中引人注意的是華為再次公布了兩項與芯片堆疊有關的專利。為何說再次,因為就在一個月前,華為同樣公開了“一種芯片堆疊封裝及終端設備”的專利。多項與芯片堆疊相關專利的公開,或許也揭露了華為未來在芯片技術上的一個發展方向。

華為芯片堆疊技術之路

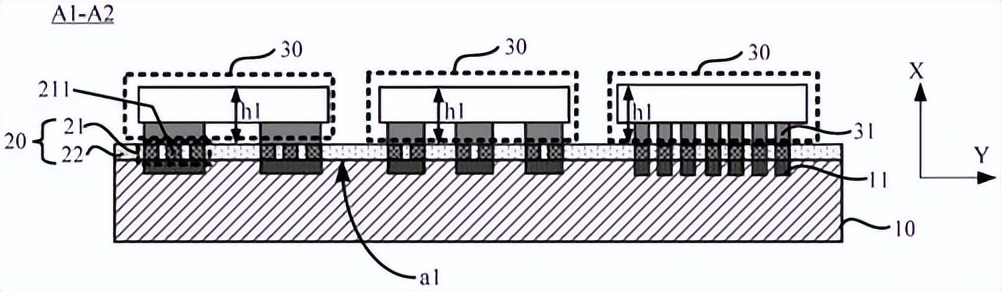

本次華為所公布的兩項芯片堆疊相關專利非常有意思,一項是“一種多芯片堆疊封裝及制作方法”(申請公布號:CN114287057A),用來解決多芯片的應力集中問題,能夠以進行更多層芯片的堆疊。

另一項為“芯片堆疊封裝結構及其封裝方法、電子設備”(申請公布號:CN114450786A),用于解決如何將多個副芯片堆疊單元可靠的鍵合在同一主芯片堆疊單元上的問題。

圖源:國家知識產權局

如果往前翻,可以發現早在2012年,華為便已經對芯片堆疊技術進行專利公開,該專利為“芯片堆疊封裝結構”(申請公布號:CN102693968A),主要設計芯片封裝技術領域,實現芯片的高密度堆疊,提高芯片堆疊封裝結構的散熱效率。

其后幾年,華為也在不斷對外公開其芯片堆疊的相關技術,足以證明長期以來華為都在這項技術上深耕研發。

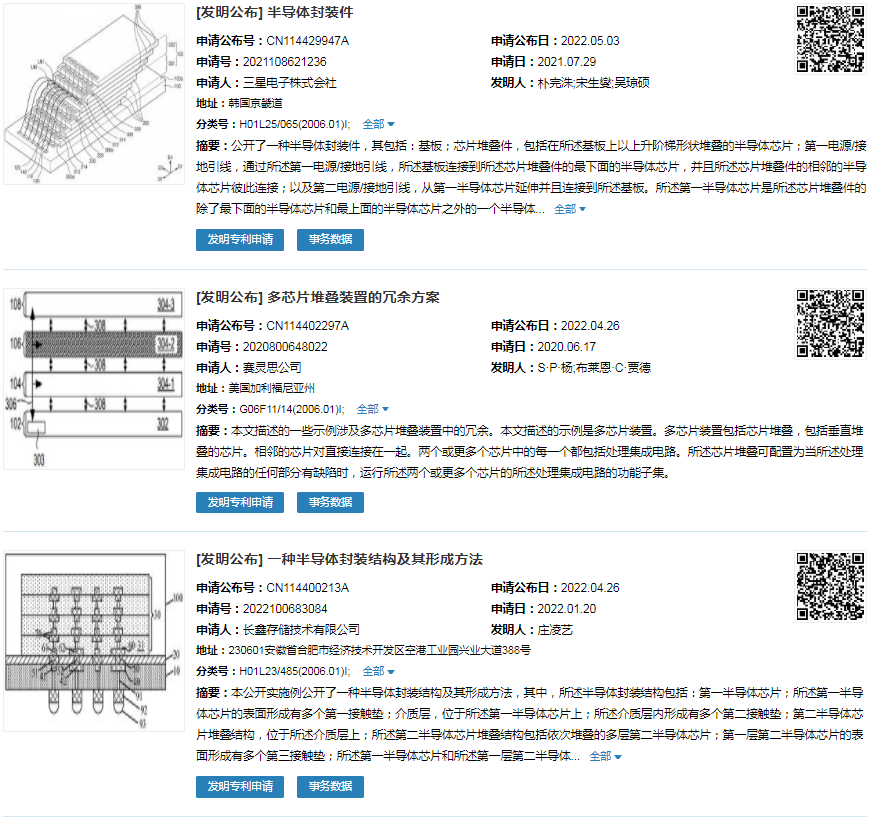

眾多廠商競逐芯片堆疊技術

從國家知識產權局所公布的專利來看,在芯片堆疊技術上并非華為的專場,眾多半導體大廠都在進行相關研發探索。如三星電子、賽靈思、博世、長鑫存儲、長江存儲等,而芯片堆疊技術為何會受到如此多廠商的青睞?

芯片堆疊,也就是封裝堆疊,或者一個更廣為人知的稱呼是3D封裝,這項技術的確是未來半導體發展的重要方向。

為何如此說?這就需要談到目前芯片工藝制程發展了。隨著芯片工藝制程的快速發展,其效益卻面臨著邊際遞減的問題,也就是說先進工藝制程可以讓芯片的性能更強、功耗更低,但卻無法使得芯片變得更便宜。

一個直觀的感受是,如今高端旗艦手機價格越來越昂貴了,而其中成本的大頭來自手機SoC,5nm的芯片要比7nm貴的多。也許不少消費者認為理所應當,但在過去可不是如此。

在芯片工藝制程發展之初,先進制程不僅能帶來更強勁的性能,讓芯片變得更小,同時也能讓晶體管成本下降。但從28nm以后,這個趨勢被打破了,這也是為何許多對性能與功耗要求不高的芯片仍然采用28nm制程,因為這樣具有最佳性價比。

那么不想增加成本用更先進的制程,又想擁有更強的性能,有沒有方法實現呢?當然有,那就是采用芯片堆疊技術。比如英國的AI芯片公司Graphcore發布了一款IPU產品Bow,采用臺積電7nm工藝生產,經過臺積電研發的3D WoW硅晶圓堆疊技術封裝后,性能提升了40%,功耗降低16%。

這是什么概念,要知道臺積電宣傳時的5nm工藝相比7nm在同等功耗下提升15%的性能,而在同等功耗下則可以提升30%的性能,對比來看,芯片堆疊技術反而表現更強。

臺積電的這項3D WoW硅晶圓堆疊技術,自2018年被提出,可以認為是類似于3D NAND閃存多層堆疊一樣,將兩層Die以鏡像方式垂直堆疊起來,以更先進的封裝技術提升芯片性能。

有了芯片堆疊技術,就能夠讓廠商以成熟工藝來獲得更高的性能,同時還能降低成本,畢竟成熟工藝良率更高,產能更大。

芯片堆疊技術能否幫助華為渡過燃眉之急

就在不久前舉辦的華為2021年業績發布會上,時任華為輪值董事長的郭平表示,未來華為可能會采用多核結構的芯片設計方案,以提升性能。同時,采用面積換性能,用堆疊換性能,使得不那么先進的工藝也能持續讓華為在未來的產品里面,能夠具有競爭力。

其中的面積換性能、堆疊換性能,指的大概就是芯片堆疊技術了。顯然對于這項技術,華為予以厚望。

同時在上個月召開的華為折疊屏及全場景新品發布會中,華為常務董事、終端BG CEO、智能汽車解決方案BU CEO余承東更是公開表示,當前華為手機的供應得到了極大地改善,去年華為手機供應很困難,而今年華為手機開始回來了,所以大家想買華為產品,華為手機都能買到,這是一個最大的好消息。

如果余承東沒有說“大話”,那么可以大膽的推測,華為在今年開始逐步解決芯片供給問題,而解決供應問題的一項方法便是采用芯片堆疊技術。

就如同Graphcore的AI芯片Bow一樣,能夠使7nm芯片通過堆疊技術之后性能要強于5nm。蘋果公司在今年的春季發布會上,便帶來了一款名為“M1 Ultra”的芯片,該蘋果采用特殊的封裝工藝,將兩塊M1 Max芯片串聯到了一起,從而實現了90%的性能提升。

顯然,華為也可以通過類似方法讓低制程芯片也煥發出新的生機,從而得到更高的性能表現,實現讓華為的產品具備一定市場競爭力的承諾。在一定程度上來說,使用芯片堆疊技術,的確能夠幫助華為解決無法獲得先進制程芯片下,產品競爭力缺失的問題。

寫在最后

需要注意的是,芯片堆疊技術并非萬能。誠然,在一代制程差距內,通過芯片堆疊技術可以讓低制程芯片在性能接近甚至超越高制程芯片,并且還能擁有良品率高、成本低等優勢,但這也是有極限的。

比如7nm通過芯片堆疊技術可以擁有5nm芯片的性能表現,而14nm芯片則需要6顆疊在一起才能在晶體管上比得上一顆5nm芯片。這樣一來,不僅是體積大增,同時由于線寬過小,會導致極間漏電流增大,邏輯錯誤增加,極間電容因為布線增多也會大幅增加,從而導致整體功耗增加數倍。而功耗的增加也導致發熱情況非常嚴重,華為的2012年的專利便已經意識到芯片堆疊的發熱問題。

即便這些問題都能夠解決,但更關鍵的問題是,即便通過芯片疊加,使晶體管數量能夠比肩高制程芯片,但算力利用率顯然不是簡單的1+1=2,大部分情況下最多只能得到1.3左右,即便是蘋果,其性能也是在1.8左右。這項技術想要真正走向成熟,還有不小的路程。

原文標題:華為公布芯片堆疊專利,能否解缺芯燃眉之急

文章出處:【微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

華為

+關注

關注

216文章

34411瀏覽量

251506 -

封裝

+關注

關注

126文章

7873瀏覽量

142894 -

芯片堆疊

+關注

關注

0文章

18瀏覽量

14576

原文標題:華為公布芯片堆疊專利,能否解缺芯燃眉之急

文章出處:【微信號:elecfans,微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

國星半導體兩項產品榮獲“2024年廣東省名優高新技術產品”

芯馳科技斬獲“創客北京2024”創新創業大賽兩項大獎

如何理解運放的共模輸入電壓范圍和差模輸入電壓范圍這兩項參數?

概倫電子同時入選兩項上證科創板主題指數

景旺電子兩項創新專利成功獲得美國專利授權

華陽與華為達成兩項重要合作

SGS助力中興通訊通過SBTi兩項審驗

華潤微電子兩項產品入選中央企業科技創新成果產品手冊

華為公布一項名為“鈉電池復合正極材料及其應用”的發明專利

華為公布創新光通信專利

華為公布“基于人體通信的電子設備、通信裝置和系統”專利

億鑄科技接連斬獲兩項大獎

華為公布兩項衛星通信網絡相關專利

華為公布兩項芯片堆疊相關專利

華為公布兩項芯片堆疊相關專利

評論