什么是阻抗

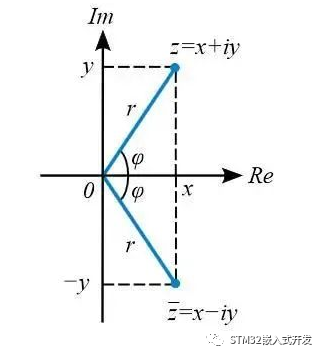

在電學(xué)中,常把對電路中電流所起的阻礙作用叫做阻抗。阻抗單位為歐姆,常用Z表示,是一個(gè)復(fù)數(shù):

Z= R+i( ωL–1/(ωC))

具體說來阻抗可分為兩個(gè)部分,電阻(實(shí)部)和電抗(虛部)。

其中電抗又包括容抗和感抗,由電容引起的電流阻礙稱為容抗,由電感引起的電流阻礙稱為感抗。

阻抗匹配的理想模型

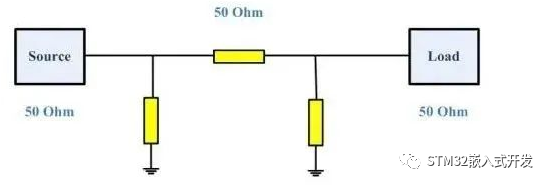

射頻工程師大都遇到過匹配阻抗的問題,通俗的講,阻抗匹配的目的是確保能實(shí)現(xiàn)信號或能量從“信號源”到“負(fù)載”的有效傳送。

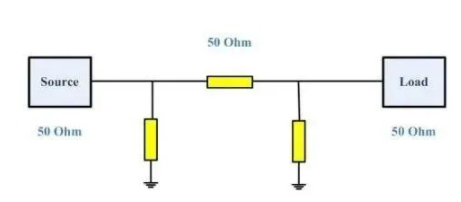

其最最理想模型當(dāng)然是希望Source端的輸出阻抗為50歐姆,傳輸線的阻抗為50歐姆,Load端的輸入阻抗也是50歐姆,一路50歐姆下去,這是最理想的。

然而實(shí)際情況是:源端阻抗不會是50ohm,負(fù)載端阻抗也不會是50ohm,這個(gè)時(shí)候就需要若干個(gè)阻抗匹配電路。

而匹配電路就是由電感和電容所構(gòu)成,這個(gè)時(shí)候我們就需要使用電容和電感來進(jìn)行阻抗匹配電路調(diào)試,以達(dá)到RF性能最優(yōu)。

阻抗匹配的方法

阻抗匹配的方法主要有兩個(gè),一是改變阻抗力,二是調(diào)整傳輸線。

改變阻抗力就是通過電容、電感與負(fù)載的串并聯(lián)調(diào)整負(fù)載阻抗值,以達(dá)到源和負(fù)載阻抗匹配。

調(diào)整傳輸線是加長源和負(fù)載間的距離,配合電容和電感把阻抗力調(diào)整為零。相關(guān)文章:認(rèn)識傳輸線的三個(gè)特性,特性阻抗、反射、阻抗匹配。

此時(shí)信號不會發(fā)生發(fā)射,能量都能被負(fù)載吸收。

高速PCB布線中,一般把數(shù)字信號的走線阻抗設(shè)計(jì)為50歐姆。一般規(guī)定同軸電纜基帶50歐姆,頻帶75歐姆,對絞線(差分)為85-100歐姆。

阻抗匹配應(yīng)用舉例——振鈴現(xiàn)象

曾經(jīng)做一個(gè)項(xiàng)目,在電信號測量時(shí),遇到過振鈴這種問題,。

由于任何傳輸線都不可避免地存在著引線電阻、引線電感和雜散電容,因此,一個(gè)標(biāo)準(zhǔn)的脈沖信號在經(jīng)過較長的傳輸線后,極易產(chǎn)生上沖和振鈴現(xiàn)象。大量的實(shí)驗(yàn)表明,引線電阻可使脈沖的平均振幅減小;而雜散電容和引線電感的存在,則是產(chǎn)生上沖和振鈴的根本原因。在脈沖前沿上升時(shí)間相同的條件下,引線電感越大,上沖及振鈴現(xiàn)象就越嚴(yán)重;雜散電容越大,則是波形的上升時(shí)間越長;而引線電阻的增加,將使脈沖振幅減小。

如果信號傳輸過程中感受到阻抗的變化,就會發(fā)生信號的反射。這個(gè)信號可能是驅(qū)動端發(fā)出的信號,也可能是遠(yuǎn)端反射回來的反射信號。相關(guān)文章:信號反射問題與相關(guān)電路設(shè)計(jì)技巧。根據(jù)反射系數(shù)的公式,當(dāng)信號感受到阻抗變小,就會發(fā)生負(fù)反射,反射的負(fù)電壓會使信號產(chǎn)生下沖。信號在驅(qū)動端和遠(yuǎn)端負(fù)載之間多次反射,其結(jié)果就是信號振鈴。大多數(shù)芯片的輸出阻抗都很低,如果輸出阻抗小于PCB走線的特性阻抗,那么在沒有源端端接的情況下,必然產(chǎn)生信號振鈴。

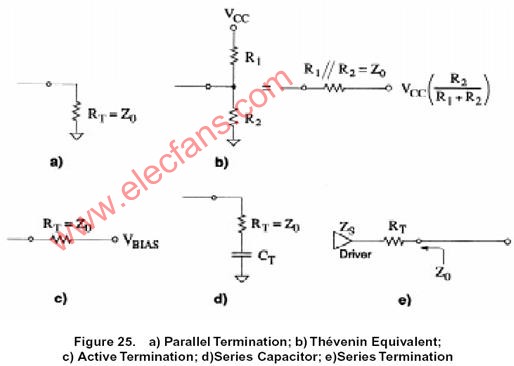

在實(shí)際電路中,采用下列幾種方法來來減小和抑制上沖及振鈴。

(1)串聯(lián)電阻。利用具有較大電阻的傳輸線或是人為地串入適當(dāng)?shù)淖枘犭娮瑁梢詼p小脈沖的振幅,從而達(dá)到減小上沖和振鈴程度的目的。但當(dāng)傳入電阻的數(shù)值過大時(shí),不僅脈沖幅度減小過多,而且使脈沖的前沿產(chǎn)生延遲。因此,串入的阻尼電阻值應(yīng)適當(dāng),并且應(yīng)選用無感電阻,電阻的連接位置應(yīng)靠近接收端。

(2)減小引線電感。設(shè)法減小線路及傳輸線的引線電感是最基本的方法,總的原則是:

盡量縮短引線長度

加粗導(dǎo)線和印制銅箔的寬度

減小信號的傳輸距離

采用引線電感小的元器件,尤其是傳輸前沿很陡的脈沖信號時(shí)更應(yīng)注意這些問題

(3)由于負(fù)載電路的等效電感和等效電容同樣可以影響發(fā)送端,使之脈沖波形產(chǎn)生上沖和振鈴,因此,應(yīng)盡量減小負(fù)載電路的等效電感和電容。尤其是負(fù)載電路的接地線過長時(shí),形成的地線電感和雜散電容相當(dāng)可觀,其影響不容忽視。

(4)邏輯數(shù)字電路中的信號線可增加上拉電阻和交流終端負(fù)載,如圖6所示。上拉電阻(可取)的接入,可將信號的邏輯高電平上拉到5V。交流終端負(fù)載電路的接入不影響支流驅(qū)動能力,也不會增加信號線的負(fù)載,而高頻振鈴現(xiàn)象卻可得到有效的抑制。

上述振鈴除了與電路條件有關(guān)外,還與脈沖前沿的上升時(shí)間密切相關(guān)。即使電路條件相同,當(dāng)脈沖前沿上升時(shí)間很短時(shí),上沖的峰值將大大增加。一般對于前沿上升時(shí)間在1以下的脈沖,均考慮產(chǎn)生上沖及振鈴的可能。因此,在脈沖信號頻率的選擇問題上,應(yīng)考慮在滿足系統(tǒng)速度要求的前提下,能選用較低頻率的信號絕不選用高頻信號;如無必要,也不應(yīng)過分要求脈沖的前沿非常陡峭。這對從根本上消除上沖和振鈴視聽有利的。

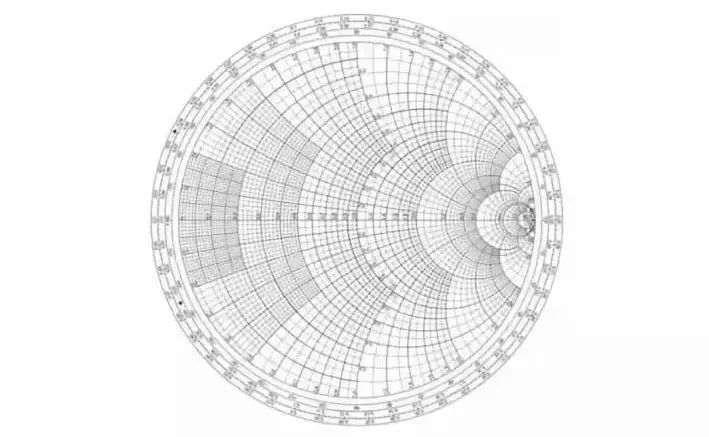

Smith圓圖在RF匹配電路調(diào)試中的應(yīng)用

Smith圓圖上可以反映出如下信息: 阻抗參數(shù)Z,導(dǎo)納參數(shù)Y,品質(zhì)因子Q,反射系數(shù),駐波系數(shù),噪聲系數(shù),增益,穩(wěn)定因子,功率,效率,頻率信息等抗等參數(shù)。

是不是一臉懵,我們還是來看阻抗圓圖吧:

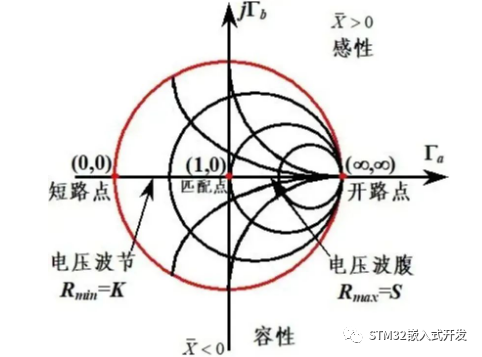

阻抗圓圖的構(gòu)圖原理是利用輸入阻抗與電壓反射系數(shù)之間的一一對應(yīng)關(guān)系,將歸一化輸入阻抗表示在反射系數(shù)極坐標(biāo)系中,其特點(diǎn)歸納如下:

上半圓阻抗為感抗,下半圓阻抗為容抗

實(shí)軸為純電阻,單位圓為純電抗

實(shí)軸的右半軸皆為電壓波腹點(diǎn)(除開路點(diǎn)),左半軸皆為電壓波節(jié)點(diǎn)(除短路點(diǎn))

匹配點(diǎn)(1,0),開路點(diǎn)(∞,∞)和短路點(diǎn)(0,0)

兩個(gè)特殊圓:最大的為純電抗圓,與虛軸相切的為匹配圓

兩個(gè)旋轉(zhuǎn)方向:逆時(shí)針轉(zhuǎn)為向負(fù)載移動,順時(shí)針轉(zhuǎn)為向波源移動

導(dǎo)納圓圖與阻抗圓圖互為中心對稱,同一張圓圖,即可以當(dāng)作阻抗圓圖來用,也可以當(dāng)作導(dǎo)納圓圖來用,但是在進(jìn)行每一次操作時(shí),若作為阻抗圓圖用則不能作為導(dǎo)納圓圖。

Smith圓圖中,能表示出一些很有意思的特征:

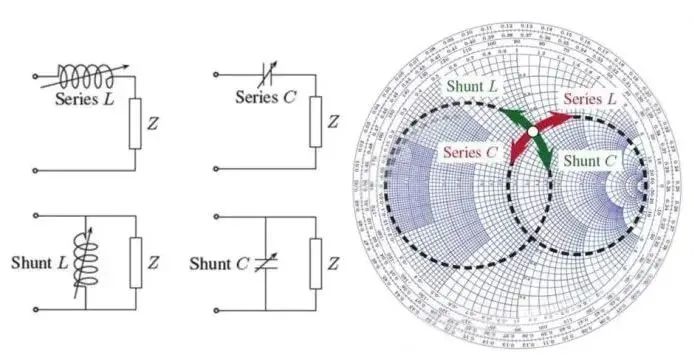

在負(fù)載之前串聯(lián)或并聯(lián)一個(gè)可變電感/電容,電路圖如下圖左側(cè)4個(gè)圖所示,將得到Smith圓圖上右側(cè)的幾條曲線。

對應(yīng)Smith阻抗圓及導(dǎo)納圓,其運(yùn)動軌跡如下:

使用Smith阻抗圓時(shí),串聯(lián)電感順時(shí)針轉(zhuǎn),串聯(lián)電容逆時(shí)針轉(zhuǎn)

使用Smith導(dǎo)納圓時(shí),并聯(lián)電感,逆時(shí)針轉(zhuǎn),并聯(lián)電容順時(shí)針轉(zhuǎn)

原文標(biāo)題:畫PCB板時(shí)阻抗設(shè)計(jì)的重要性

文章出處:【微信公眾號:STM32嵌入式開發(fā)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

審核編輯:湯梓紅

-

pcb

+關(guān)注

關(guān)注

4319文章

23081瀏覽量

397525 -

阻抗匹配

+關(guān)注

關(guān)注

14文章

351瀏覽量

30797 -

Smith

+關(guān)注

關(guān)注

0文章

20瀏覽量

9010

原文標(biāo)題:畫PCB板時(shí)阻抗設(shè)計(jì)的重要性

文章出處:【微信號:c-stm32,微信公眾號:STM32嵌入式開發(fā)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

淺析阻抗匹配及其應(yīng)用

PCB阻抗匹配的方法

怎樣理解阻抗匹配?

什么是阻抗匹配以及為什么要阻抗匹配

怎樣理解阻抗匹配_pcb阻抗匹配如何計(jì)算

阻抗匹配是什么意思_阻抗匹配原理詳解

淺談阻抗匹配的理想模型及方法

阻抗匹配的方法與應(yīng)用舉例

阻抗匹配的方法與應(yīng)用舉例

評論