第一 什么是流水線

流水線設計就是將組合邏輯系統地分割,并在各個部分(分級)之間插入寄存器,并暫存中間數據的方法。目的是將一個大操作分解成若干的小操作,每一步小操作的時間較小,所以能提高頻率,各小操作能并行執行,所以能提高數據吞吐率(提高處理速度)。

第二 什么時候用流水線設計

使用流水線一般是時序比較緊張,對電路工作頻率較高的時候。典型情況如下:

1)功能模塊之間的流水線,用乒乓 buffer 來交互數據。代價是增加了 memory 的數量,但是和獲得的巨大性能提升相比,可以忽略不計。

2) I/O 瓶頸,比如某個運算需要輸入 8 個數據,而 memroy 只能同時提供 2 個數據,如果通過適當劃分運算步驟,使用流水線反而會減少面積。

3)片內 sram 的讀操作,因為 sram 的讀操作本身就是兩極流水線,除非下一步操作依賴讀結果,否則使用流水線是自然而然的事情。

4)組合邏輯太長,比如(a+b)*c,那么在加法和乘法之間插入寄存器是比較穩妥的做法。

第三 使用流水線的優缺點

1)優點:流水線縮短了在一個時鐘周期內給的那個信號必須通過的通路長度,增加了數據吞吐量,從而可以提高時鐘頻率,但也導致了數據的延時。舉例如下:例如:一個 2 級組合邏輯,假定每級延遲相同為 Tpd,

1.無流水線的總延遲就是 2Tpd,可以在一個時鐘周期完成,但是時鐘周期受限制在 2Tpd;

2.流水線:

每一級加入寄存器(延遲為 Tco)后,單級的延遲為 Tpd+Tco,每級消耗一個時鐘周期,流水線需要 2 個時鐘周期來獲得第一個計算結果,稱 為首次延遲,它要 2*( Tpd+Tco),但是執行重復操作時,只要一個時鐘周期來獲得最后的計算結果,稱為吞吐延遲( Tpd+Tco)。可見只要 Tco 小于 Tpd,流水線就可以提高速度。 特別需要說明的是,流水線并不減小單次操作的時間,減小的是整個數據的操作時間,請大家認真體會。

2) 缺點:功耗增加,面積增加,硬件復雜度增加,特別對于復雜邏輯如 cpu 的流水線而言,流水越深,發生需要 hold 流水線或 reset 流水線的情況時,時間損失越大。 所以使用流水線并非有利無害,大家需權衡考慮。

第四 一個 8bit 流水線加法器的小例子

非流水線:

module add8(

a,

b,

c);

input [7:0] a;

input [7:0] b;

output [8:0] c;

assign c[8:0] = {1'd0, a} + {1'd0, b};

endmodule

采用兩級流水線:第一級低 4bit,第二級高 4bit,所以第一個輸出需要 2 個時鐘周期有效,后面的數據都是 1 個周期

之后有效。

module adder8_2(

clk,

cin,

cina,

cinb,

sum,

cout);

input clk;

input cin;

input [7:0] cina;

input [7:0] cinb;

output [7:0] sum;

output cout;

reg cout;

reg cout1; //插入的寄存器

reg [3 :0 ] sum1 ; //插入的寄存器

reg [7 :0 ] sum;

reg [3:0] cina_reg;

reg [3:0] cinb_reg;//插入的寄存器

always @(posedge clk) //第一級流水

begin

{cout1 , sum1} <= cina[3:0] + cinb [3:0] + cin ;

end

always @(posedge clk)

begin

cina_reg <= cina[7:4];

cinb_reg <= cinb[7:4];

end

always @(posedge clk) //第二級流水

begin

{cout ,sum[7:0]} <= {{1'b0,cina_reg[3:0]} + {1'b0,cinb_reg[3:0]} + cout1 ,sum1[3:0]} ;

end

endmodule

這里講到的流水線,主要是一種硬件設計的算法,如第一條中表述的流水線設計就是將組合邏輯系統地分割,并在各個部分(分級)之間插入寄存器,并暫存中間數據的方法。

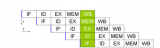

針對處理器中的流水線結構。比如,比如 5—6 個不同功能的電路單元組成一條指令處理流水線,然后將一條指令分成 5—6 步后再由這些電路單元分別執行,這樣就能實現在一個 CPU 時鐘周期完成一條指令,因此提高 CPU 的運算速度。 一般的 CPU 中,每條整數流水線都分為四級流水, 即指令預取、 譯碼、 執行、 寫回結果,openrisc采用的是 5 級整數流水線。

當然它們的核心思想都是利用并行執行提高效率。

總結一下,流水線就是插入寄存器,以面積換取速度。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603005 -

流水線

+關注

關注

0文章

120瀏覽量

25726

原文標題:FPGA學習-流水線設計Pipeline Design

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

周期精確的流水線仿真模型

一文讀懂處理器流水線

FPGA之為什么要進行流水線的設計

滾筒輸流水線故障排除方法

如何選擇合適的LED生產流水線輸送方式

嵌入式_流水線

CPU流水線的問題

了解流水線型ADC

一文詳細了解流水線設計

一文詳細了解流水線設計

評論