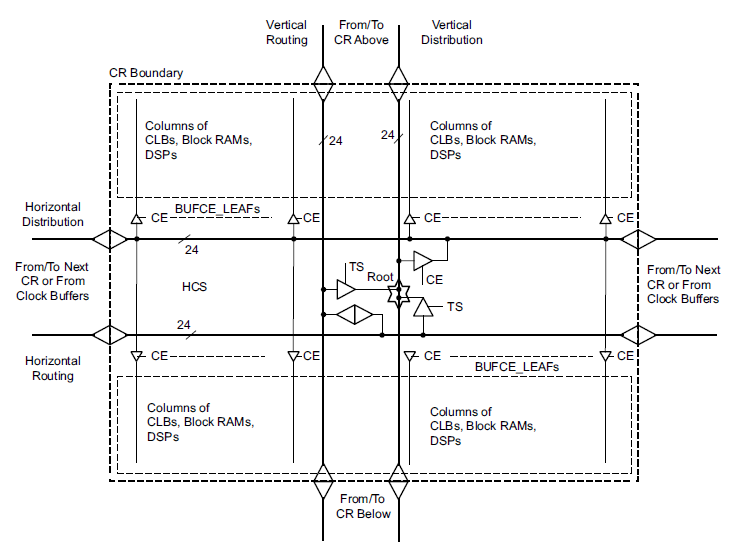

UltraScale和UltraScale+進一步增強了Clock root的概念,從芯片架構和Vivado支持方面都體現(xiàn)了這一點。為了理解這一概念,我們先看看UltraScale/UltraScale+的時鐘資源。

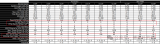

每個時鐘區(qū)域有24個水平分發(fā)軌道(HorizontalDistribution)和水平布線軌道(HorizontalRouting),同時,垂直方向也有24個分發(fā)軌道(VerticalDistribution)和24個布線軌道(Vertical Routing),如下圖所示。

審核編輯 :李倩

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

時鐘

+關注

關注

11文章

1758瀏覽量

132182 -

UltraScale

+關注

關注

0文章

118瀏覽量

31564

原文標題:設計中的Clock root可以修改嗎?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

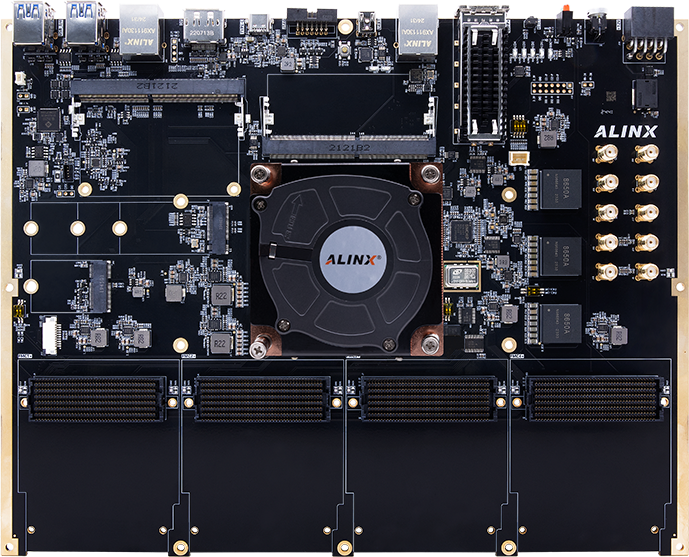

AI 應用場景全覆蓋!解碼超高端 VU+ FPGA 開發(fā)平臺 AXVU13F

「AXVU13F」 Virtex UltraScale+ XCVU13P + Jetson Orin NX? 繼發(fā)布 AMD Virtex UltraScale+ FPGA PCIE3.0 開發(fā)平臺

Zynq UltraScale+ MPSoC數(shù)據(jù)手冊

電子發(fā)燒友網(wǎng)站提供《Zynq UltraScale+ MPSoC數(shù)據(jù)手冊.pdf》資料免費下載

發(fā)表于 12-30 14:37

?2次下載

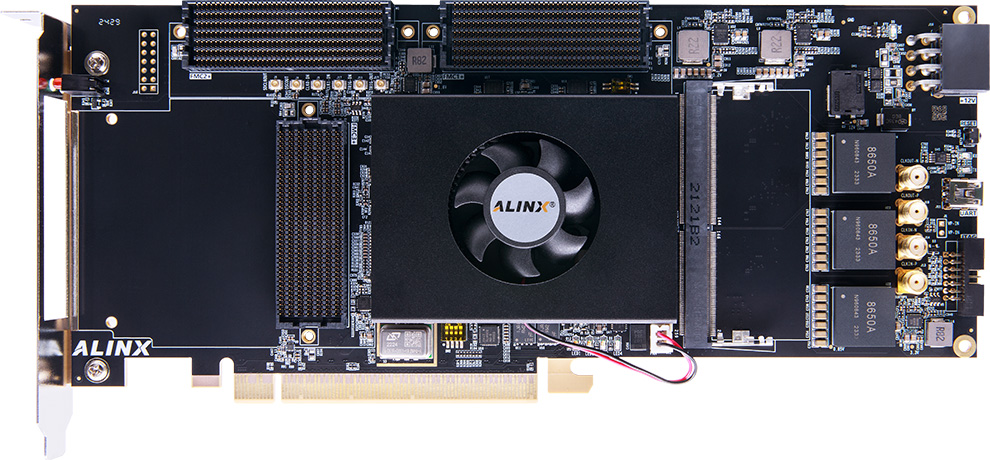

ALINX 發(fā)布 AXVU13P:AMD Virtex UltraScale+ 高端 FPGA PCle 3.0 綜合開發(fā)平臺

ALINX 正式發(fā)布 AMD Virtex UltraScale+ 系列 FPGA PCIe 3.0 綜合開發(fā)平臺?AXVU13P! 這款搭載 AMD 16nm 工藝 XCVU13P 芯片的高性能

針對ZYNQ+ULTRASCALE的FPGA供電的一些疑問求解答

針對ZYNQ+ULTRASCALE的FPGA供電一些疑問(比如XCZU15EG-FFVB1156I型號):

1:這個芯片的輸出配置可以通過I2C接口進行配置,有個疑問,就是板子在SMT貼片回來以后

發(fā)表于 12-02 08:02

時序約束一主時鐘與生成時鐘

的輸出,對于Ultrascale和Ultrascale+系列的器件,定時器會自動地接入到GT的輸出。 1.2 約束設置格式 主時鐘約束使用命令create_clock進行創(chuàng)建,進入Timing

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件可快速啟動汽車、工業(yè)、視頻和通信應用設計。AMD/Xilinx MPSoC ZCU102 評估套件采用

為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電

電子發(fā)燒友網(wǎng)站提供《為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電.pdf》資料免費下載

發(fā)表于 09-25 10:54

?0次下載

使用TPS65086x PMIC為Xilinx Zynq UltraScale MPSoC供電

電子發(fā)燒友網(wǎng)站提供《使用TPS65086x PMIC為Xilinx Zynq UltraScale MPSoC供電.pdf》資料免費下載

發(fā)表于 09-21 11:11

?0次下載

一個更適合工程師和研究僧的FPGA提升課程

設計;

● UltraFast 設計方法;

● 使用UltraScale和UltraScale+架構進行設計;

● FPGA 功耗最優(yōu)化;

● 使用 Vivado Design Suite 4

發(fā)表于 06-05 10:09

基于FPGA設計的BRAM內(nèi)部結構

再看末級觸發(fā)器對BRAM時序性能的影響,下圖依次展示了7系列FPGA、UltraScale+和Versal芯片在未使用和使用末級觸發(fā)器兩種情形下時鐘到輸出的延遲。

發(fā)表于 04-25 10:42

?518次閱讀

中高端FPGA如何選擇

為了使數(shù)據(jù)傳輸更加高效,Achronix FPGA上的Memory資源也是非常給力,不管是片上Ram還是DDR接口,都比Virtex Ultrascale+有很大優(yōu)勢。

在Speedster7t

發(fā)表于 04-24 15:09

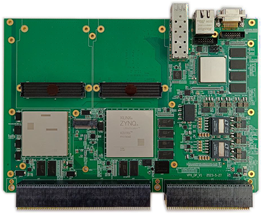

KU115+ZU19EG+DSP6678的雙FMC 6U VPX處理板

和 1 片 Zynq UltraScale+ MPSoC 家族的 XCZU19EG-2FFVC1760I 以及 1 片 TI 公司的 DSP 芯片 TMS320C6678ACYPA。

Achronix的FPGA有哪方面的優(yōu)勢?

Achronix的Speedster7t支持PCIe Gen5和112G Serdes,而AMD的高端系列Virtex Ultrascale+也僅僅支持到PCIe Gen4,也只在最高端的FPGA中支持到58Gb的GTM,大多數(shù)Virtex Ultrascale+僅僅支持

發(fā)表于 03-18 10:55

?458次閱讀

AMD推出全新Spartan UltraScale+ FPGA系列

AMD 已經(jīng)擁有 Zynq UltraScale+ 和 Artix UltraScale+ 系列,而 Spartan UltraScale+ FPGA 系列的推出使其不斷現(xiàn)代化。

發(fā)表于 03-18 10:40

?516次閱讀

UltraScale系列與7系列FPGA的差異

已從該架構中移除BUFMRs、BUFRs、BUFIOs及其相關的路由資源,并被新的時鐘緩沖器、時鐘路由和全新的I/O時鐘架構所取代。

UltraScale/UltraScale+的時鐘資源

UltraScale/UltraScale+的時鐘資源

評論