本系列文章已突出介紹了連續時間Σ-Δ(CTSD)模數轉換器(ADC)調制器環路的架構特性,這種架構能夠簡化ADC模擬輸入端的信號鏈設計。現在討論將ADC數據與外部數字主機接口以對此數據執行應用相關處理的簡單但創新的方法。對任何應用而言,數字數據輸出采樣速率都是ADC信號鏈的一個關鍵參數。但是,不同應用有不同的采樣速率要求。本文章介紹一種新型片內采樣速率轉換技術,其用在核心ADC的輸出上,允許信號鏈設計人員以應用所需的采樣速率處理ADC數字輸出數據。

ADC的作用是對模擬輸入信號進行采樣,并將其轉換為等效的數字格式。應用對數字數據做進一步處理所需的采樣速率不一定與ADC對模擬信號進行采樣的速率相同。每個應用都有獨特的數字輸出采樣速率要求。采樣速率轉換器將ADC數據的輸入采樣速率映射為所需的輸出采樣速率。本文首先概述各種應用的采樣速率要求,證明ADC需要支持廣泛的輸出采樣速率。然后,本文快速回顧已知ADC架構中的傳統采樣速率轉換技術及其缺點。接下來,本文介紹新穎的異步采樣速率轉換(ASRC),它能與任何ADC架構配對,以獲得任何所需的輸出采樣速率,并用外部數字主機簡化數字接口設計。

ASRC與CTSD ADC搭配可謂兩全其美,不僅能簡化ADC模擬輸入端的信號鏈設計,也能簡化數字輸出端的信號鏈設計。

采樣速率要求

驅動數字數據采樣速率選擇ADC的主要性能參數之一是ADC的預期精度。數字數據中的樣本數量越多,對模擬輸入的表示就越準確。但不利的一面是需要處理大量數據,外部數字主機接口設計的復雜度和功耗會提高。因此,每個應用根據所需的精度、功耗預算和設計復雜度以及計劃的算法處理,決定了數字數據的采樣速率。所需的大多數一般采樣速率可以分類如下:

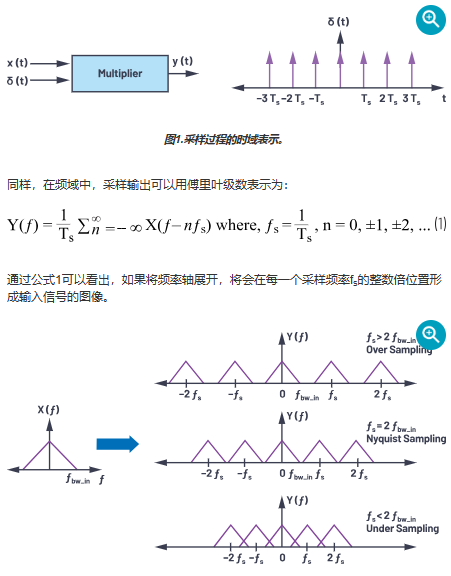

奈奎斯特采樣速率

眾所周知的奈奎斯特采樣1準則指出:為了提供模擬輸入的忠實數字表示,采樣速率至少應為輸入帶寬的兩倍。因此,奈奎斯特采樣速率應用的數字采樣速率為目標輸入帶寬的兩倍。這種采樣速率的一個眾所周知的例子是CD上的數字音頻數據存儲,其速率為44.1 kSPS,而目標輸入音頻帶寬最高為20 kHz,即人類聽力的頻率上限。

過采樣速率

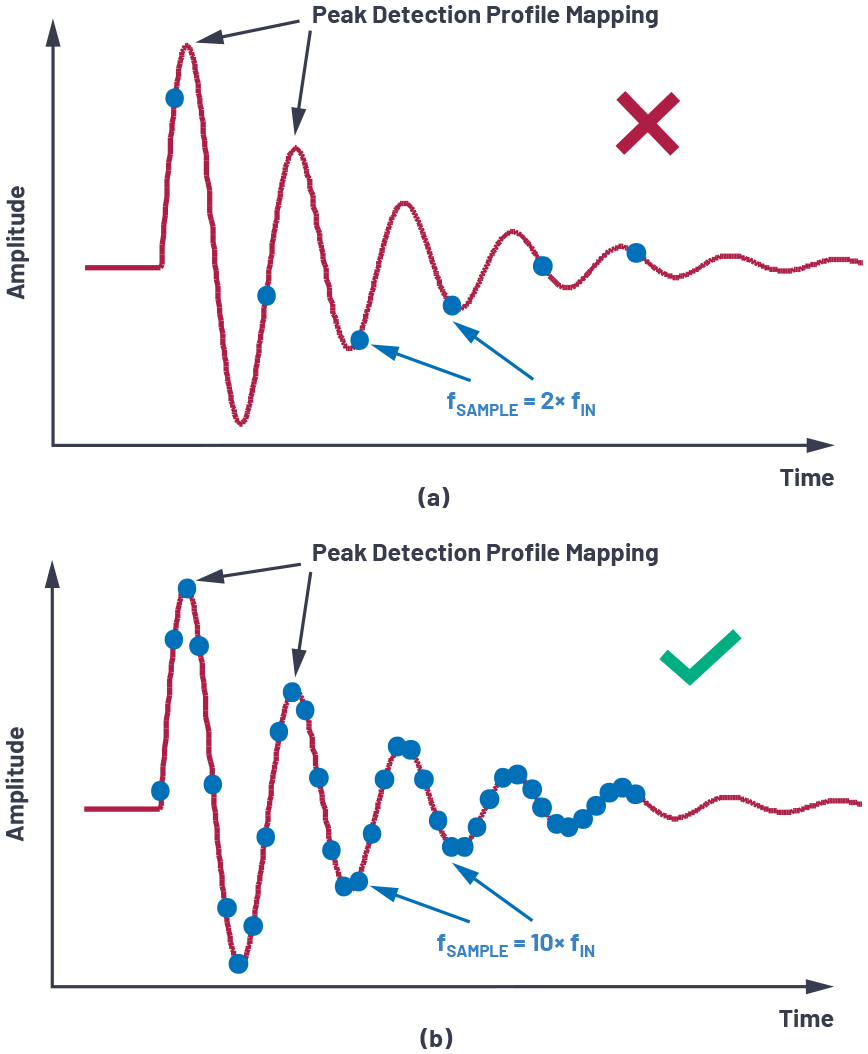

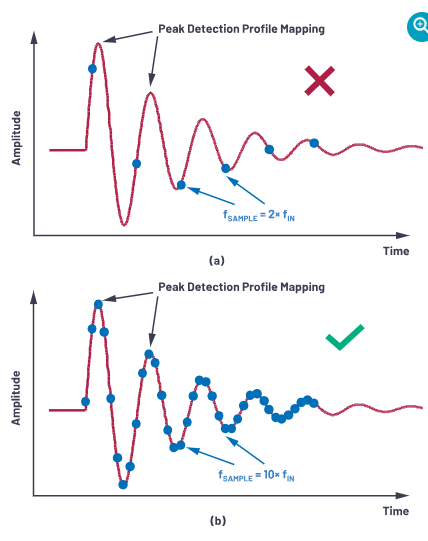

有少數一些應用,例如頻率諧波分析或時域分析,其需要的采樣速率比輸入帶寬高出好多倍。過采樣速率的一個例子是沖擊檢測環境中瞬態信號的時域分析,如圖1所示。如果這種信號的采樣速率是奈奎斯特采樣速率,我們將無法了解信號的全貌。擁有更多的采樣點可以更忠實地重建和分析信號。

圖1.瞬態信號的時域分析:(a) 奈奎斯特采樣速率,(b) 過采樣速率

可變采樣速率

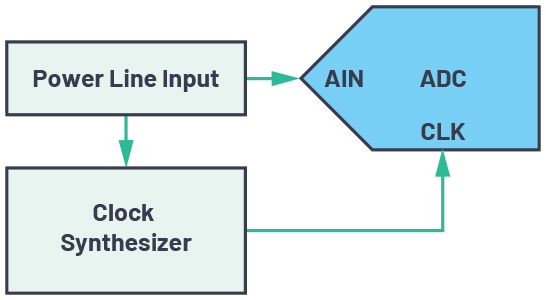

某些應用(例如相干采樣)要求以良好的分辨率根據模擬輸入頻率調整輸出采樣速率。電力線監測就是這種應用的一個例子,需要相干采樣來滿足IEC 61000-4-30規定的A類電能質量計量要求。這些標準的精度要求決定了采樣速率需要跟蹤輸入線路頻率漂移。在這些應用中,電力線上的時鐘頻率合成器電路產生ADC的輸出數字數據采樣時鐘,如圖2所示。

圖2.可變采樣速率:電力線質量監測

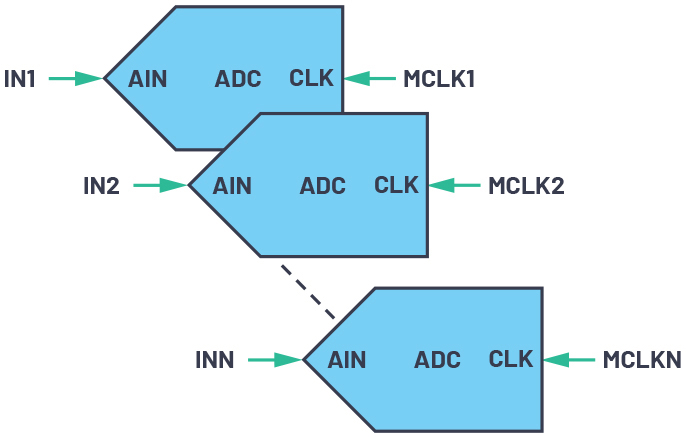

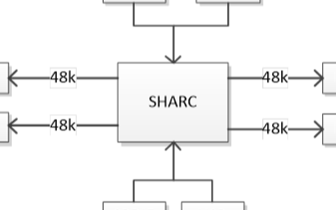

多采樣速率

在檢測和分析寬范圍且不同類型的模擬輸入的多通道應用中,例如示波器或數據采集應用,每個通道的采樣速率可能不同。在這種情況下,平臺中使用的ADC應該能夠靈活地支持多采樣速率。

圖3.多采樣速率應用

因此,數字數據采樣速率要求因應用而異,并不存在一種萬能的采樣速率。所以,面向廣闊市場的ADC需要支持寬范圍的可編程數字數據采樣速率。

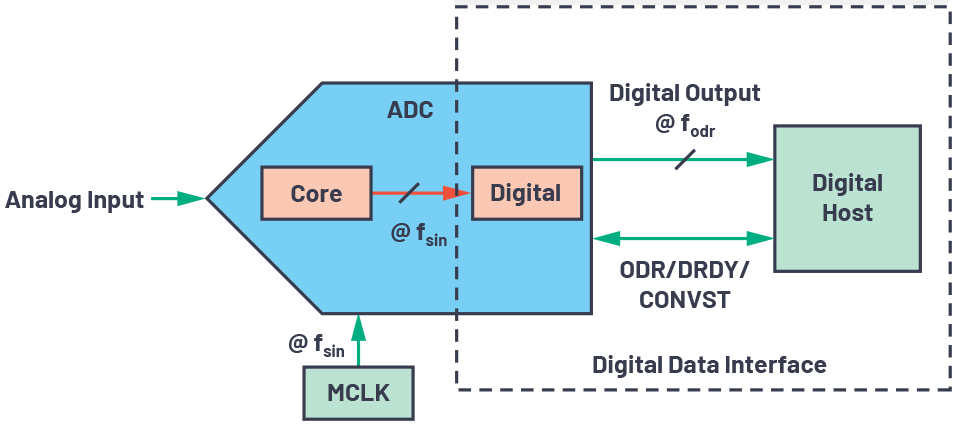

圖4展示了一個具有外部數字主機的廣義ADC數字數據接口。需要注意的是,本文中討論的數字數據接口不包括器件配置控制接口,如SPI或I2C。

圖4.廣義ADC數字數據接口

核心ADC利用速率為fsin的采樣時鐘對模擬輸入采樣,如圖4所示。在大多數數據手冊中,輸入采樣時鐘本身一般表示為MCLK。最終數字輸出數據的采樣速率為fodr。通常,這些引腳在數據手冊中標記為ODR、DRDY或CONVST時鐘。本文使用ODR時鐘這個總稱來表示數字輸出數據時鐘。

ADC核心的采樣速率fsin取決于ADC架構。數字輸出數據速率fodr取決于外部數字主機的數據接口要求。在大多數ADC信號鏈應用中,fsin和fodr可以具有不同的值并且不相關。因此需要進行采樣速率轉換,將ADC核心的fsin數據映射為fodr的數字輸出數據。以下部分將討論眾所周知的ADC架構(如奈奎斯特ADC和過采樣ADC)中使用的傳統采樣速率轉換技術。此外,我們將深入了解其他相關的數字數據接口要求。

奈奎斯特速率ADC中的采樣速率轉換

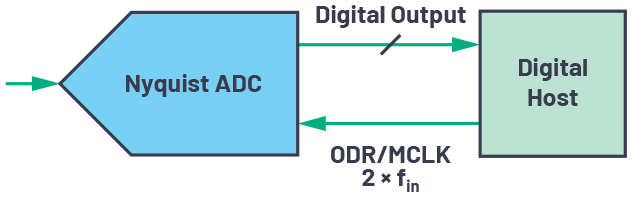

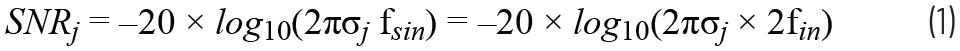

在奈奎斯特速率轉換器中,ADC核心的采樣頻率是模擬輸入帶寬fin的兩倍。此類別下最常見的例子是奈奎斯特速率SAR ADC,其輸入和輸出采樣速率相同。因此,數字輸出數據速率時鐘ODR可以復用為ADC核心采樣時鐘MCLK。在SAR ADC數據手冊中,數字輸出數據時鐘表示為CONVST或DRDY。但如前所述,本文將所有這些時鐘統稱為ODR時鐘。ODR和MCLK組合可簡化數字數據接口,如圖5所示,僅需一條時鐘布線。由于時鐘由外部時鐘源或外部數字主機提供并控制,因此ADC由外部提供時鐘。這意味著ADC是在外部托管模式下運行。

圖5.托管模式中奈奎斯特速率轉換器的簡化數字數據接口

根據應用要求和模擬輸入帶寬,很容易調整采樣速率fodr。通過調整fodr,我們還能調整ADC核心的采樣時鐘速率fsin。另一個優點是,當調整fodr時,整個ADC的功耗也會線性地調整。這種簡化的數字數據接口還有許多其他延伸的好處,其中一個是多通道應用中易于同步。

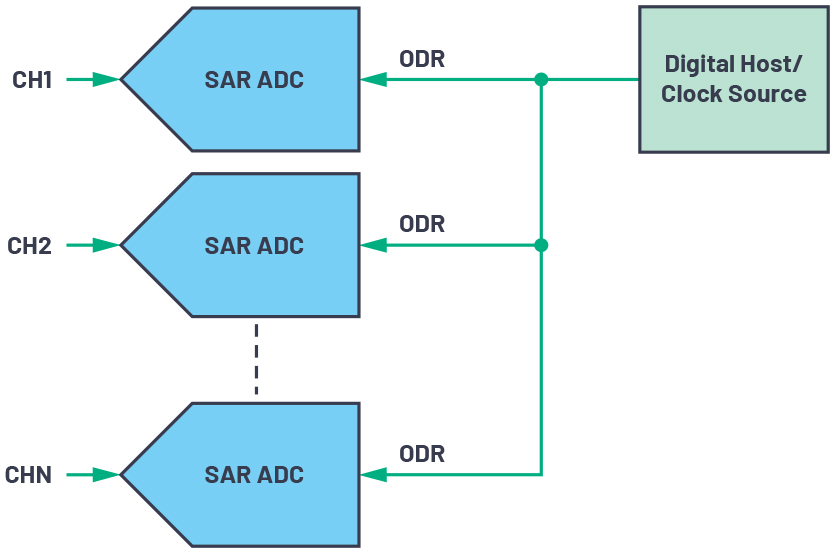

易于同步

在單通道ADC應用中,提供給ADC的本地時鐘會固有地將數字數據與給定時鐘同步。在多通道ADC應用中,挑戰是要保證多個模擬輸入的同步采樣,以及數字數據與ODR時鐘邊沿同步以進行進一步數字處理。多通道同步應用有很多廣為人知的例子,例如音頻應用,其中左右通道具有特定的同步要求。另一個典型例子是監測電網中的各種電力線。在每條電力線內部,電壓、電流和功率輸入測量需要同步。利用奈奎斯特速率ADC,如圖6所示,通過共享ODR時鐘并對其路由進行良好規劃,可以輕松實現多通道同步。規劃良好的路由可以確保ODR時鐘以相同延遲傳播到每個ADC,并提供盡可能好的通道同步。

圖6.簡化奈奎斯特速率采樣速率轉換器中的同步

簡化的數字數據接口是奈奎斯特速率轉換器的一個重要優勢。下面討論其無法勝任的一些數字數據接口挑戰。

奈奎斯特速率控制的局限性

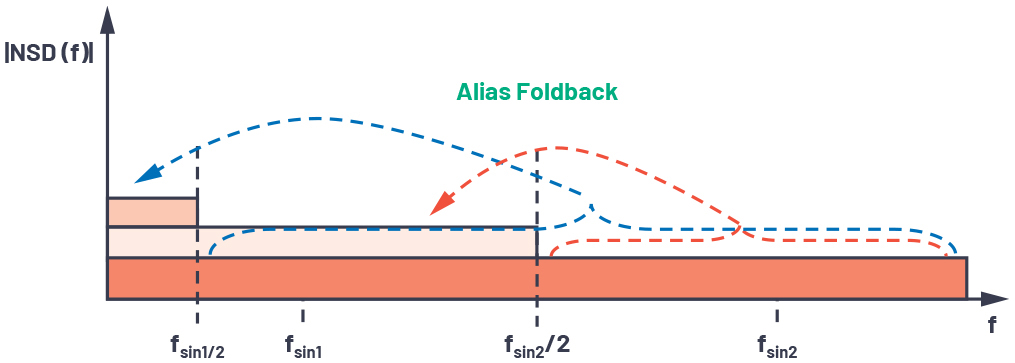

噪聲調整

在基于應用的模擬輸入帶寬的奈奎斯特速率轉換器中,可以輕松調整數字數據時鐘。時鐘調整可帶來功耗上的優勢,但由于所謂混疊折返現象,ADC噪聲會增加。奈奎斯特采樣準則的延伸是,任何超出奈奎斯特頻率的信息都會折返或混疊回到目標頻帶。ADC的模擬輸入會有大量來自信號源和輸入模擬電路的干擾信息或噪聲,其延伸到非常高的頻率。ADC采樣導致任何超過fsin/2的輸入噪聲折返,使得目標輸入帶寬中的噪聲增加。如圖7所示,隨著采樣速率降低,會有更多這樣的外部噪聲折返,從而增加ADC輸出中的噪聲。

圖7.輸入噪聲折返與采樣頻率的關系

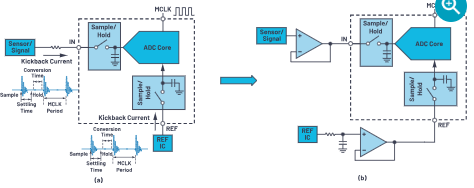

時鐘時序約束

對于SAR ADC,模擬輸入采樣時鐘需要兩個階段,如圖9a所示。一個是采樣階段,其中ADC的輸入采樣電容對模擬輸入充電;另一個是轉換階段,其中該采樣數據被數字化。為了獲得盡可能好的ADC性能,ADC的采樣電路一般存在最短采樣時間要求。因此,生成此時鐘的外部數字主機或時鐘源需要遵守這些時序約束。

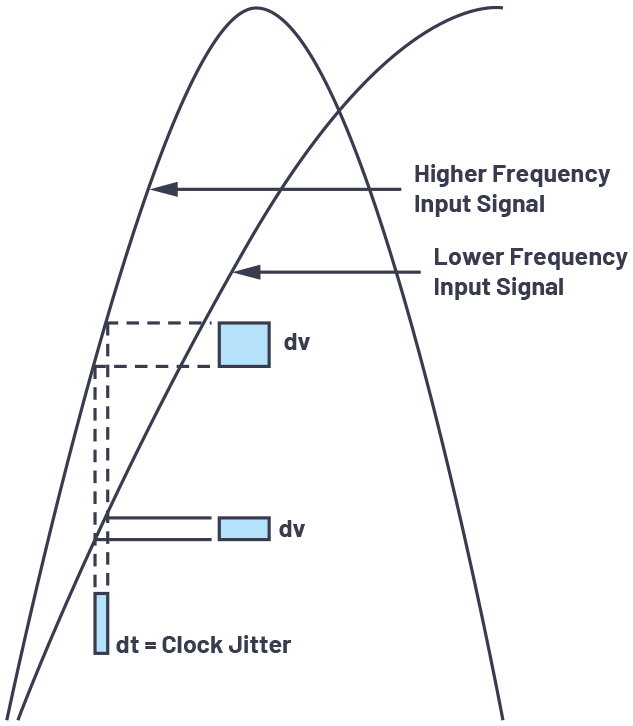

時鐘抖動

應用電路板上的時鐘路由對時鐘源的電源噪聲或與電路板上的其他信號耦合敏感,因為該噪聲會增加時鐘邊沿的不確定性。時鐘邊沿的不確定性被稱為抖動,采樣時鐘上有多種類型的時鐘抖動會影響ADC的性能。最常見的是周期間均方根抖動,其增加了模擬信號采樣點的可變性,導致性能下降,如圖8所示。有關均方根時鐘抖動對ADC性能的影響的更多詳細信息,請參閱相關文章2。

圖8.時鐘抖動引起模擬輸入采樣點的不確定性

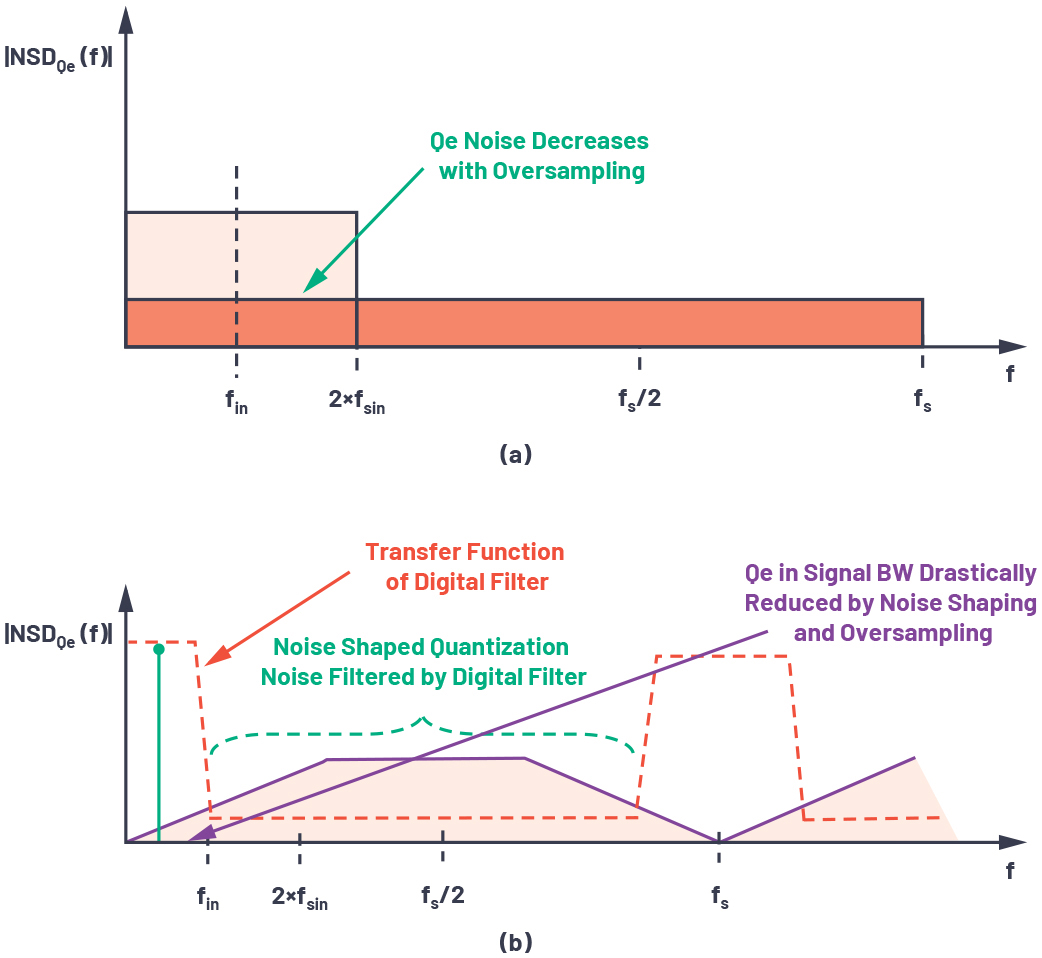

總結一下,時鐘抖動導致ADC數據的誤差增加可以量化為信噪比(SNR)的降低:

其中σj為均方根抖動。

當數字主機或時鐘源的噪聲很高時,式1意味著要達到所需的SNRj,我們要么限制輸入帶寬,要么采用額外的技術來濾除時鐘噪聲。

時鐘抖動是多通道應用的一個更嚴重挑戰,平衡同步和長時鐘布線引起的抖動增加需要良好的時鐘架構規劃3。在這種情況下,需要采取適當的隔離和緩沖措施以確保ADC具有低噪聲時鐘。隔離可利用常見的數字隔離器實現,但需要增加設計復雜度和功耗方面的預算。

圖9.奈奎斯特速率轉換器數據接口的局限性:(a) 時鐘時間約束(b) 多通道應用中的隔離要求

了解奈奎斯特速率ADC中的采樣速率控制之后,我們看一下過采樣ADC中使用的采樣速率控制技術。

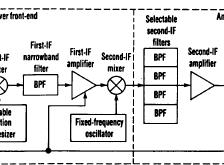

過采樣ADC中的采樣速率轉換

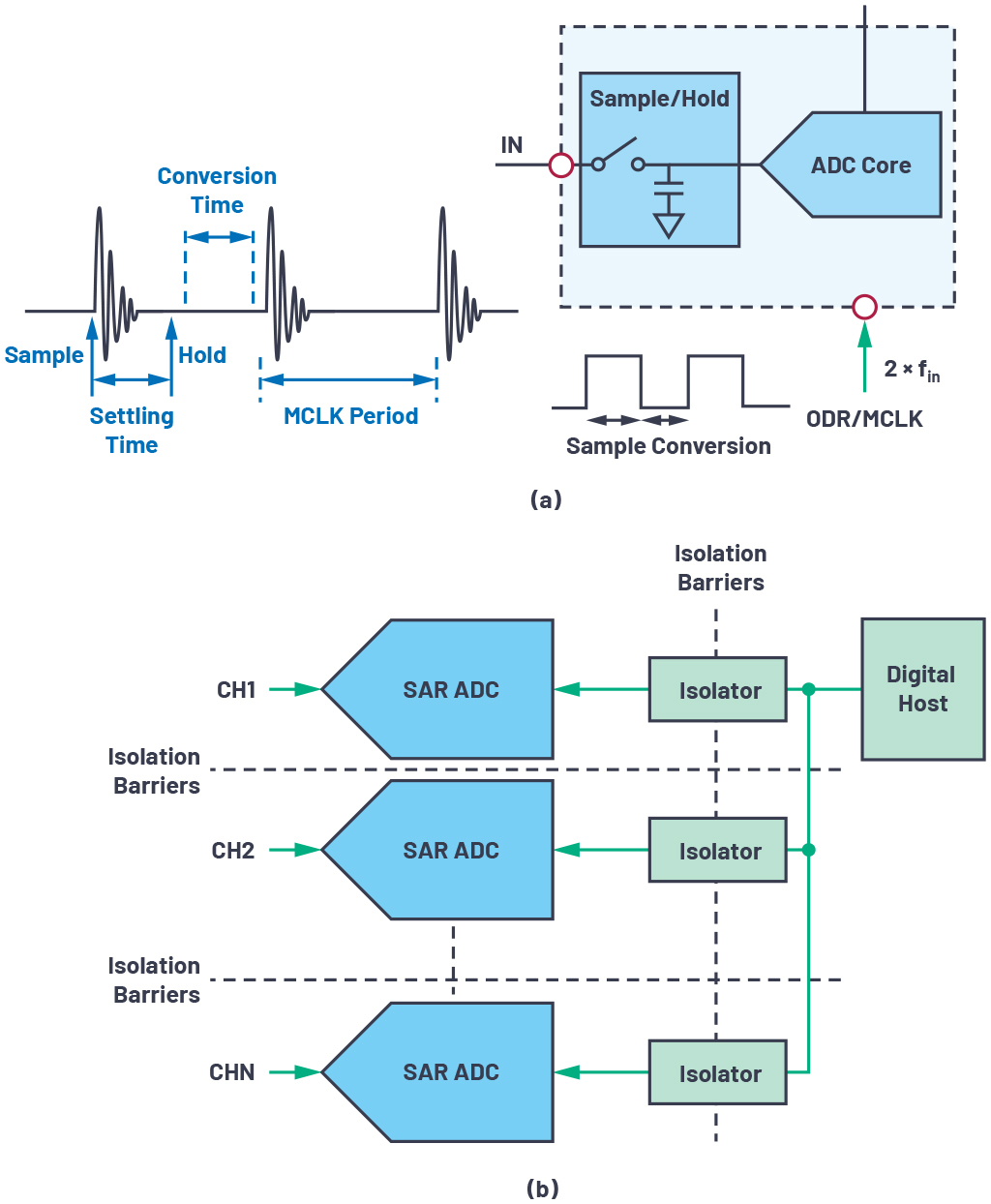

如本系列之前的文章所述,對連續時間信號進行采樣和數字化會有信息損失,并且會在采樣輸出中引入量化噪聲。有一類ADC遵循這樣的原則,即樣本數越大,精度越高,量化噪聲誤差越小。因此,其模擬輸入采樣速率高于奈奎斯特采樣速率,這被稱為過采樣。一些新型精密SAR ADC使用這種過采樣技術,被稱為過采樣SAR ADC。圖10a顯示了過采樣SAR ADC的噪聲優勢。另一類使用過采樣概念的ADC是Σ-Δ型ADC4,其量化噪聲Qe被進一步整形并向外推出,以提高目標輸入帶寬中的性能。圖10b顯示了Σ-Δ型調制器的量化噪聲的噪聲整形特性。在數學上,采樣頻率為OSR × fodr/2,其中OSR為過采樣率。

圖10.(a) 過采樣SAR ADC的頻譜,(b) Σ-Δ型ADC的頻譜

如果直接將核心ADC的過采樣數據與外部數字主機接口,那么后者將要接受許多冗余信息,導致過載。此外,在某些情況下,主機可能不支持這種高數字數據速率傳輸所需的嚴格時序約束,而且還會導致高功耗。因此,最優方式是僅提供目標輸入帶寬中的性能優化數據。這意味著,輸出數字數據速率應降低或抽取到奈奎斯特速率(2 × fin),或奈奎斯特速率的幾倍,具體取決于應用需要。因此,需要一種采樣速率轉換器來將ADC核心數據的高采樣速率fsin映射為所需的fodr。

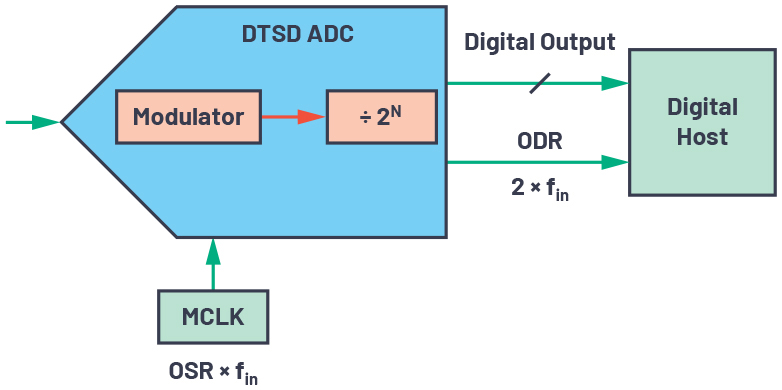

有一種稱為抽取的傳統數字采樣速率轉換技術,它能以2N的倍數濾波和抽取核心ADC數據,如圖11所示。向ADC提供稱為MCLK的輸入采樣時鐘。所需的數字輸出數據采樣速率(ODR/DRDY)時鐘——其為MCLK的分頻版本——作為輸出提供。基于所需的抽取率,通過設置N來實現分頻比。對于fodr編程,為了獲得更精細的分辨率,MCLK也可以根據應用的輸入帶寬要求進行調整。觀察過采樣ADC的數字數據接口,ODR時鐘由ADC給出和控制。這意味著ADC提供該時鐘,在主機模式下其名稱為ADC。

圖11.離散時間Σ-Δ(DTSD) ADC的數字數據接口

因此,將抽取用作采樣速率轉換技術時,ADC能以較低輸出數據速率提供高性能數字數據。但是,這種技術也有自己的局限性。

使用抽取控制采樣速率的局限性

非線性噪聲、功耗調整

在可變速率應用中,抽取率和MCLK兩者或其中之一可以調整。當僅提高抽取率時,fodr降低,噪聲隨著數字濾波器濾除更多量化噪聲而降低。只有數字濾波器的功耗線性降低。如果像在SAR ADC中討論的那樣降低MCLK,則整個ADC的功耗會線性降低,但噪聲會因為混疊折返而增加。

許多系統同時調整ADC的MCLK和抽取率來實現寬范圍的ODR,但這種方法可能導致測量噪聲性能或系統功耗性能發生不希望的階躍變化。

時鐘抖動

由于輸入采樣時鐘頻率fsin更高,因此過采樣ADC對時鐘抖動的敏感性比奈奎斯特速率SAR ADC更高,如式1所示。所以,時鐘源和MCLK的時鐘路由應基于應用容許的抖動噪聲來規劃。無論單通道還是多通道應用信號鏈,應用電路板上都會有許多切換信號在運行。來自這種高噪聲信號的耦合會提高MCLK上的時鐘抖動。因此,為了獲得最優ADC性能,需要利用數字隔離器來滿足MCLK的隔離需求。這種額外的設計規劃會帶來面積和功耗方面的成本。如前所述,為了讓fodr編程具有更精細的分辨率,MCLK也會調整。然而,具有所需fsin值和抖動性能的MCLK時鐘源可能很有限。

同步

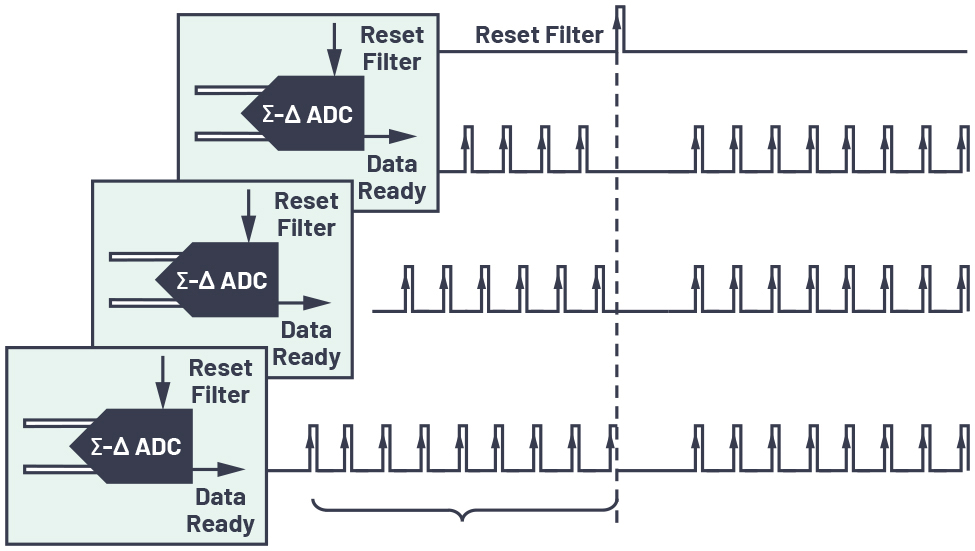

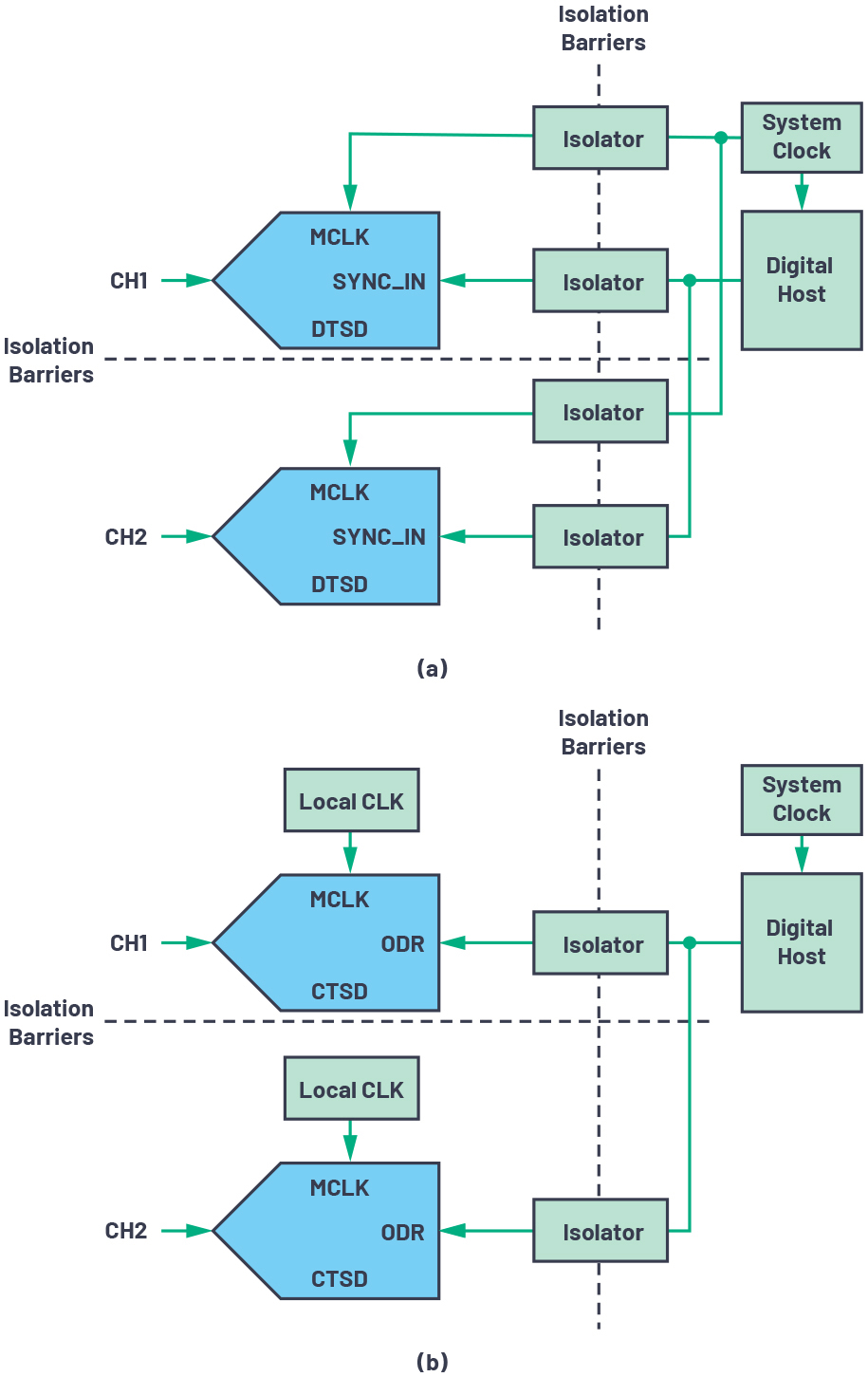

實現同步是過采樣ADC的另一個挑戰。通常,Σ-Δ型ADC中提供一個稱為SYNC_IN的額外引腳用于同步。SYNC_IN引腳的觸發會啟動對模擬輸入的同步采樣以及抽取濾波器的復位。經過數字濾波器建立時間之后,數字輸出數據是同步的。數字濾波器建立期間的數字輸出數據是中斷的,如圖12所示。它還假設,所有ADC的MCLK和SYNC_IN命令是同步的。在高采樣速率時鐘上實現這種同步,特別是在有隔離器或頻率合成器的情況下,會是一個巨大挑戰。一種致力于解決數據中斷和同步挑戰的系統解決方案是時鐘頻率合成器電路,例如PLL,它會為所有通道生成同步的MCLK。

圖12.發生數據中斷的DTSD ADC中的同步

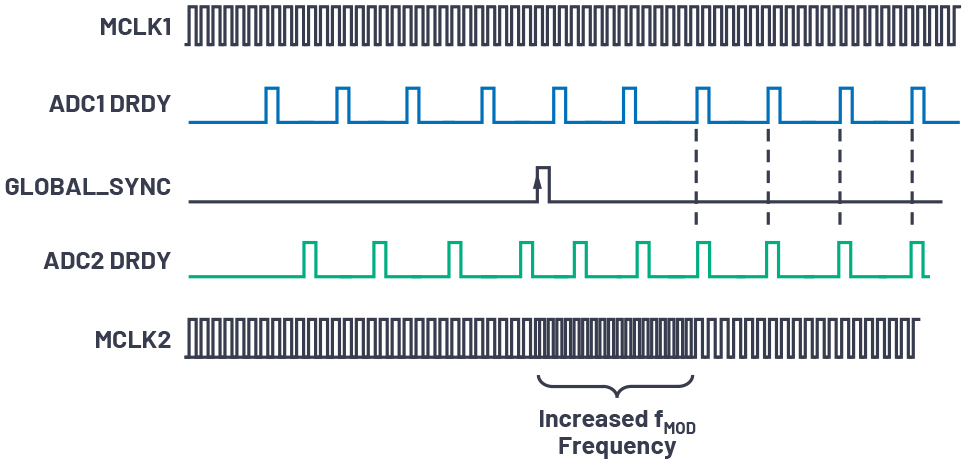

快速總結一下,當觸發SYNC_IN引腳時,PLL環路啟動與參考時鐘的時鐘同步。在PLL建立期間,MCLK速率會調整,使得在建立結束時,輸入ADC采樣邊沿和ODR時鐘邊沿同步。有關該解決方案的原理和細節,請參閱“同步關鍵分布式系統時,最新Σ-Δ ADC架構可避免數據流中斷”5。

圖13.基于PLL的DTSD ADC同步解決方案

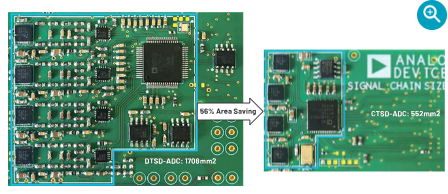

要點是,與SAR ADC相比,Σ-Δ型ADC或過采樣SAR ADC的同步多出了板載電路、PLL或時鐘頻率合成器要求,這會增加設計復雜性和功耗。ADI公司探索了另一種新穎的技術,稱為同步采樣速率轉換,它能在一定程度上幫助化解同步挑戰。

同步采樣速率轉換(SRC)

對于已討論的簡單抽取的若干挑戰,一種解決方案是使用同步采樣速率轉換6。SRC的優點是抽取率可以是fsin的任何整數或小數倍,從而可以更精細地控制fodr。ADI探索了該技術,并將其與AD7770中的精密DTSD轉換器配對使用。有關SRC的更多細節,請參閱AD7770的數據手冊或參考資料。

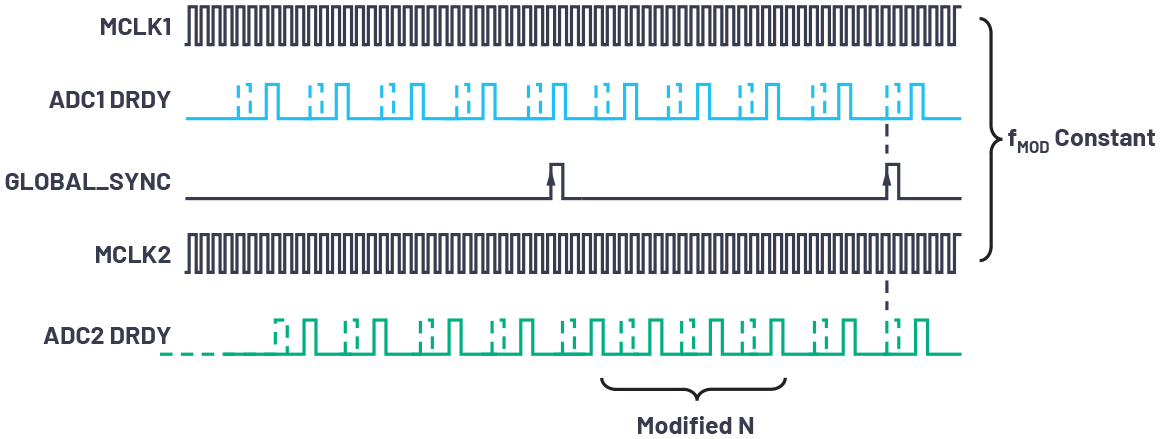

重點是,SRC中能以精細分辨率對fodr進行編程,因此同步變得更容易。例如,抽取率能以非常精細的步進變化,而無需調整外部MCLK。因此,當觸發SYNC_IN時,通道將會同步,如圖14所示。

圖14.使用SRC實現多通道同步

在不調整MCLK的情況下實現更精細的fodr,可以克服簡單抽取技術的大多數局限性。SRC也有自己的局限性和挑戰需要克服。

SRC的局限性

SRC并未解決讓所有通道具有相同MCLK的同步挑戰。

時鐘抖動/同步

在MCLK抖動方面,SRC具有與簡單抽取采樣速率控制相同的局限性。ADC性能對高fsin引起的時鐘抖動的敏感性,需要通過MCLK的隔離柵或噪聲濾波電路來解決。在多通道應用中,由于MCLK要路由到多個ADC通道,因此這一挑戰的難度進一步加大。為了實現同步,MCLK和SYNC_IN引腳信號需要同步,如圖16a所示。挑戰在于,所有時鐘同時到達ADC,與時鐘到PCB的距離和隔離柵可能造成的延遲相關。需要建立包括隔離柵和路由架構在內的精心設計的時鐘方案,以確保所有ADC通道經歷同樣的延遲,包括路徑中的隔離器。

接口模式

到目前為止,所討論的數字數據接口是主機模式和托管模式,其與ADC核心架構相關。例如,奈奎斯特速率ADC的數字數據時鐘由外部時鐘源或數字主機控制并提供。因此,它們只能被設置為托管模式。過采樣ADC提供并控制外部數字主機的數字時鐘。因此,它們只能被設置為主機模式。由此可見,上面討論的所有采樣速率控制技術存在一個普遍的局限性,那就是不能獨立地規劃數據接口。

對于大多數數字數據接口挑戰,一種解決方案是將MCLK時鐘域和ODR時鐘域解耦。因此,ADI公司重新引入了新穎的異步采樣速率轉換技術,使得ODR時鐘和數據接口時鐘相互獨立,從而打破了ADC核心架構長久以來的障礙,ODR時鐘的選擇和控制不再受限。

異步采樣速率轉換

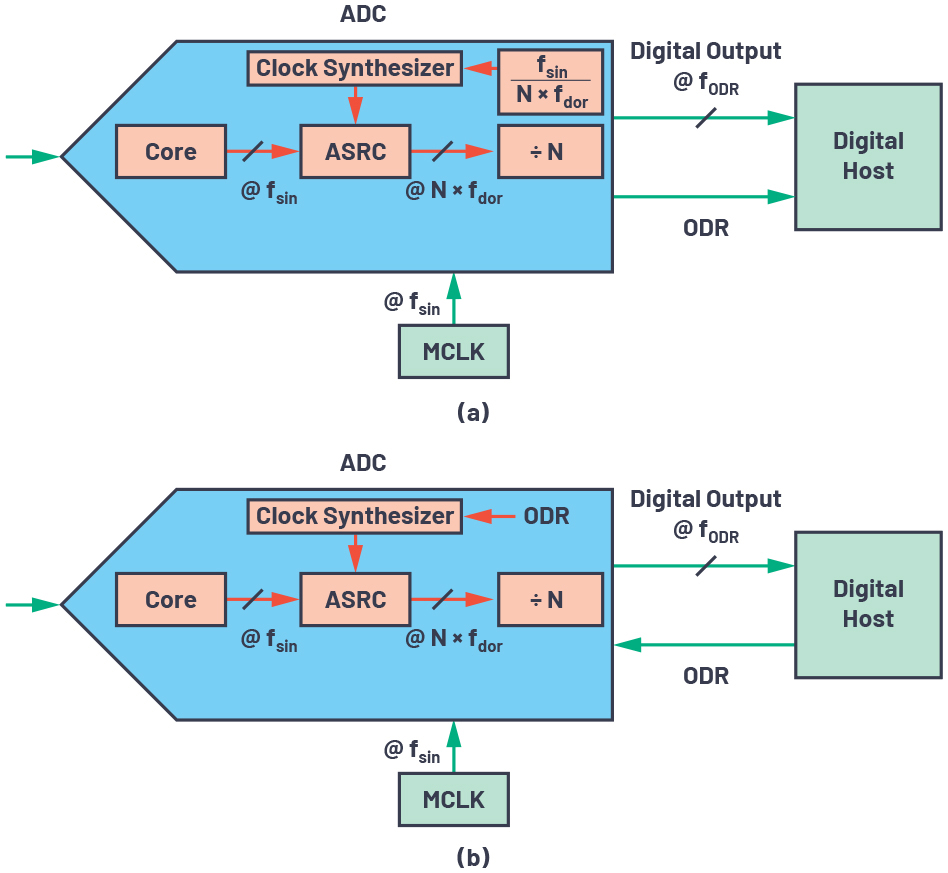

ASRC在數字域中以fsin對核心ADC數據重新采樣,并將其映射到任何所需的輸出數據速率。ASRC可以被認為是能夠實現任何非整數抽取的數字濾波器。然而,為了實現優化的性能、面積和功耗,應由ASRC處理小數抽取,然后由一個簡單的抽取濾波器來處理整數抽取,如圖15所示。ASRC對ADC核心數據重新采樣,并以fsin/N × fodr抽取數據。ASRC的輸出數據速率為N × fodr。同時,抽取濾波器得到所需的÷N抽取。

在某種形式的ASRC實現中,系數fsin/N × fodr可以由信號鏈設計人員根據ADC的fsin、所需fodr和從ADC上實現的抽取濾波器獲知的N來設置。這類似于設置SRC中的抽取率,不同點是抽取比率可以是無理數比率,并且支持非常精細的分辨率。在這種情況下,如同在SRC中,ODR時鐘與MCLK同步,并且是在片內通過MCLK分頻而產生的輸出。

另一種形式的ASRC實現是,ODR時鐘由外部時鐘源或類似于奈奎斯特速率轉換器的數字主體提供。在這種情況下,ASRC具有內部時鐘頻率合成器,它會計算fsin/N × fodr比率,并為ASRC和抽取濾波器產生所需的時鐘。ODR無需與MCLK同步,可以獨立設置為任何采樣速率。

圖15.ASRC實現:(a) 設置比率,(b) 片內計算比率

因此,無論何種形式,ASRC技術都支持信號鏈設計人員以細粒度設置fodr,并打破長久以來的限制,即fodr以輸入采樣速率的整數或小數比為限。結果是,ODR時鐘的采樣速率和時序要求現在純粹屬于數字接口的功能范圍,并且完全與ADC的輸入采樣頻率無關。這兩種實現形式的任何一種都展現了ASRC的優勢,信號鏈設計人員因而得以簡化數字數據接口設計。

ASRC的價值主張

MCLK和ODR時鐘解耦

在任何一種實現形式中,由于能以更精細的分辨率設置/調整fodr(調整幅度可以是幾分之一赫茲),因此ASRC允許獨立選擇MCLK和ODR時鐘速率。MCLK速率fsin可以根據ADC性能和時鐘抖動要求來選擇,而ODR時鐘fodr可以根據數字數據接口要求來實現。

時鐘抖動

在奈奎斯特速率轉換器和過采樣ADC中,我們都看到MCLK和ODR相關,需要調整MCLK以實現更精細分辨率的fodr。然而,能夠匹配任何fsin速率的MCLK之時鐘抖動要求的時鐘源是有限的。因此,需要權衡MCLK抖動引起的ADC性能降低和fodr的可能分辨率。就ASRC而言,可以選擇MCLK源以提供最佳的時鐘抖動,因為fsin的值可以獨立選擇,與ODR無關。

接口模式

ASRC讓MCLK和ODR的時鐘速率不再相關,因此接口模式的選擇有一定的自由度。任何具有ASRC后端的ADC都可以獨立配置為主機或托管外設,而不用考慮ADC核心架構。

同步

在先前討論的多通道同步技術中,MCLK時鐘路由有嚴格的要求。需要規劃隔離柵和時鐘架構以滿足時鐘抖動和同步要求。現在,每個通道的MCLK源可以是獨立的,如圖16b所示。在主機工作模式下,抽取率可以獨立設置以實現同步。在托管模式下,如圖16b所示,ODR可以共享和同步。由于ODR時鐘的速率較低且只是一個數字數據選通時鐘,因此它沒有像MCLK那么嚴格的抖動要求,故而可以放松對隔離柵或時鐘路由的嚴格要求。

圖16.(a) 使用SRC的Clock和SYNC_IN分配(b) 利用ASRC簡化時鐘和同步

總之,ASRC開辟了創新和簡化與外部數字主機接口的探索之道。此外,MCLK可以是獨立的,因而它非常適合與CTSD ADC配對使用。

ASRC與CTSD ADC配對

CTSD ADC核心對過采樣和噪聲整形的Σ-Δ概念也有效,同時提供電阻輸入、參考驅動和固有混疊抑制等架構優勢。這些特性大大簡化了模擬輸入前端設計。如第2部分所討論,由于核心ADC環路是一個連續時間系統,因此將環路系數調整為數據手冊中指定的固定輸入采樣速率。

CTSD ADC的局限性是MCLK不能像在DTSD或SAR ADC中那樣調整。如果CTSD ADC與SRC配對,則ODR將是該固定采樣時鐘的函數。這會限制CTSD ADC的使用范圍。應用需要的ODR可以是該固定fsin的無理數比。此外,CTSD ADC要求該MCLK精確且具有低抖動,以實現優化ADC性能。例如,精度要求可以是±100ppm左右,均方根抖動為10 ps。因此,MCLK將需要一個規劃良好的時鐘架構,以保證多通道應用中的抖動噪聲較低。MCLK是高頻時鐘,因而挑戰難度加大。

ASRC能讓MCLK和ODR解耦,非常適合應對CTSD ADC架構的局限性。MCLK時鐘源可以在本地且靠近ADC,避免長時鐘布線及耦合到其他信號,導致抖動噪聲增加。因此,ASRC與CTSD ADC的組合帶來一類新的ADC,其既有CTSD ADC的架構優勢,又能克服固定、低抖動MCLK的局限性。

結論

ASRC讓信號鏈設計人員可以獨立地以粒度選擇所需的輸出數據速率。另一個優點是,由于輸入采樣時鐘和ODR時鐘解耦,多通道應用中可以有效地規劃數字隔離。自由地配置數據接口而不用考慮核心ADC架構,是對信號鏈的另一種簡化。本文有助于了解相比于傳統采樣速率轉換,ASRC給數字數據接口帶來的各種優點和簡化。一般而言,ASRC可以與任何ADC核心架構配對,但與CTSD ADC配對可以簡化模擬輸入端及數字數據端的完整信號鏈設計。明確ASRC的需求和價值主張之后,請留意后續文章,我們將深入闡述ASRC的概念及其構建模塊。這些細節有助于信號鏈設計人員了解與ASRC相關的性能指標,并在應用中發揮其優勢。

參考資料

1Walt Kester。“MT-002教程:奈奎斯特準則對數據采樣系統設計有何意義。”ADI公司,2009年。

2Derek Redmayne、Eric Trelewicz和Alison Smith。“設計筆記1013:了解時鐘抖動對高速ADC的影響。”凌力爾特,2006年。

3Pawel Czapor。“Σ-Δ ADC時鐘——不只是抖動。”模擬對話,第53卷第2期,2019年4月。

4Michael Clifford。“Σ-Δ型ADC拓撲結構基本原理:第1部分。”ADI公司,2016年1月。

5Lluis Beltran Gil。“同步關鍵分布式系統時,最新Σ-ΔADC架構可避免數據流中斷。”《模擬對話》,第53卷第3期,2019年9月。

6Anthony O’Shaughnessy和Petre Minciunescu。“AN-1388:使用AD7779 24位同步采樣Σ-Δ型ADC實現電能質量測量的相干采樣。”ADI公司,2016年2月。

AD1893數據手冊。ADI公司。

-

adc

+關注

關注

98文章

6495瀏覽量

544468 -

數據接口

+關注

關注

1文章

79瀏覽量

17836 -

多速率轉換

+關注

關注

0文章

2瀏覽量

5712

發布評論請先 登錄

相關推薦

CTSD ADC:如何改進精密ADC信號鏈設計

RF采樣:全新的采樣速率數據轉換器

FPGA與ADC數字數據輸出的接口

利用異步采樣速率轉換簡化數字數據接口

CTSD精密ADC:利用異步采樣速率轉換(ASRC)簡化數字數據接口

CTSD精密ADC:輕松驅動ADC輸入和基準電壓源,簡化信號鏈設計

CTSD精密ADC—利用異步采樣速率轉換(ASRC)簡化數字數據接口

CTSD精密ADC—利用異步采樣速率轉換(ASRC)簡化數字數據接口

評論