正如每個工程師在早期階段都知道的那樣,必須遵守時鐘沿。在數字領域,通過全局和本地時鐘樹的同步、擺率和上升/下降時間都結合在一起,使產品“滴答”。同時使用時鐘信號的上升沿和下降沿來增加數據吞吐量的概念——所謂的雙倍數據速率或 DDR——徹底改變了數字設計。

今天,DDR 被用于計算機系統中的許多接口,其中之一與處理器與內存的接口方式有關。每個新應用程序都會突破此界面的限制。最新的技術,如人工智能 (AI)、機器學習 (ML) 和數據挖掘,將使其更加困難。

針對高帶寬 SDRAM 的最新版 DDR 接口 DDR5 的開發始于 2017 年。JESD79-5 DDR5 SDRAM 標準于 2020 年 7 月發布,比預期晚,甚至更受熱捧。

DDR5帶來了什么?

與 DDR4 相比,DDR5 承諾的主要功能是降低功耗和雙倍帶寬。這意味著從 3.2 Gbps 增加到 6.4 Gbps,時鐘頻率也相應地從 1.6 GHz 增加到 3.2 GHz。通過將電源電壓略微降低 (0.1 V) 至 1.1 V 來解決低功耗方面的問題。

這伴隨著電源管理的轉變,從主板轉移到雙列直插式內存模塊 (DIMM)。DIMM 容量也從 16 Gb 增加到 64 Gb,從而產生更高容量的內存模塊。通道數量的變化補充了這一點,每個 DIMM 從 1 個變為 2 個,每個 DIMM 都有一個 40 位數據通道,而 DDR4 中只有一個 72 位數據通道。數據位的總數保持不變,但通過兩個通道傳遞數據位會對時鐘信號的生成和分配方式產生影響。這是為了提高信號完整性(SI)。

雖然較低的電源電壓會降低功率,但它具有較小的噪聲容限,這會影響設計。但是,DDR5 還將電源管理 IC (PMIC) 從主板移到模塊上。這是另一個重大變化,它使電源管理、電壓調節和上電排序在物理上更接近模塊上的存儲設備。這也應該有助于電源完整性 (PI) 并提供對 PMIC 運行方式的更多控制。

設計挑戰:PI 和 SI

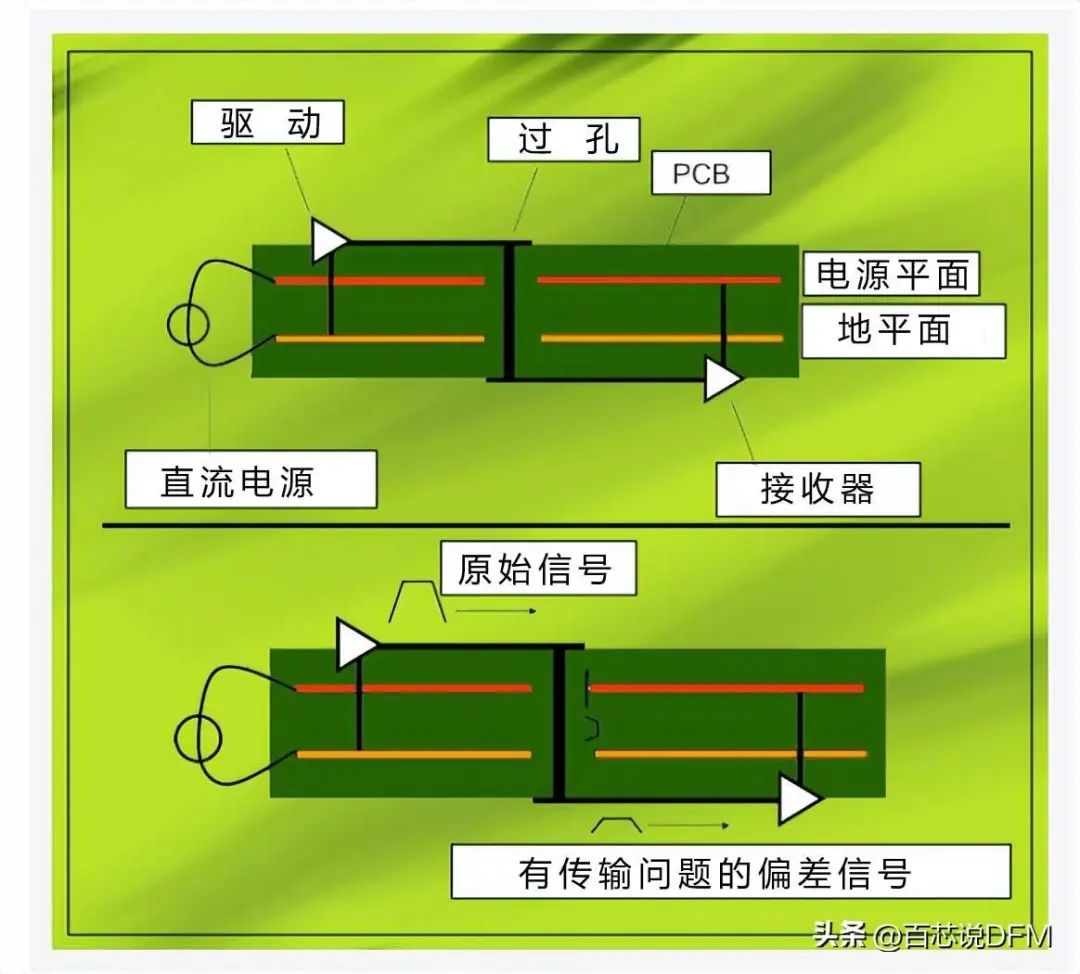

很明顯,在標準的開發過程中已經考慮了信號完整性,將 PMIC 移至模塊也應該帶來其自身的優勢。然而,設計人員仍需要考慮功率感知信號完整性的整體影響。傳統的工作流程會假設一個理想的配電網絡 (PDN),并且可能會忽略耦合信號、電源和接地層對整個 PCB 的整體信號完整性的影響。如果分別分析電源完整性和信號完整性,則可能會遺漏電源感知信號完整性問題。

這包括同時開關噪聲 (SSN),它被比作 PCB 中的地反彈。實際上,SSN 具有改變接地層電位的效果,或者它也可能表現為電源軌上的下降,這是由于多個接收器同時切換并且消耗的功率超過了 PDN 在那一刻所能提供的功率。當多個信號一起切換時,高速并行總線(例如 DDR)可能會特別受到 SSN 的影響(圖 1)。

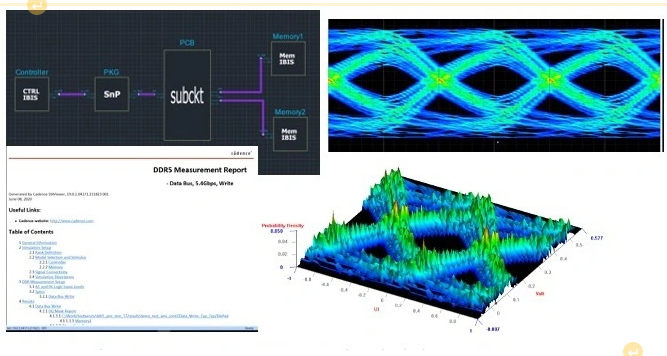

圖 1 DDR5 信號質量與使用 2D 和 3D 眼圖的 JEDEC 規范進行比較。資料來源:Cadence 設計系統

對 SSN 的影響進行準確建模并非天生簡單,大多數傳統 EDA 工具使用單獨的功耗感知模型來解決它;例如,IBIS 5.0+ 模型和互連模型。大多數信號完整性工具無法執行 SSN 分析,因為一旦布局完成,功率感知互連模型就可用。這意味著設計階段的噪聲分析通常僅限于設計規則和幾何規則檢查。

FDTD方法

在當今使用的大多數仿真技術中,信號分析和 PDN 之間存在根本性的脫節。這是一個帶有其他缺點的傳統,因為底層仿真技術早在設計以 Gbps 速度運行的并行總線(如 DDR5)之前就已經開發出來了。

通常,SPICE 模型的復雜性可能會有所不同,使用時域仿真來生成準確的 RLC 模型,同時有時會假設一個理想的基礎。這會產生基于簡單頻率響應的時域模型,通過仿真提取。這犧牲了準確性以換取權宜之計,而對于更高的頻率,工程師轉向可以使用混合求解器創建的 S 參數。SPICE 模型和 S 參數都很有用,尤其是因為 S 參數不包含任何低頻或直流信息。

有限差分時域方法或 FDTD 與混合求解器一起使用,可將覆蓋范圍擴展到信號、電源和接地線。集成和組合多個求解器的輸出以解決電路布局以及傳輸線和電磁場的工具能夠更好地提供數據和電源/接地平面之間的時變交互。一個例子是Sigrity SPEED2000引擎,它使用 FDTD 方法來分析 IC 封裝和 PCB 的布局。

簽核模擬

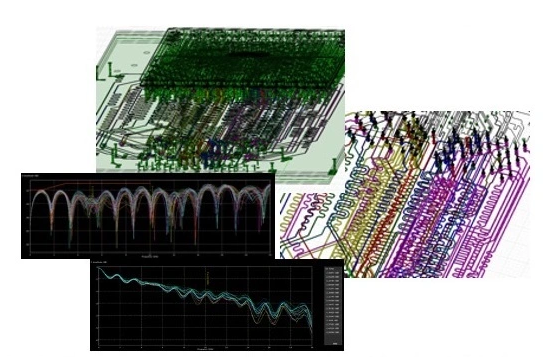

使用 FDTD 方法支持快速設計流程,并訪問支持多域規則檢查和仿真的功率感知信號完整性分析。但對于最終簽核,工程師可能仍會轉向 3D 全波建模方法,因為這提供了所需的精度(圖 2)。

圖 2信號完整性簽核過程需要對跨多??個層和多個結構的耦合信號進行準確的 3D 建模。資料來源:Cadence 設計系統

這種準確性是以計算能力和模擬時間為代價的。這可以通過分段來解決,但這只會將問題分解成更小的部分;這些碎片仍然需要處理。

這就是并行化提供真正性能優勢的地方。通過使用基于有限元分析 (FEM) 的方法,將任務分解為更小的部分,這些部分可以分布在大規模并行架構中,例如數據中心或云服務器。分析結果重新組合成基于頻率響應的 S 參數模型。FEM 由Clarity 3D Solver提供,然后 Sigrity 技術可以分析模型。

DDR5 的功率感知信號完整性

傳統的信號分析通常在 PDN 是“理想”的假設下運行。這是為了方便和權宜之計,而不是準確性。隨著我們進入具有 6.4-Gbps 數據速率和 3.2-GHz 系統時鐘的 DDR5 領域,功耗感知信號完整性問題的可能性開始變得更加顯著。

如果工程師希望采用 DDR5 提供的性能,則越來越有必要在系統中的所有關鍵點應用功耗感知信號完整性分析:芯片、封裝和 PCB。這種分析水平會對底層計算平臺提出巨大的要求,更不用說總設計時間了。

沒有一種方法可以提供完全解決功率感知信號完整性分析所需的覆蓋范圍。建議使用一種整體處理分析的方法,主要要求是具有最終將信號、電源和接地作為完整電氣系統進行分析的工具層次結構。

在該層次結構中,設計人員可以使用電氣規則檢查 (ERC) 來估計電源層和接地層之間的噪聲耦合。然而,最終解決方案必須包括功率感知信號完整性分析,該分析結合快速準確的場求解器以進行互連提取。

Brad Griffin是 Cadence Design Systems 的多物理場系統分析產品管理組總監。

-

SDRAM

+關注

關注

7文章

430瀏覽量

55317 -

DDR5

+關注

關注

1文章

430瀏覽量

24193

發布評論請先 登錄

相關推薦

DDR5的基本信號完整性 DDR5頻率相關損耗和反射

信號完整性仿真:DDR3/4/5系列地址信號端接優化對比

Introspect DDR5/LPDDR5總線協議分析儀

淺談確保信號完整性的電路板設計準則

DDR2-800和DDR3的PCB信號完整性設計

淺談DDR5 的功率感知和信號完整性

淺談DDR5 的功率感知和信號完整性

評論