ADAS的技術使駕乘體驗更舒適、更安全、更智能。TI Jacinto

TDA4VM&DRA829處理器是TI最新一代的處理器,以先進的高集成度和多核異構的高性能處理能力,展現(xiàn)了其靈活的處理能力和極具競爭力的成本,為ADAS技術實現(xiàn)提供了極具競爭力的平臺。 在ADAS的應用中,攝像頭作為感知模塊,越來越多地攝像頭被部署在應用中,感知能力的大小對應用來說至關重要,因此,本文將介紹Jacinto7處理器攝像頭接入和ISP的處理能力。

Jacinto7 圖像接入

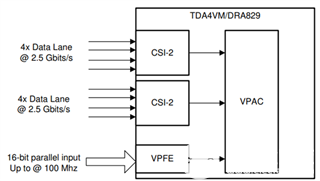

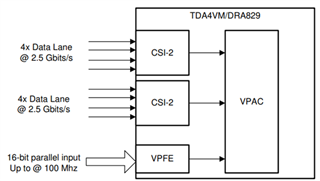

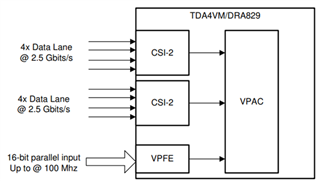

Jacinto7 TDA4VM/DRA829攝像頭接入子系統(tǒng)包含了2x MIPI CSI-2接口 和video processing front end(VPFE),可以支持多個攝像頭的接入。

圖1 : TI Jacinto7攝像頭接入子系統(tǒng)

對于MIPI-CSI2接口支持情況如下:

- 2x MIPI D-PHY with 4 lanes (2.5Gbps/lane)

- Supports 8 sensors with de-serializer Hubs

- 2x Camera Adaptation Layer (CAL)

– Protocol stack for MIPI CSI2

– Supports all MIPI supported formats

- RAW/DPCM/YUV

- RAW 8, 10, 12, 14, 16 bits

– Companied or linear

– Real-time priority on I/F port traffic

VPFE輸入接口模塊用于接收原始圖像、視頻數(shù)據(jù)、YUV等數(shù)字圖像數(shù)據(jù)。VPFE支持的功能如下:

- Support for conventional Bayer pattern and Foveon sensor formats.

– Generates HD/VD timing signals and field ID to an external timing generator or can synchronize to the external timing generator

– Support for progressive (non-interlaced) and interlaced sensors

– Support for up to 110-MHz sensor clock.

– Support for REC656/CCIR-656 standard (YCbCr 422 format, either 8- or 16-bit).

– Support for YCbCr 422 format, either 8- or 16-bit with discrete HSYNC and VSYNC signals.

– Support for up to 16-bit input.

因此,從圖像接入來說,TDA4VM/DRA829 MIPI-CSI2的每個接口有10Gbps 的帶寬,兩個MIPI-CSI2有20Gbps的帶寬,每個CSI2接口支持16個Virtual Channels,因此兩個CSI2接口可以支持多達32路攝像頭。EVM可以方便展示多達8路2M攝像頭的接入。

Jacinto7 圖像處理

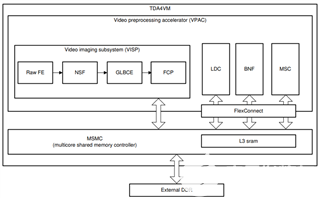

Jacinto7集成了視覺預處理加速器Vision Pre-processing Accelerator(VPAC), 提供了常用的圖像處理功能,比如顏色處理和增強、噪聲過濾、寬動態(tài)(WDR)、鏡頭畸變矯正、圖像金字塔、圖像縮放等。基于TI 超過20年在數(shù)百萬種產(chǎn)品中部署的多個Soc系統(tǒng),TI發(fā)布了最新一代的成像系統(tǒng),即德州儀器第七代ISP,并被集成在了Jacinto7 TDA4VM和DRA829處理器。

如圖2 VPAC系統(tǒng)框圖所示,由以下主要模塊組成:

- Video Imaging Subsystem (VISS)

- Lens Distortion Correction (LDC)

- Bilinear Noise Filter (BNF)

- Multi-scaler (MSC)

圖2 : TI Jacinto7 VPAC 系統(tǒng)框圖

VISS(Video Imaging Subsystem)模塊主要處理RAW數(shù)據(jù)并輸出RGB或YUV圖像。其包含RAW FE(Raw Front End)、NFS(Noise Filter)、GLBCE(Global and Local Brightness Contrast Enhancement)、FCP(Flex Color Processing)等模塊。

LDC(Lens Distortion Correction)主要對圖像進行畸變矯正。

MSC(Multi-Scalar)主要功能是對圖像進行縮放。

BNF(Bilateral Noise Filtering)雙邊濾波去除噪聲。

TDA4VM的VPAC的處理能力是720MP/s,因此理論上可以對24M RAW攝像頭的數(shù)據(jù)進行處理。

Jacinto7 Use Cases

Jacinto7 的用戶經(jīng)常會問TDA4VM/DRA829能夠接幾個攝像頭,有幾個ISP,ISP能夠處理幾路攝像頭的問題。 通常我們經(jīng)常使用MIPI-CSI2接收圖像,使用VPAC里面VISS對RAW圖像進行處理。TDA4VM/DRA829處理器有兩個CSI-2接口,一個ISP, ISP可以分時處理多路圖像, 其吞吐量如下表所示:

|

IP |

Max Throughput |

|

CSI-2*2 |

10Gbits*2 |

|

VPAC |

720 MP/s |

當前的SDK中已經(jīng)支持攝像頭查看Release Notes(https://software-dl.ti.com/jacinto7/esd/processor-sdk-rtos-jacinto7/latest/exports/docs/imaging/imaging_release_notes.html#ImageSensor_Support)

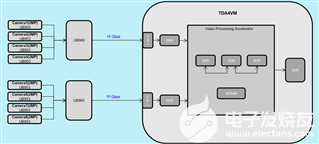

PSDKRA Multi Camera Use Case 1

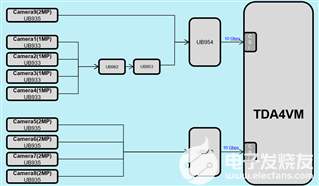

Jacinto7 SDK支持Multi Camera Use Case,其系統(tǒng)框圖如圖3所示,該Demo同時可以接入8個2MP@30FPS攝像頭,攝像頭先通過FPD LINK串化器UB953,然后通過同軸接入FPD LINK解串器UB960,最后通過TDA4VM MIPI-CSI2接口接入TDA4VM進行圖像處理。

該Demo可以在EVM快速搭建,需要TDA4VM EVM、Fusion Board(攝像頭接口板)和8個AR0233或IMAX390攝像頭。

圖3 : TDA4VM Multi Camera Use Case 1

該Use Case的利用率如下8*2MP@30FPS(RAW12):

|

IP |

Max Throughput |

Utilization |

Utilization(Percentage) |

|

CSI-2 (Port1) |

10 Gbits |

2.88 Gbits |

28.80% |

|

CSI-2 (Port2) |

10 Gbits |

2.88 Gbits |

28.80% |

|

VPAC |

720 MP/s |

480MP/x |

66.66% |

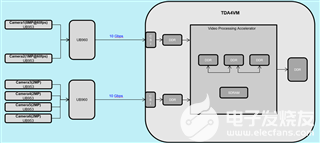

PSDKRA Multi Camera Use Case 2

當前的ADAS應用中,有4個2MP@30FPS攝像頭實現(xiàn)全景,1個8MP@30FPS實現(xiàn)前視,另外一個攝像頭完成DMS或后視功能。一個前視攝像頭其系統(tǒng)框圖如圖4所示:

- 1*8MPpixel@30fps RAW12 Front Camera

- 1*1MPpixel@60fps RAW12 Rear/DMS Camera

- 4*2MPpixel@30fps RAW12 Surround View (SRV) Camera

圖4 : TDA4VM Multi Camera Use Case 2

該Use Case的利用率如下:

|

IP |

Max Throughput |

Utilization |

Utilization(Percentage) |

|

CSI-2 (Port1) |

10 Gbits |

3.6 Gbits |

36% |

|

CSI-2 (Port2) |

10 Gbits |

2.88 Gbits |

28.80% |

|

VPAC |

720 MP/s |

540MP/x |

75% |

PSDKRA Multi Camera Use Case 3

在Jacinto7里面如果超過8個攝像頭應該怎么接呢?假如依舊使用TDA4VM CSI2的兩個接口,如果是9個或9個以上的攝像頭,需要如何接呢?FPD LINK有Cascading的功能,如下方案采用FPD LINK Cascading的功能,其系統(tǒng)框圖如圖6所示:

圖6 : TDA4VM Multi Camera Use Case 3-2

|

IP |

Max Throughput |

Utilization |

Utilization(Percentage) |

|

CSI-2 (Port1) |

10 Gbits |

2.16 Gbits |

21.6% |

|

CSI-2 (Port2) |

10 Gbits |

2.88 Gbits |

28.80% |

|

VPAC |

720 MP/s |

420MP/x |

60% |

總結

攝像頭的接入和處理能力對用戶方案至關重要,因此,本文對Jacinto7 TDA4VM/DRA829處理的攝像頭接入和處理能力進行了概述,并使用實際的Use Case 介紹了攝像頭的接入和處理方案,用戶可以根據(jù)實際應用需求對文中的方案進行修改。對于其它的Jacinto7的處理器,比如TDA4VL、TDA4AL、TDA4VMECO、TDA4VH、TDA4AH等處理器,本文也同樣適用,需要注意的是不同處理器的CSI和VPAC帶寬的不同,性能有所差異,因此需要根據(jù)帶寬進行換算。

審核編輯:符乾江

-

ISP

+關注

關注

6文章

476瀏覽量

51802 -

adas

+關注

關注

309文章

2183瀏覽量

208631 -

Jacinto

+關注

關注

0文章

11瀏覽量

5990

發(fā)布評論請先 登錄

相關推薦

詳解智能座艙內(nèi)部的各種攝像頭

攝像頭常見故障

智能攝像頭的音頻監(jiān)聽

RK3288在人臉識別上的應用及外接雙路攝像頭

ISP和攝像頭工作原理

回收蘋果攝像頭 收購蘋果攝像頭

回收手機攝像頭 收購手機攝像頭

OV7670攝像頭的設計

車載攝像頭提升自動駕駛產(chǎn)業(yè)鏈的智能化水平

Jacinto7處理器攝像頭接入和ISP的處理能力

Jacinto攝像頭接入與ISP處理

Jacinto 7攝像頭捕捉和成像子系統(tǒng)

Jacinto??攝像頭接入與ISP處理詳解

Jacinto??攝像頭接入與ISP處理詳解

評論