高速的數據轉換在設計中有很多和一般數據轉換設計中相似的問題,需要可靠的設計和穩定的結構。從基礎上來說,兩者并無二致,但受限于芯片的限制,高速數據轉換系統中更能窺見前沿的動態性能發展。

在一個高速數據轉換系統中,放大器、DAC、ADC這些都是必不可少的。一般先考慮運算放大器,接下來是在數據轉換中相當重要的采樣/保持,再是DAC,ADC這些。

不管是兼容于ECL還是兼容于TTL的DAC,它們有很多組成部分是相同的,尤其是核心電流控制部分。目前最典型的單片工藝可以做到的數模轉化器,12位分辨率,還原時間25ns,精度±0.01%,差不多都在這個范圍內。這種高速、高分辨率、低功耗的DAC包含了高精度的電流開關、放大器、NPN等等。NPN中的薄膜電阻利用激光平衡技術能夠在很寬的溫度范圍內維持12位的線性度。在這種DAC中,一般來說只有極少數電容因為太大而導致不能集成,需要作為濾波和旁路的片外器件。

高速DAC如何控制電流?

為了控制通過輸出開關的電流能足夠快,避免飽和十分重要,一旦晶體管飽和,恢復時間會遞增。不同的DAC結構有不同的特點,二進制結構的DAC可以得到很高的精確度,但問題在于在如此寬的電流范圍內,精確匹配分立的電源流和開關是很難的。

12位DAC滿刻度LSB電流仍然會太小難以匹配高速的開關。這種結構唯一的可取之處在于其不會損耗電流,耗散相比其他設計低得多。

另一種較為接近的方法是12位等值的電流開關,12位等值權的電流源與伺服控制環精確匹配。如果所有的晶體管和電阻都能匹配得很好,這是一種很理想的技術,在失效性能上是控制得最小的,代價是高功率耗散。

實際設計中,數模轉換器一般都是混合這兩種設計。相同電流密度的MSB電流與LSB電流持續匹配。為了盡可能控制失效性能,DAC傳播延遲在負值的同時也有正的邏輯變化;為了解決低位高電流供應,會犧牲提供的差動驅動器。如果以犧牲差動驅動器為代價來解決低位高電流供應,那芯片必須附加十二位的差動輸入。

設計中的誤差源

首先,為了使器件能夠保持高速,一個合適阻值的齊納擊穿是很有必要的。當ECL處在低電平時,本該截止的基極即使微導通,傳導的總量對于一個12位的DAC來說還是能夠承受的。

上面說到,薄膜電阻利用激光平衡技術能夠在很寬的溫度范圍內維持線性度。晶體管和薄膜電阻的匹配就是其中的誤差源。合理的晶體管匹配加之伺服環路的補償作用,能將溫度偏移性能控制得很好。配合合適的電阻選擇,可以獲得極其優秀的阻抗匹配。這種水平的設計做到一個高增益的,有±1/2LSB線性度的DAC不是難事。

剩下的兩個誤差源來自輸出阻抗以及重疊誤差。輸出阻抗比較好確定,比較公式化,通過合適的設計即可消除。重疊誤差的產生就有很多原因了。首先就是補償產生的重疊誤差,在R-2R梯度的反向線中電阻產生。這種效應可以通過盡可能減小梯度返回的阻抗來優化。

ECL DAC更佳的性能

通常在設計中都會利用ECL DAC,比較于TTL DAC,ECL的邏輯延遲更小、噪聲更低,還有一點則是ECL數據寄存器有著更低的數據不對稱性。數據不對稱性產生于所有數字輸入在相同的時間內不改變的時候,這種不對稱性可以理解為DAC輸出端口的失效率。

這個數值,一般通過測量LSB的單位失效區域來給出。失效時間的測量中,峰值失效振幅是器件帶寬的函數,當帶寬減少時,峰值幅度將會減小,失效將持續更長的時間。如果想進一步減小失效,可以進一步在DAC后面帶有的跟蹤和保持電路上做優化。

小結

高精度高速的數模轉換器對于設計、版圖、工藝、制造的要求都很高,必須嚴格把控設計中所有的單元都有著足夠的精度。

不管是兼容于ECL還是兼容于TTL的DAC,它們有很多組成部分是相同的,尤其是核心電流控制部分。CMOS技術也已經在數模轉換器中展現出了相當高的性能,雖然基于CMOS的DAC分辨率上做到雙極技術和差不多,但是速度這一指標上還是落下了雙極技術不少。GaAs技術近年來也開始被用于設計超高速DAC,其拓撲結構在某種程度上和雙極設計十分相似。

-

芯片

+關注

關注

460文章

52566瀏覽量

441827 -

dac

+關注

關注

44文章

2412瀏覽量

193974 -

轉換系統

+關注

關注

0文章

5瀏覽量

6347

發布評論請先 登錄

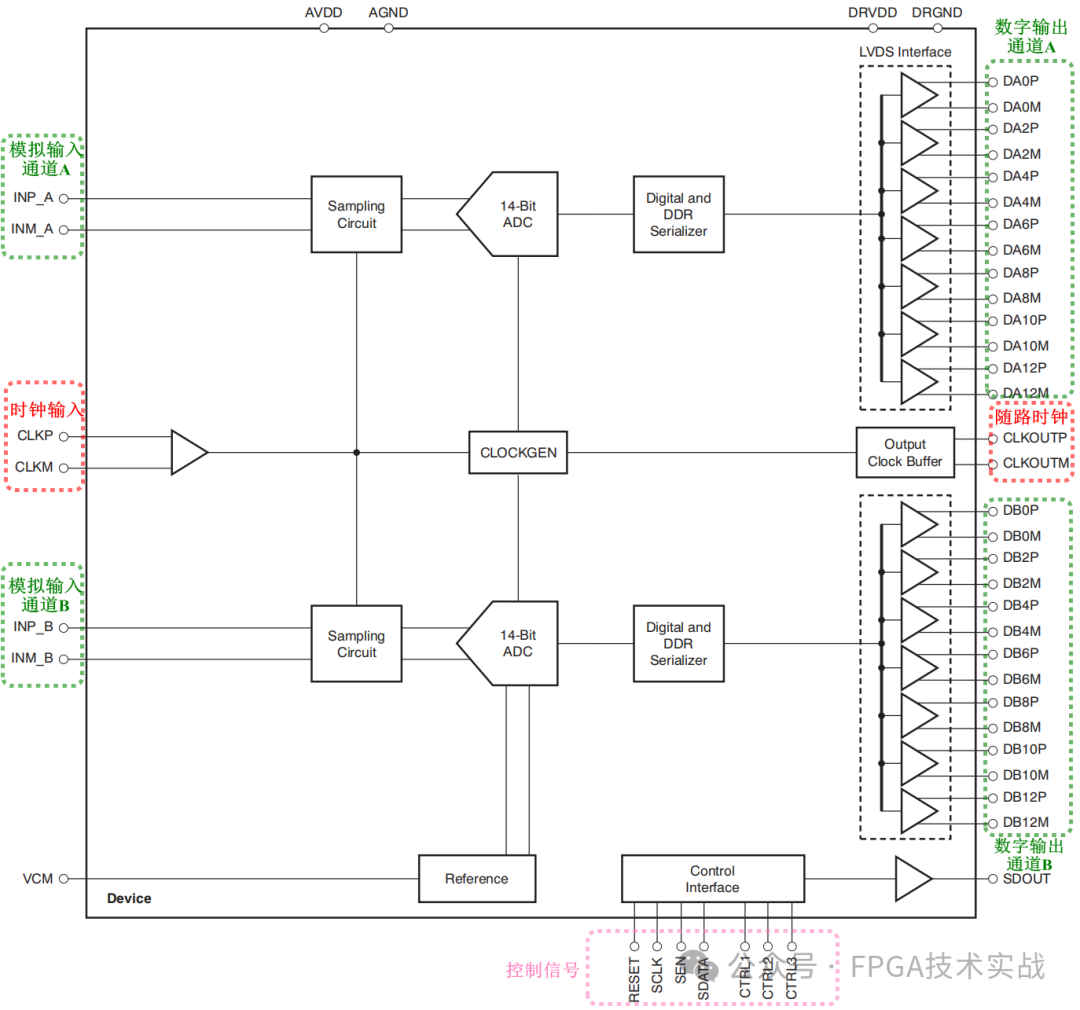

Altera FPGA與高速ADS4249和DAC3482的LVDS接口設計

高速ADC、DAC與處理器之間是怎么通信的呢?

高速ADC設計中采樣時鐘影響的考量

【GD32 MCU 入門教程】GD32 MCU 常見外設介紹(13)DAC 模塊介紹

DAC7642和DAC7643雙通道數模轉換器(DAC)數據表

DAC2904單芯片、14位、雙通道、高速數模轉換器(DAC)數據表

高速轉換系統中DAC如何考量

高速轉換系統中DAC如何考量

評論