簡介

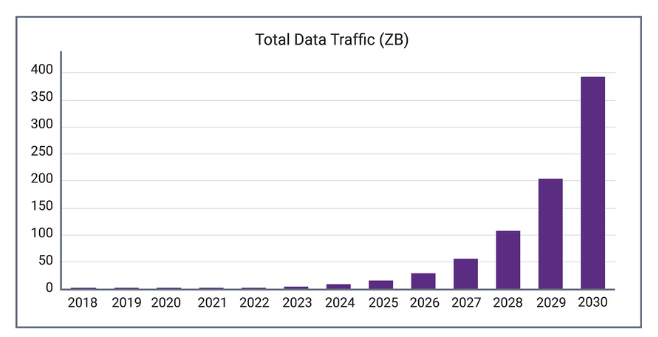

流媒體、監視和監控數據、聯網傳感器、社交媒體、在線協作、遠程學習、增強和虛擬現實、在線游戲……隨著無窮無盡的在線應用不斷涌現,在線數據量出現激增。預計在未來 10 年中,數據流量的年增長率將超過 400 倍(圖 1)。這種數據流量的快速增長,將對數據接口 IP 提出更高要求,需要其在速度和延遲方面,尤其是云基礎架構中都有顯著改善。本文將解釋在數據中心內、數據中心之間、服務器內以及 SoC 內等,加速數據傳輸和管理的技術發展。

圖 1:2030 年之前的總體數據流量預測。來源:《人工智能對于電子和半導體行業的影響》,IBS,2020 年 4 月。

數據中心內部和數據中心之間的長距離數據移動

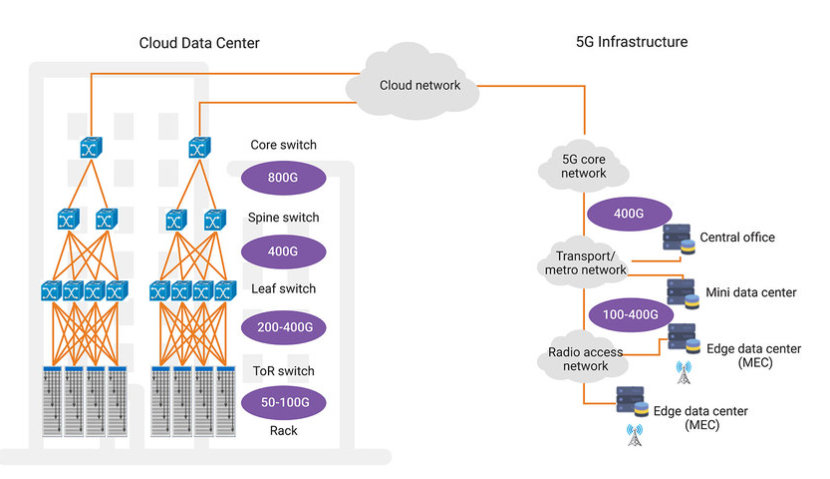

當今,大多數大型數據中心都使用 100Gbps 以太網基礎架構,數據跨越長距離(例如,在機架和數據中心之間)進行傳輸。長距離傳輸架構通常需要使用 4 個 25 Gbps 或 28 Gbps NRZ SerDes 連接通道。然而,隨著數據量的增長,需要速度更快的基礎架構來維持數據傳輸。使用支持 PAM-4 編碼的 56 Gbps 和 112 Gbps SerDes IP,在目前正在部署的超大規模數據中心中,可實現 400Gbps 的以太網連接,并在未來會實現高達 800Gbps 的連接速度(圖 2)。主要的以太網交換機供應商已經在開發基于 112G SerDes IP 的 800Gbps 交換機,計劃在未來幾年內推出 1.6Tbps 以太網(使用更快的新一代 SerDes),以滿足數據量不斷增長帶來的需求。

機架內服務器之間的數據通信,由頂層 (ToR) 交換機和網絡接口卡 (NIC) 管理。過去幾年,云數據中心在該級別最常用的接口速度為 25Gbps。但是,隨著基礎架構速度提高到 400Gbps,機架內的以太網速度也提高到了 100Gbps。

隨著數據速率的提高,接口功耗(通常以“皮焦耳/位”為測量單位)和面積變得越來越重要。物理接口 (PHY) IP 具有明顯的優勢,可最大限度地減少能耗,同時在所需距離內可靠地提供數據,從而可最大限度地降低基礎架構的功耗和散熱成本。節省空間的硅 PHY 解決方案可最大限度地降低 SoC 成本,從而為 SoC 供應商提高盈利能力。

圖 2:超大規模數據中心基礎架構逐漸轉向采用 400+GbE

服務器內部的數據傳輸

所有數據到達服務器后,就需要利用高速接口,在服務器內部的設備之間高效移動這些數據。例如,當數據以 100Gbps 的速度到達 NIC 時,必須將其快速移動到存儲器、系統內存,也可能移動到圖形或 AI 加速器,以進行處理。PCI Express (PCIe)、Computer Express Link (CXL) 和類似協議在這一方面具有優勢。為了應對流量的快速增長,PCI-SIG 于 2019 年發布了 PCIe 5.0,帶寬比上一代產品翻倍,并力爭在 2021 年發布 PCIe 6.0,再次使 PCIe 數據速率翻倍,達到 64 GT/s(每個 x16 卡的速率高達 128GB/s)(圖 3)。

圖 3:PCI Express 每個通道的帶寬升級過程。來源:PCWorld

近來,由計算系統生成和處理的數據量(尤其是非結構化數據)持續增長,已促使了新架構的產生,新架構通常采用加速器來加快數據處理。將數據從一個處理器域復制到另一個處理器域是一個資源密集型過程,這會顯著增加數據處理的延遲。緩存相干解決方案讓處理器和加速器共享內存,而無需將數據從一個內存空間復制到另一個內存空間,從而節省了復制數據所需的內存資源和時間。

CXL 是一種緩存相干協議,利用 PCIe 的數據速率和 PCIe 物理層,使 CPU 和加速器能夠訪問彼此的內存。在多個設備都需要訪問同一個數據集時,集成 CXL 協議可有效減少必須具有非相干協議的數據副本數,從而減少系統內所需的傳輸次數。減少數據副本數,有助于降低系統中大量已預留的內存和 IO 接口的負載。

與其他外設互連相比,用于高性能計算工作負載的 CXL 可顯著降低延遲。由于 cxl.cache 和 cxl.mem 事務的延遲僅為 50-80 納秒,因而在 PCIe 延遲中,CXL 延遲僅占一小部分。此外,CXL 通過使用資源共享提高性能并降低復雜性,這也降低了總體系統成本。

SoC 內的 USR/XSR 數據移動

許多現代服務器 SoC 利用在單個 package 內放置多個 Die,在符合設計和制造約束的范圍內提供所需的性能。因此,需要高速 die-to-die (D2D) 通信以在芯片內的 Die 之間傳遞大型數據集。超短距離/極短距離 (USR/XSR) SerDes 可實現這一傳遞,當前設計使用 112Gbps SerDes,并且在未來幾年內可能會達到更高的速度。

使用 D2D 接口技術的多芯片模塊可處理多種用例。所有 D2D 用例都縮短了開發時間,并降低了開發和制造成本。有些情況使用多個異構 Die(即“小芯片”),它們利用可重復使用的功能組件,每個組件都使用最適合其特定功能的制造技術構建。其他情況通過創建大型高性能 SoC 著重提高靈活性,此類 SoC 使用更小的同質構建模塊來提高良率和可擴展性。

圖 4:舉例展示 Die 間互連用例

總結

云數據的快速增長推動了對于更快、更高效接口的需求,以將云基礎架構內的數據從網絡和系統向下傳輸到芯片級數據通信中。新推出和正在開發的接口技術(包括 400Gbps 和更快的以太網、PCIe 6.0 和 CXL 外設互連技術,以及用于 Die 間通信的新型高速 SerDes)可實現必要的基礎架構改善,以支持不斷提高的云數據需求。

新思科技的 DesignWare? 高速 SerDes 和以太網 IP 支持實現新一代數據中心網絡解決方案。DesignWare PCIe IP 是一種穩定成熟的技術,在 90% 的領先的半導體公司得到應用,為實現 DesignWare CXL IP 奠定了基礎。DesignWare 112G USR/XSR SerDes IP 為多 Die SoC 提供低成本、節能的 die-to-die 接口。新思科技提供經過硅驗證且品類齊全的 DesignWare 接口 IP 產品組合,同時提供開發高速、低功耗、高度可靠的 SoC 所需的設計和驗證工具,以支持當今和未來云基礎架構不斷提高的數據移動需求。

審核編輯:符乾江

-

soc

+關注

關注

38文章

4161瀏覽量

218167 -

PCIe

+關注

關注

15文章

1234瀏覽量

82584 -

云數據

+關注

關注

0文章

117瀏覽量

16610

發布評論請先 登錄

相關推薦

RocketIO高速串行接口

汽車導航軟件是如何知道道路的實時擁堵情況的

關于高速數據流盤處理技術看完你就懂了

LabVIEW用NI-DAQmx高速數據流盤

通信網絡數據流量倒流應對策略

基于Interlaken協議的高速數據流接口設計

研究稱LTE數據流量今年將增長207%

到2017年,移動數據流量絕大部分由WIFI網絡處理

沃達豐表示網絡數據流量激增了50%

思科預測2025年全球數據流量將會從2020年的16ZB上升至163ZB?

高速ADC與FPGA的LVDS數據接口中避免時序誤差的設計考慮

利用高速接口IP避免云數據流量擁堵

利用高速接口IP避免云數據流量擁堵

評論