1. 塊語(yǔ)句有兩種,一種是 begin-end 語(yǔ)句, 通常用來(lái)標(biāo)志()執(zhí)行的語(yǔ)句;一種是 fork-join 語(yǔ)句,通常用來(lái)標(biāo)志()執(zhí)行的語(yǔ)句。

答案:順序,并行

解析:

(1)begin_end順序塊,用于將多條語(yǔ)句組成順序塊,語(yǔ)句按順序一條一條執(zhí)行(除了帶有內(nèi)嵌延遲控制的非阻塞賦值語(yǔ)句),每條語(yǔ)句的延遲時(shí)間是相對(duì)于由上一條語(yǔ)句的仿真時(shí)間而言;

(2)fork-join并行塊,塊內(nèi)語(yǔ)句同時(shí)執(zhí)行。

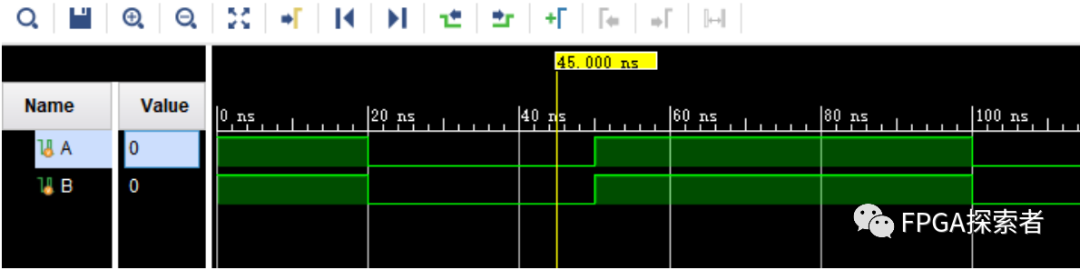

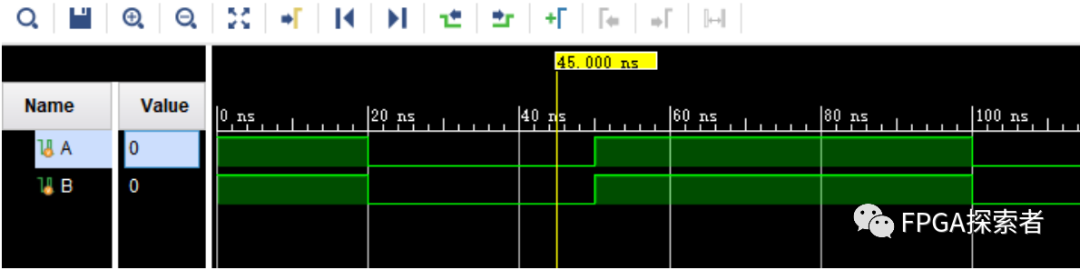

2. 塊語(yǔ)句,下面這段語(yǔ)句中,第 40 時(shí)刻上,A、B 的值各是多少?

reg A;reg B;initial begin fork begin A = 1; #20 A = 0; #30A=1; #50 A = 0; end begin B = 1; #20 B = 0; #30 B = 1; #50 B = 0; end joinend

答案:A = 0,B = 0

解析:

塊語(yǔ)句有兩種,begin...end 和 fork...join,其中 fork...join 是并行塊,begin...end 是順序執(zhí)行塊,可以相互嵌套。

上面,兩個(gè) begin...end 之間是并行的,而各自 begin...end 內(nèi)部是順序執(zhí)行,A 和 B 的賦值邏輯是一樣的,所以要么都是 1,要么都是 0。

按照順序執(zhí)行,A 前 20 個(gè)時(shí)間單位是 1,然后持續(xù) 30 個(gè)時(shí)間單位的 0,所以 40 時(shí)刻是 0,同理 B 也是 0。

審核編輯 :李倩

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

原文標(biāo)題:Verilog 的塊語(yǔ)句 fork...join 和 begin...end

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

相關(guān)推薦

Verilog與ASIC設(shè)計(jì)的關(guān)系 Verilog作為一種硬件描述語(yǔ)言(HDL),在ASIC設(shè)計(jì)中扮演著至關(guān)重要的角色。ASIC(Application Specific Integrated

![的頭像]() 發(fā)表于

發(fā)表于 12-17 09:52

?92次閱讀

Verilog測(cè)試平臺(tái)設(shè)計(jì)方法是Verilog FPGA開(kāi)發(fā)中的重要環(huán)節(jié),它用于驗(yàn)證Verilog設(shè)計(jì)的正確性和性能。以下是一個(gè)詳細(xì)的Verilog測(cè)試平臺(tái)設(shè)計(jì)方法及

![的頭像]() 發(fā)表于

發(fā)表于 12-17 09:50

?126次閱讀

Verilog 與 VHDL 比較 1. 語(yǔ)法和風(fēng)格 Verilog :Verilog 的語(yǔ)法更接近于 C 語(yǔ)言,對(duì)于有 C 語(yǔ)言背景的工程師來(lái)說(shuō),學(xué)習(xí)曲線較平緩。它支持結(jié)構(gòu)化編程,代碼更直觀,易于

![的頭像]() 發(fā)表于

發(fā)表于 12-17 09:44

?116次閱讀

介紹幾種自動(dòng)生成verilog代碼的方法。

![的頭像]() 發(fā)表于

發(fā)表于 11-05 11:45

?287次閱讀

本文繼續(xù)介紹Verilog HDL基礎(chǔ)知識(shí),重點(diǎn)介紹賦值語(yǔ)句、阻塞與非阻塞、循環(huán)語(yǔ)句、同步與異步、函數(shù)與任務(wù)語(yǔ)法知識(shí)。

![的頭像]() 發(fā)表于

發(fā)表于 10-24 15:00

?340次閱讀

reg 變量,因?yàn)?initial 塊是不可綜合的,只能在仿真環(huán)境中使用,用于初始化寄存器、內(nèi)存或執(zhí)行仿真期間的其他任務(wù)。

但在 FPGA 設(shè)計(jì)中,可以使用默認(rèn)賦值或者使用有條件的賦值語(yǔ)句來(lái)為 reg

發(fā)表于 09-12 19:10

條件語(yǔ)句用于基于不同的條件來(lái)執(zhí)行不同的動(dòng)作。

TypeScript 條件語(yǔ)句是通過(guò)一條或多條語(yǔ)句的執(zhí)行結(jié)果(True 或 False)來(lái)決定執(zhí)行的代碼塊。

![的頭像]() 發(fā)表于

發(fā)表于 04-01 13:51

?752次閱讀

Verilog中的模塊端口對(duì)應(yīng)方式,并提供示例代碼和詳細(xì)解釋?zhuān)詭椭x者更好地理解和應(yīng)用。 首先,我們來(lái)了解一下Verilog中的模塊和模塊端口。一個(gè)Verilog模塊被定義為包含一組聲明和語(yǔ)

![的頭像]() 發(fā)表于

發(fā)表于 02-23 10:20

?1747次閱讀

在Verilog中,repeat語(yǔ)句不需要使用begin和end塊。repeat語(yǔ)句是一種循環(huán)控制語(yǔ)句,允許重復(fù)執(zhí)行一個(gè)代碼

![的頭像]() 發(fā)表于

發(fā)表于 02-23 10:14

?1188次閱讀

Assign語(yǔ)句和Always語(yǔ)句是在硬件描述語(yǔ)言(HDL)中常用的兩種語(yǔ)句,用于對(duì)數(shù)字電路建模和設(shè)計(jì)。Assign語(yǔ)句用于連續(xù)賦值,而Always

![的頭像]() 發(fā)表于

發(fā)表于 02-22 16:24

?2530次閱讀

Verilog是一種硬件描述語(yǔ)言(HDL),用于設(shè)計(jì)和模擬數(shù)字電路。在Verilog中,關(guān)鍵字initial和always都是用于描述電路行為的特殊語(yǔ)句。它們被用來(lái)生成仿真模型,并控制模擬器的啟動(dòng)

![的頭像]() 發(fā)表于

發(fā)表于 02-22 16:09

?2834次閱讀

的for循環(huán)也是并行執(zhí)行的。 Verilog中的for循環(huán)可以用來(lái)實(shí)現(xiàn)重復(fù)的操作,例如在一個(gè)時(shí)鐘周期中對(duì)多個(gè)電路進(jìn)行操作。在循環(huán)內(nèi)部,多個(gè)語(yǔ)句可以同時(shí)執(zhí)行,而不受循環(huán)次數(shù)的限制。這種并行執(zhí)行的機(jī)制使得Verilog在硬件設(shè)計(jì)中非

![的頭像]() 發(fā)表于

發(fā)表于 02-22 16:06

?2905次閱讀

Verilog 是一種硬件描述語(yǔ)言 (HDL),主要用于描述數(shù)字電子電路的行為和結(jié)構(gòu)。在 Verilog 中,函數(shù) (Function) 是一種用于執(zhí)行特定任務(wù)并返回一個(gè)值的可重用代碼塊。函數(shù)在

![的頭像]() 發(fā)表于

發(fā)表于 02-22 15:49

?5529次閱讀

單片機(jī)中的if語(yǔ)句是一種條件語(yǔ)句,用于根據(jù)不同的條件執(zhí)行不同的代碼塊。在程序執(zhí)行過(guò)程中,條件語(yǔ)句用來(lái)決定是否執(zhí)行特定的代碼段。在單片機(jī)編程中,if語(yǔ)

![的頭像]() 發(fā)表于

發(fā)表于 01-05 14:04

?1757次閱讀

單片機(jī)中的for語(yǔ)句是一種常見(jiàn)的循環(huán)控制結(jié)構(gòu),用于重復(fù)執(zhí)行一段代碼塊,可以簡(jiǎn)化程序的編寫(xiě)和減少代碼量。本文將詳細(xì)介紹單片機(jī)中for語(yǔ)句的運(yùn)用。 一、for語(yǔ)句的基本結(jié)構(gòu)和功能 for

![的頭像]() 發(fā)表于

發(fā)表于 01-05 14:02

?2403次閱讀

Verilog的塊語(yǔ)句

Verilog的塊語(yǔ)句

評(píng)論