一般Fabless公司設計的芯片在工程批回來之后,都會做芯片級的ESD測試和latchup等測試,對很多客戶朋友來說,有可能對latchup稍微陌生,本篇文章將簡要介紹latchup。

latchup的中文譯名為閂鎖或閂鎖效應,要想了解清楚latchup,需要先了解MOS管的結構。

1MOS管的結構

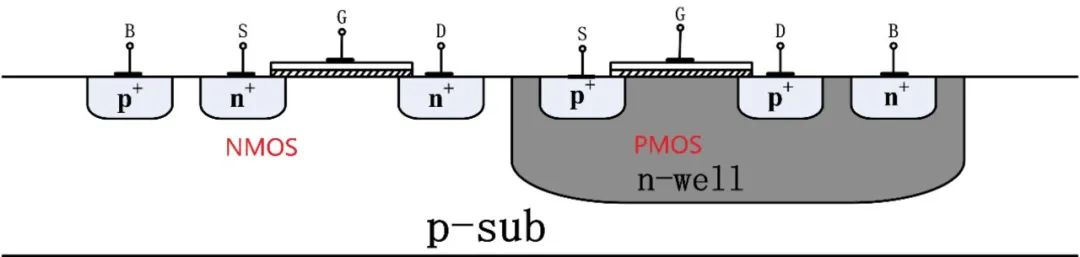

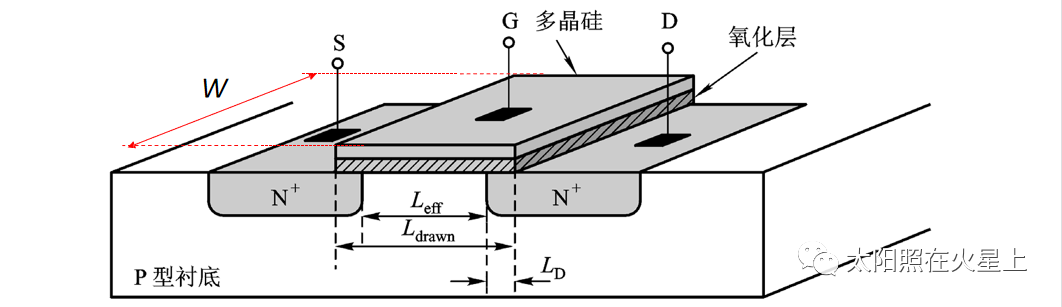

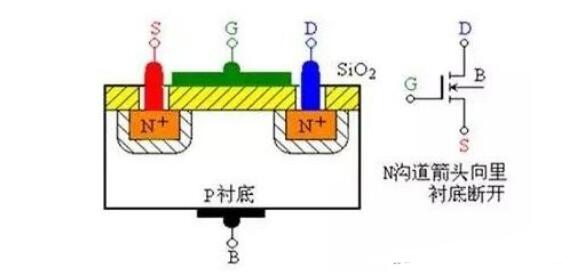

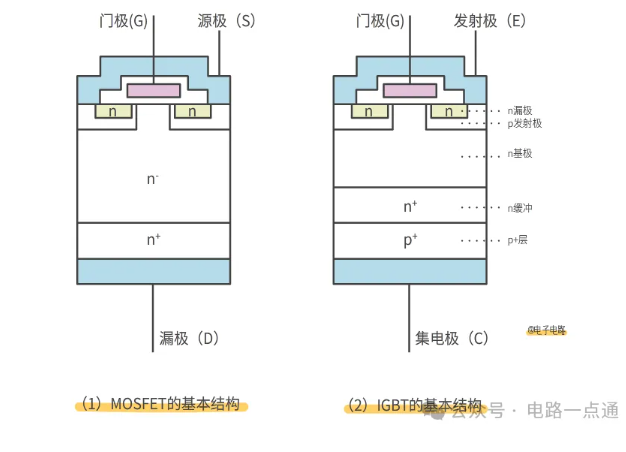

在CMOS電路中,有NMOS 和PMOS兩種晶體管。在制作NMOS時,首先是有一個P型襯底,一般稱為P-substrate,為避免將substrate和Source混淆(因首字母一樣),經常將P襯底稱為P-Body或P-Bulk。在P型襯底上,兩個重摻雜n區形成源端(Source)和漏端(Drain),重摻雜的多晶硅區(簡稱poly)作為柵(Gate),一層薄SiO2(簡稱柵氧)使柵與襯底隔離,而器件的有效作用就發生在柵氧化層的襯底區,因為襯底電位對器件特性有很大的影響,所以MOSFET是一個四端器件(即Gate、Drain、Source、Bulk)。

關于柵氧層,因為SiO2是絕緣的,所以NMOS管的輸入阻抗Rgs是無窮大,輸入電流趨近于零。現在國內發展得如火如荼的電容隔離器,隔離柵使用的絕緣介質也是SiO2。

在現代CMOS工藝中,PMOS器件做在n阱(即n-well)中,而之所以這么做,是因為在實際生產中,NMOS器件和PMOS器件必須做在同一襯底上,所有的NMOS器件都共享一個P襯底,而每一個PMOS可以處于各自獨立的N阱中。對于PMOS,源和漏重摻雜P型元素,導電載流子為空穴,柵源電壓足夠負,在氧化層-硅界面才會形成一個由空穴組成的反型層,從而為源和漏之間提供一個導電溝道,所以PMOS器件的閾值電壓通常是負的。

2latchup的形成原因

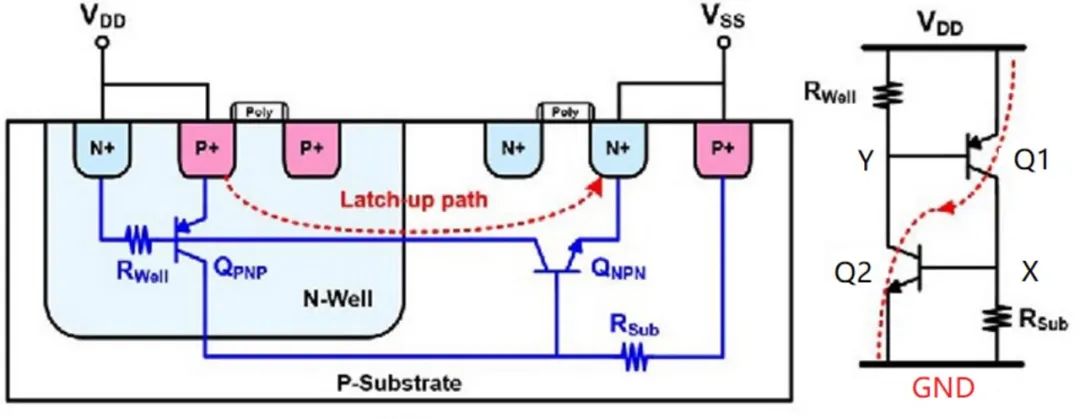

如下圖所示的NMOS和PMOS器件,會寄生出Q1 PNP管和Q2 NPN 管,從圖中可以看出,每個雙極型晶體管的基區必然與另一個晶體管的集電區相連接,而且由于n阱和p襯底均有一定的電阻,所以Q1和Q2會形成一個正反饋環路。

實際上,如果有電流注入結點X使Vx上升,則Q2的Ic2增大,那么Vy=VDD-Rwell*Ic2會減小,Vy減小會導致IC1增大,進而導致Vx進一步上升。如果環路增益≥1,這種現象會持續下去,直至兩個晶體管都完全導通,從VDD抽取很大的電流。此時稱該電路被閂鎖。

觸發閂鎖效應的起始電流可以由集成電路中的各種原因產生,例如當漏端的一個大電壓擺動,會通過容性耦合向n阱或襯底注入相當大的位移電流,從而引發閂鎖效應。

閂鎖效應通常發生在大尺寸的輸出反相器的情況下,因為在這種情況下,一是這種電路容易通過晶體管較大的漏結電容向襯底注入大電流,另外一種情況,是由于在與地相連的鍵合線上,產生相當大的瞬態電壓,通過正偏源襯二極管向襯底注入大電流。

Latchup就是閂鎖效應,它是CMOS工藝所特有的寄生效應,是指在CMOS電路中,電源VDD和地GND之間由于寄生的NPN和PNP雙極性BJT的相互影響而產生一個低阻通路,低阻通路會在電源和地之間形成大電流,可能會使芯片永久性損壞。

榮湃半導體

榮湃半導體創立于2017年,專注于高性能模擬集成電路產品的研發與設計,聚焦數字隔離器、驅動器、隔離放大器等產品系列,并廣泛應用于工業控制、新能源汽車、數字電源、智能電器等領域,致力于建立物理世界與數字世界的安全聯結。憑借自主知識產權的電容智能分壓(iDivider)技術,實現國產數字隔離芯片的突破,匠心智造不一樣的隔離好產品,用“芯”創造新價值。

原文標題:技術課堂之十二 | 淺談latchup

文章出處:【微信公眾號:榮湃半導體】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

ESD

+關注

關注

49文章

2041瀏覽量

173111 -

MOS管

+關注

關注

108文章

2423瀏覽量

67064 -

latchup

+關注

關注

1文章

2瀏覽量

1170

原文標題:技術課堂之十二 | 淺談latchup

文章出處:【微信號:gh_fb935efbb3e1,微信公眾號:榮湃半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

MOS管的基本結構 MOS管的二級效應

MOS管種類和結構

分析MOS管發燙原因

mos管損壞的原因分析

MOS管的結構與latchup的形成原因

MOS管的結構與latchup的形成原因

評論