硬件加速器已經(jīng)在數(shù)據(jù)中心變得司空見慣,大量新的工作負(fù)載已經(jīng)成熟,可以利用 FPGA 加速的優(yōu)勢及其更高的計(jì)算效率。對機(jī)器學(xué)習(xí) (ML) 的快速增長的興趣正在推動在私有、公共和混合云數(shù)據(jù)中心環(huán)境中越來越多地采用 FPGA 加速器來加速這種計(jì)算密集型工作負(fù)載。作為促進(jìn) IT 基礎(chǔ)架構(gòu)向異構(gòu)計(jì)算轉(zhuǎn)型的一部分,我們最近與 VMware 合作在 vSphere上測試 FPGA 加速,VMware的云計(jì)算虛擬化平臺。鑒于賽靈思 FPGA 越來越多地用于 ML 推理加速,我們將展示如何將賽靈思 FPGA 與 VMware vSphere 結(jié)合使用,以實(shí)現(xiàn)虛擬和裸機(jī)部署之間幾乎相同的高吞吐量和低延遲 ML 推理性能。

自適應(yīng)計(jì)算優(yōu)勢

FPGA 是自適應(yīng)計(jì)算設(shè)備,可提供重新編程的靈活性以滿足所需應(yīng)用程序的不同處理和功能要求。這一特性將 FPGA 與 GPU 和 ASIC 等固定架構(gòu)區(qū)分開來——更不用說定制 ASIC 飛漲的成本了。此外,與其他硬件加速器相比,F(xiàn)PGA 在實(shí)現(xiàn)高能效和低延遲方面也具有優(yōu)勢,這使得 FPGA 特別適用于 ML 推理任務(wù)。與 GPU 從根本上依賴大量并行處理內(nèi)核來實(shí)現(xiàn)高吞吐量不同,F(xiàn)PGA 可以通過定制的硬件內(nèi)核、數(shù)據(jù)流管道和互連同時實(shí)現(xiàn) ML 推理的高吞吐量和低延遲。

在 vSphere 上使用 Xilinx FPGA 進(jìn)行 ML 推理

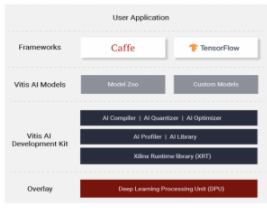

VMware 在他們的實(shí)驗(yàn)室中使用 Xilinx Alveo U250 數(shù)據(jù)中心卡 進(jìn)行測試。使用 Vitis AI中提供的 Docker 容器快速配置 ML 模型, Vitis AI是 Xilinx 統(tǒng)一開發(fā)堆棧,用于在 Xilinx 硬件平臺上從 Edge 到 Cloud 進(jìn)行 ML 推理。它由優(yōu)化的工具、庫、模型和示例組成。Vitis AI 支持主流框架,包括 Caffe 和 TensorFlow,以及能夠執(zhí)行各種深度學(xué)習(xí)任務(wù)的最新模型。此外,Vitis AI 是開源的,可以在 GitHub 上訪問。

Vitis AI 軟件堆棧

目前,Xilinx FPGA 可以通過 DirectPath I/O 模式(直通)在 vSphere 上啟用。通過這種方式,我們的 FPGA 可以被運(yùn)行在 VM 中的應(yīng)用程序直接訪問,繞過虛擬機(jī)管理程序?qū)樱瑥亩畲笙薅鹊靥岣咝阅懿⒆畲笙薅鹊販p少延遲。在 DirectPath I/O 模式下配置 FPGA 是一個簡單的兩步過程:首先,在主機(jī)級別啟用 ESXi 上的設(shè)備,然后將設(shè)備添加到目標(biāo) VM。詳細(xì)說明可在此 VMware 知識庫文章中找到。請注意,如果您運(yùn)行的是 vSphere 7,則不再需要重新引導(dǎo)主機(jī)。

高吞吐量、低延遲的機(jī)器學(xué)習(xí)推理性能

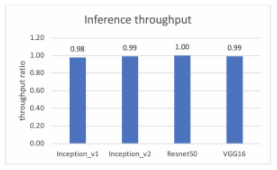

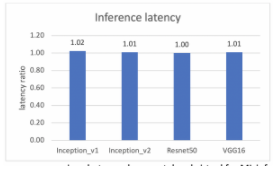

VMware 與 Xilinx 一起通過使用四個 CNN 模型運(yùn)行推理來評估我們的 Alveo U250 加速卡在 DirectPath I/O 模式下的吞吐量和延遲性能:Inception_v1;初始_v2;資源網(wǎng)50;和 VGG16。這些模型的模型參數(shù)數(shù)量不同,因此具有不同的處理復(fù)雜性。

測試使用了配備兩個 10 核 Intel Xeon Silver 4114 CPU 和 192 GB DDR4 內(nèi)存的 Dell PowerEdge R740 服務(wù)器。我們使用了 ESXi 7.0 管理程序,并將每個模型的端到端性能結(jié)果與作為基準(zhǔn)的裸機(jī)進(jìn)行了比較。Ubuntu 16.04(內(nèi)核 4.4.0-116)用作來賓操作系統(tǒng)和本機(jī)操作系統(tǒng)。此外,Vitis AI v1.1 和 Docker CE 19.03.4 用于整個測試。使用從 ImageNet2012 派生的 50k 圖像數(shù)據(jù)集,為了進(jìn)一步避免讀取圖像的磁盤瓶頸,創(chuàng)建了一個 RAM 磁盤并用于存儲 50k 圖像。

通過這些設(shè)置,虛擬和裸機(jī)測試之間的性能比較可以在以下兩張圖中查看,一張用于吞吐量,另一張用于延遲。y 軸是虛擬機(jī)和裸機(jī)之間的比率,y=1.0 表示虛擬機(jī)和裸機(jī)的性能相同。

Xilinx Alveo U250 FPGA 機(jī)器學(xué)習(xí)推理的裸機(jī)和虛擬機(jī)吞吐量性能比較

Xilinx Alveo U250 FPGA 機(jī)器學(xué)習(xí)推理的裸機(jī)和虛擬機(jī)延遲性能比較

測試驗(yàn)證了虛擬機(jī)和裸機(jī)之間的性能差距上限為 2%,無論是吞吐量還是延遲。這表明在虛擬環(huán)境中用于 ML 推理的 vSphere 上的 Alveo U250 的性能幾乎與裸機(jī)基準(zhǔn)相同。

云中的 FPGA 性能

FPGA 加速器在數(shù)據(jù)中心的采用正變得越來越普遍,并將繼續(xù)增加以滿足對異構(gòu)計(jì)算和性能提升的日益增長的需求。我們很高興與 VMware 合作,以確保客戶能夠充分利用 vSphere 平臺上的 Xilinx FPGA 加速。我們的 Alveo U250 加速器在 vSphere for ML inference 上的測試成功地向客戶展示了通過 DirectPath I/O 模式實(shí)現(xiàn)的接近原生的性能。審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1629文章

21748瀏覽量

603993 -

數(shù)據(jù)中心

+關(guān)注

關(guān)注

16文章

4792瀏覽量

72184 -

機(jī)器學(xué)習(xí)

+關(guān)注

關(guān)注

66文章

8422瀏覽量

132743

發(fā)布評論請先 登錄

相關(guān)推薦

Netflix起訴博通,指控VMware虛擬機(jī)專利侵權(quán)

芯華章發(fā)布FPGA驗(yàn)證系統(tǒng)新品HuaProP3

芯華章推出新一代高性能FPGA原型驗(yàn)證系統(tǒng)

國產(chǎn)EDA公司芯華章科技推出新一代高性能FPGA原型驗(yàn)證系統(tǒng)

AMD Alveo V80計(jì)算加速器網(wǎng)絡(luò)研討會

數(shù)字芯片設(shè)計(jì)驗(yàn)證經(jīng)驗(yàn)分享(第三部分):將ASIC IP核移植到FPGA上——如何確保性能與時序以完成充滿挑戰(zhàn)的

在多FPGA集群上實(shí)現(xiàn)高級并行編程

借助全新 AMD Alveo? V80 計(jì)算加速卡釋放計(jì)算能力

fpga原型驗(yàn)證平臺與硬件仿真器的區(qū)別

fpga原型驗(yàn)證流程

fpga驗(yàn)證和測試的區(qū)別

fpga驗(yàn)證和uvm驗(yàn)證的區(qū)別

在FPGA上為FPGA設(shè)計(jì)PCB的步驟詳解

VMware在vSphere上驗(yàn)證Alveo FPGA性能

VMware在vSphere上驗(yàn)證Alveo FPGA性能

評論