前言

硅通孔(Through Silicon Via,TSV)技術是一項高密度封裝技術,它正在逐漸取代目前工藝比較成熟的引線鍵合技術,被認為是第四代封裝技術。在2.5D/3D IC中TSV被大規模應用于芯片和封裝基板的互連,以及芯片和芯片的互連。TSV技術通過銅、鎢、多晶硅等填充,實現垂直電氣互連。硅通孔技術可以通過垂直互連減小互聯長度,降低信號延遲,降低寄生電容/電感,實現芯片間的低功耗、高速、寬帶通信和實現器件集成的小型化。

在結構上,TSV的仿真模型一般可以簡化為導電柱、種子層和隔離氧化層。TSV互連填充主要依靠電鍍銅的方式進行。一般來說,在電鍍前,孔內和表面需要導電的種子層覆蓋,一般會以鈦和銅為種子層,超高深徑比或特殊結構可能需要采用金種子層。種子層是電鍍的基本保障,在確保電鍍順利的同時提供導電特性。

本文介紹了采用芯和半導體ViaExpert軟件進行TSV陣列的建模和仿真分析流程。TSV結構復雜,存在建模繁瑣、分析不便等問題。對經常從事TSV仿真的工程師來說,如何利用工具模板快速對TSV陣列進行建模并仿真顯得特別重要。

TSV陣列建模流程

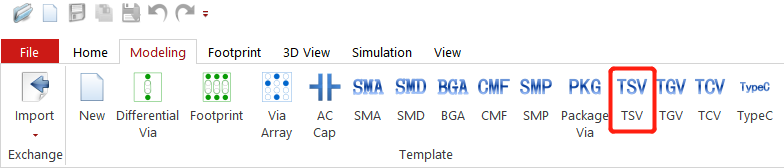

1. 調用TSV模板

首先我們打開ViaExpert工具,選擇菜單欄ModelingTemplateTSV圖標;

圖1:TSV模板選擇

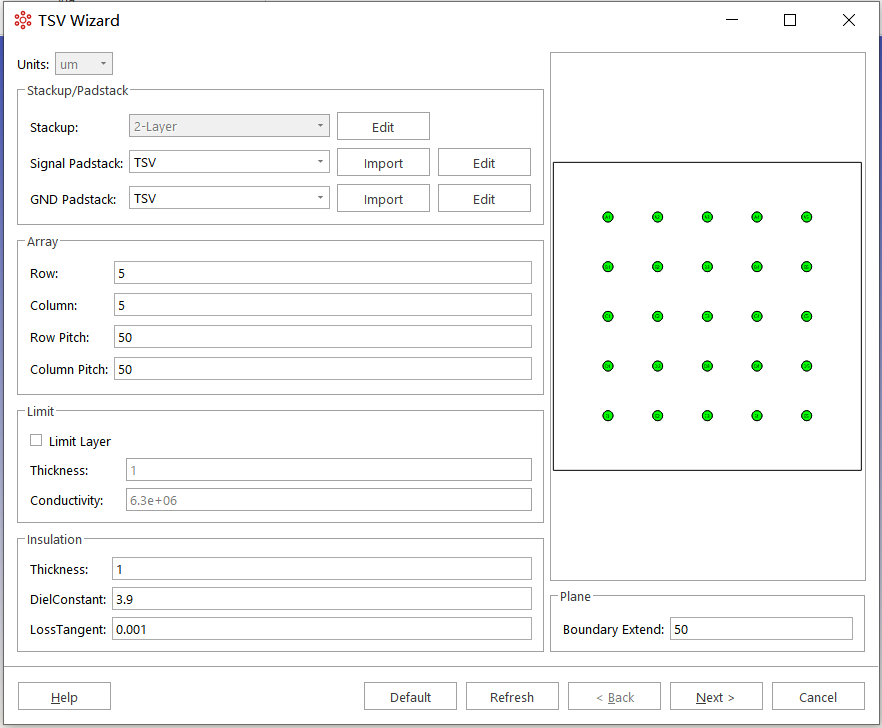

點擊TSV圖標后,可進入TSV建模向導界面;

圖2:TSV向導窗口

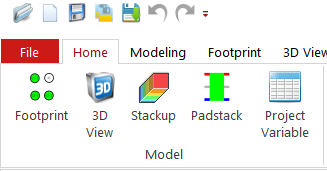

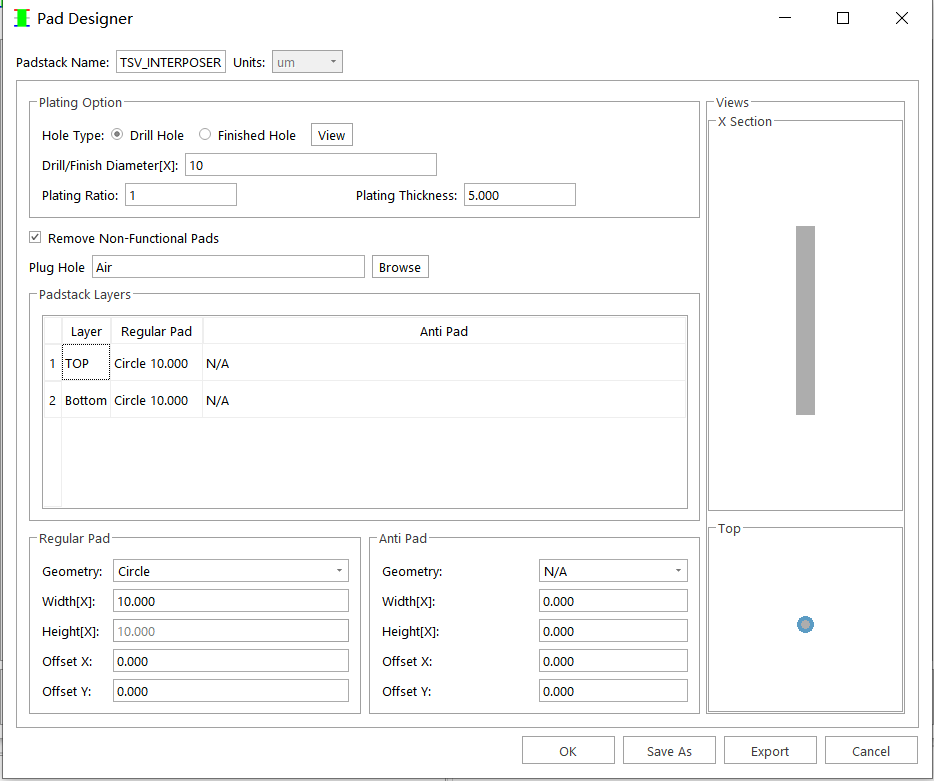

接下來點擊TSV Wizard中的Padstack/ Edit或者在Home 菜單下進入“Padstack”,根據TSV的信息設置Padstack的尺寸;

圖3:Home菜單

在Pad Designer中Regular Pad為TSV的直徑,Hole的尺寸可以根據TSV的結構進行設置,如果是100%的導電柱結構,則設置為和Regular Pad一樣的Drill 尺寸。詳細的俯視圖和側視圖可以在窗口的右邊進行Preview。

圖4:Pad Designer

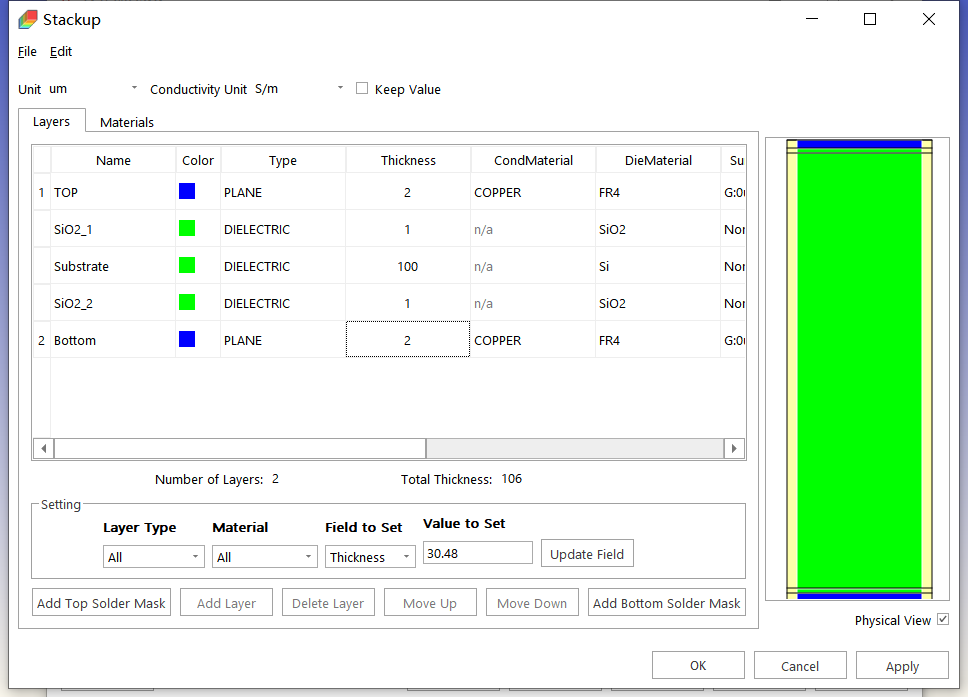

3. Stackup和Materials 設置

點擊TSV Wizard中的Stackup/ Edit進入Stackup編輯界面,在該界面下用戶可以根據硅材料的厚度來進行TSV高度的設置,通常在Si interposer中TSV厚度為50至100um不等。需要注意的是,在Materials編輯窗口中用戶必須指定Si和SiO2的材料屬性,尤其是Si作為半導體既需要定義Conductivity也需要定義Dk和Df值,這樣確保仿真結果能夠模擬真實材料特性對TSV所造成的影響。

圖5:Stackup編輯窗口

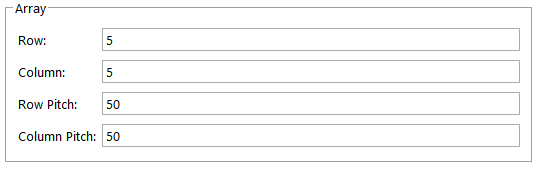

4. TSV Array 設置

在TSV Wizard中的Array編輯區域,用戶可以指定TSV陣列的數量和間距,在此案例中我們按照下列參數進行設置:

圖6:TSV Array編輯

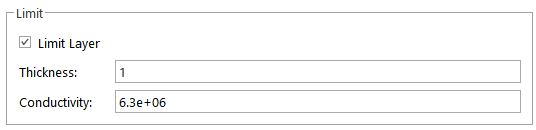

5. Limit Layer 設置

在TSV Wizard中的Limit Layer編輯區域;用戶可以指定TSV種子層的金屬厚度和電導率參數,因為其對結果影響微乎其微,一般在簡化模型中也可不考慮此結構的影響。

圖7:Limit Layer編輯

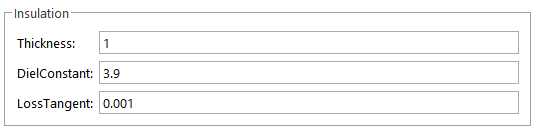

6. Insulation Layer 設置

在TSV Wizard中的Insulation編輯區域,用戶可以指定TSV隔離氧化層的厚度和氧化物的Dk、Df值。在TSV的特性中,隔離氧化層對電性能影響較大,尤其在氧化層厚度較小時,導電柱和Silicon之間形成較大寄生電容,讓信號的損耗隨著頻率上升急劇增加。

圖8:Insulation Layer編輯

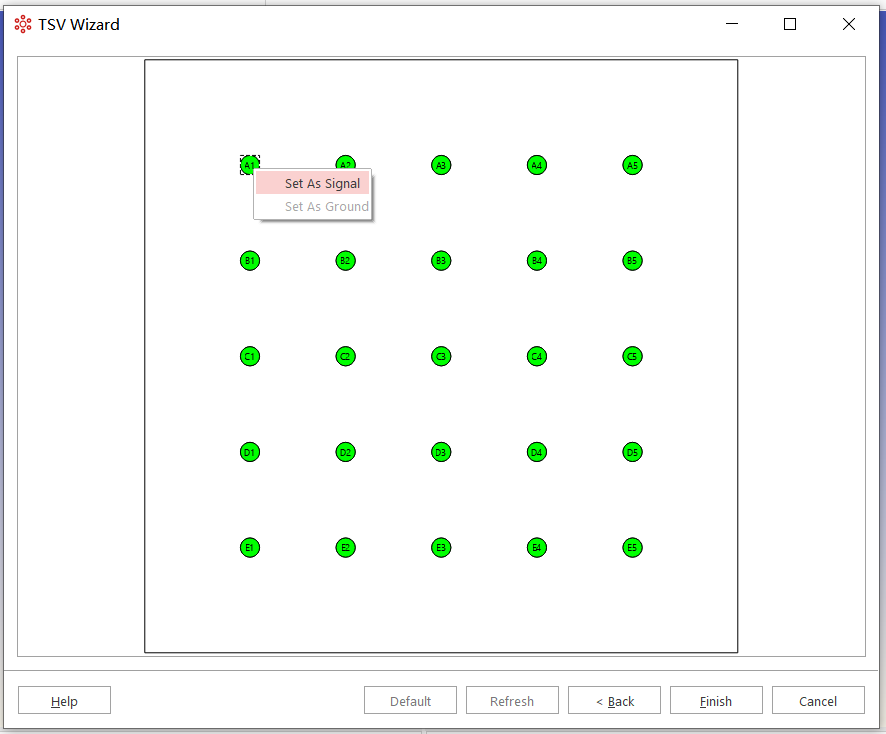

7. TSV Type 設置

在設置好以上參數以及模型的Boundary尺寸以后,點擊Next,進入TSV種類的選擇,用戶可以根據設計需要將TSV陣列中TSV修改為Signal或者Ground類型。

圖9:TSV類型編輯

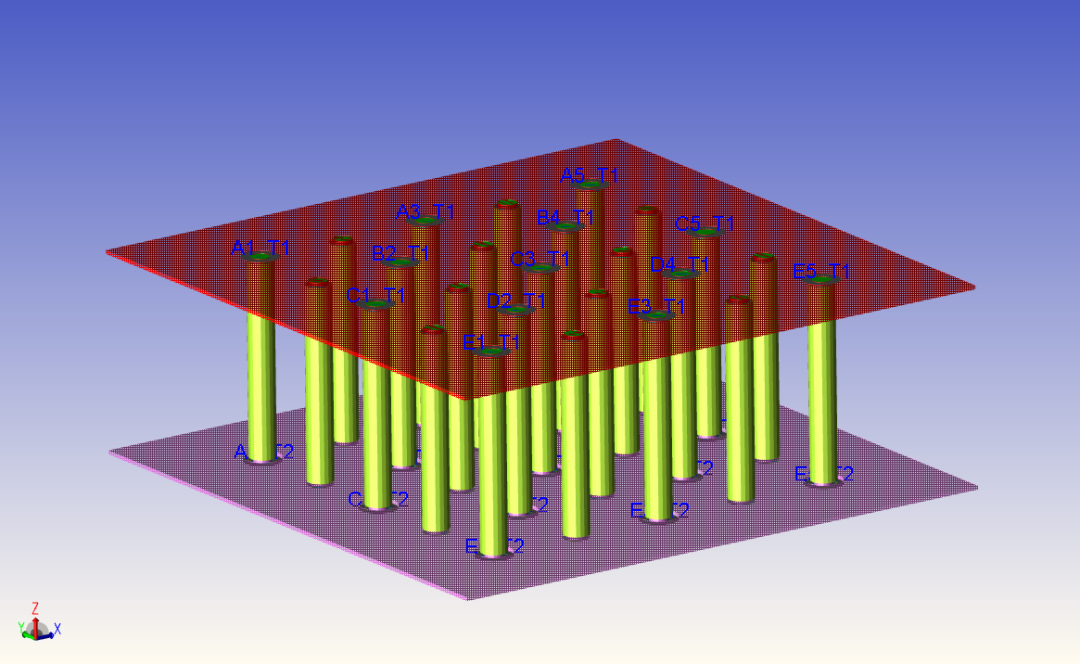

點擊Finish,即可完成TSV陣列的建模,仿真模型的Port會自動進行添加。

圖10:TSV陣列3D視圖

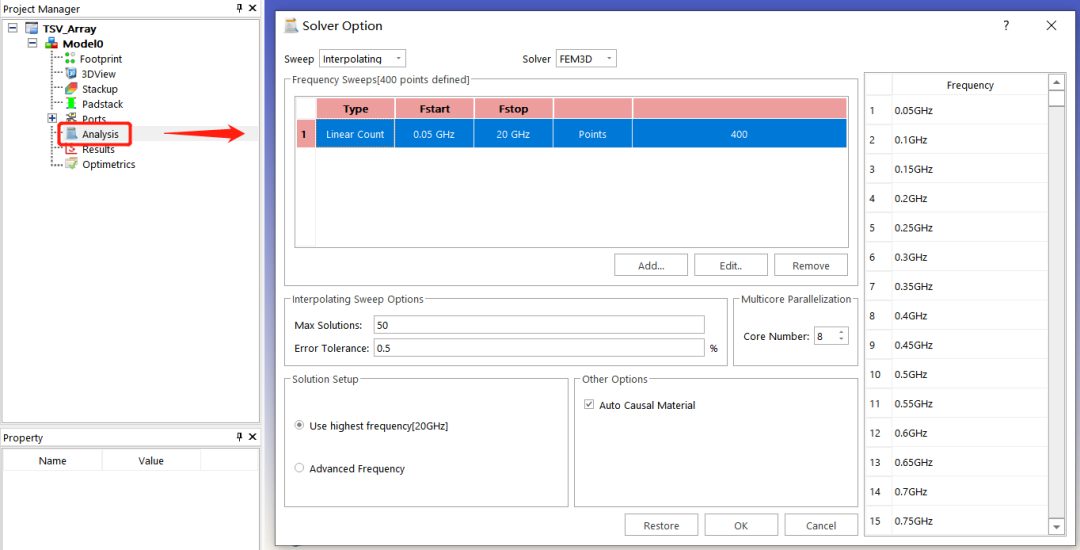

8. 求解器設置和啟動

在Project Manager中右鍵Analysis進入Solver Option界面,用戶可以根據要求選擇S參數掃頻范圍、收斂條件以及Core Number等設置。

圖11:求解器設置界面

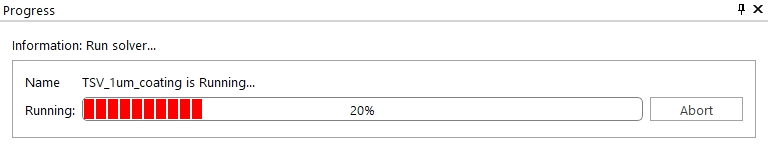

在Project Manager中右鍵Analysis,選擇Run Solver,求解器將開始對整個TSV陣列的結構進行S參數求解。在Progress的狀態欄里可以查看仿真的進度。

圖12:仿真進度窗口

9. 仿真結果查看

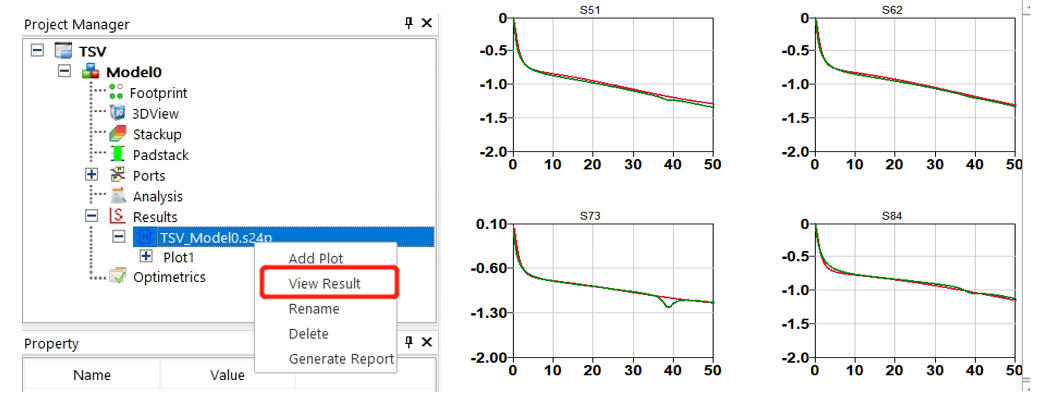

仿真完成以后,在Project Manager中Results下方會生成相應S參數結果,右鍵選擇View Result可在SnpExpert中對仿真結果進行查看和分析。

圖13:S參數分析窗口

總結本文介紹了采用芯和半導體ViaExpert軟件進行TSV陣列建模與仿真分析的完整流程,步驟包括:Padstack編輯、Stackup和Materials編輯、陣列編輯、隔離層設置、TSV類型選擇等。通過預制模板的方式建立TSV陣列,用戶可以有效地提高TSV建模和仿真效率,加快芯片的設計和迭代。

原文標題:【應用案例】如何進行“TSV陣列的建模和仿真”?

文章出處:【微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

-

建模

+關注

關注

1文章

315瀏覽量

61197 -

TSV

+關注

關注

4文章

117瀏覽量

81731 -

viaexpert

+關注

關注

0文章

3瀏覽量

1929 -

芯和半導體

+關注

關注

0文章

117瀏覽量

31627

原文標題:【應用案例】如何進行“TSV陣列的建模和仿真”?

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何使用串口工具連接OneNET上報數據AT命令流程的代碼詳細說明

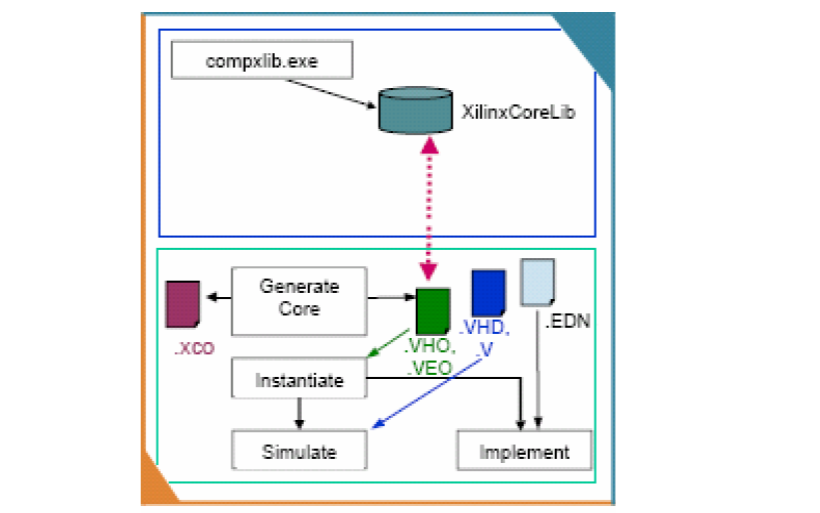

FPGA設計的全部流程詳細說明

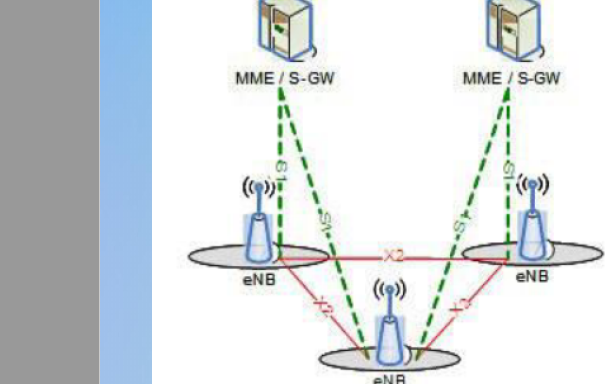

LTE簇優化流程和案例介紹詳細說明

評論