當(dāng)你想到它時,這是一個有趣的舊世界。您可能知道也可能不知道,我的學(xué)位是控制工程(現(xiàn)在稱為系統(tǒng)工程)。該課程包括數(shù)學(xué)專業(yè)和電子、機械、液壓和流體學(xué)的輔修課程(不要問我們在業(yè)余時間做了什么)。

盡管我涉足編寫軟件,但我專注于以奇怪而奇妙的方式創(chuàng)建代碼失敗。我是一名硬件設(shè)計工程師。我的第一個職位是為大型計算機設(shè)計中央處理器 (CPU) 的團隊成員。

當(dāng) MPU 和 MCU 在 1970 年代首次出現(xiàn)時,絕大多數(shù)編寫軟件的人都是那些在“大鐵”大型機和小型機上工作的人。因此,主要是硬件工程師為基于 MPU/MCU 的嵌入式系統(tǒng)編寫原始程序。

當(dāng)然,這些天來,整個行業(yè)對軟件編碼的興趣不斷增加。事實上,2019 年賽靈思開發(fā)者論壇 (XDF) 的一位主題演講者指出,“工程蛋糕”現(xiàn)在由 80% 的軟件開發(fā)人員組成,而硬件設(shè)計人員僅占 20%。這可能表明我是一個垂死品種的成員,但我更愿意相信隨著歲月的流逝,我變得越來越特別。(小時候媽媽常說我很特別,我傻傻地把這當(dāng)成夸獎了也是一種贊美。)

如果您在無人看的情況下快速使用 Google,您會看到估計全世界大約有 2200 萬軟件開發(fā)人員。其中,大多數(shù)專注于應(yīng)用程序級和基礎(chǔ)設(shè)施級編碼,僅剩下大約 120 萬個專注于嵌入式系統(tǒng)。

反過來,絕大多數(shù)嵌入式軟件開發(fā)人員專注于 MPU 和 MCU 的編碼;很少有人有使用現(xiàn)場可編程門陣列 (FPGA) 的經(jīng)驗。這是不幸的,因為盡管常規(guī)處理器非常適合執(zhí)行決策和控制雜務(wù),但在執(zhí)行許多數(shù)據(jù)處理任務(wù)時它們的效率非常低。相比之下,F(xiàn)PGA 能夠以大規(guī)模并行方式執(zhí)行復(fù)雜的數(shù)據(jù)處理任務(wù),從而使它們能夠提供顯著的算法加速。

在許多情況下,理想的解決方案是將常規(guī)處理器的決策和控制能力與在 FPGA 可編程結(jié)構(gòu)中實現(xiàn)的硬件加速器提供的算法處理能力相結(jié)合。為了促進這一點,賽靈思創(chuàng)建了 Zynq 系列 SoC FPGA,它將硬化處理器內(nèi)核與可編程結(jié)構(gòu)相結(jié)合。例如,Zynq 7020 提供雙核 667 MHz 32 位 Arm Cortex-A9 處理器(帶有緩存和浮點單元)以及 13,333 個可編程邏輯片。

唯一的問題是如何將 FPGA 的優(yōu)勢提供給沒有時間了解 FPGA 并且對此沒有興趣的軟件開發(fā)人員。解決方案是具有 SYZYGY 兼容擴展的 Digilent 的Eclypse Z7 開發(fā)板。

除了前面提到的 Zynq 7020,Eclypse Z7 還擁有 1 GB DDR3L 內(nèi)存、一個 MicroSD 卡插槽和一個千兆以太網(wǎng)接口。高速儀器、醫(yī)療設(shè)備、軟件定義無線電 (SDR) 和許多其他應(yīng)用的嵌入式系統(tǒng)開發(fā)人員特別感興趣的是,除了兩個 Pmod 接口之外,Eclypse Z7 還提供兩個 Zmod 接口.

直到最近,任何想要對基于 FPGA 的新系統(tǒng)進行原型設(shè)計或開發(fā)的人都受到兩種最常用擴展方案的能力的限制:Pmod和FMC。Pmod(外圍模塊)接口是由 Digilent 定義的開放標(biāo)準(zhǔn),并已在整個行業(yè)中廣泛采用。Pmod 非常適合 1 至 50 MHz 范圍內(nèi)的低速外設(shè);6 針、8 針和 12 針連接器的實施成本低廉;并且有許多現(xiàn)成可用的低成本外圍模塊。

另一端是 ANSI/VITA FMC(FPGA 夾層卡)標(biāo)準(zhǔn),它更適合數(shù)據(jù)速率高達 10 Gbps 的高性能外設(shè)。在這種情況下,72 針和 200 針連接器要貴得多,外圍設(shè)備本身的成本可能高達數(shù)千美元。

為了彌補這一差距,Opal Kelly的人們創(chuàng)建了 SYZYGY(發(fā)音為“Sizz-Uh-Gee”)開放標(biāo)準(zhǔn),用于將高性能外設(shè)連接到 FPGA 硬件。(另請參閱SYZYGY 起源故事。)SYZYGY 滿足了 FPGA 和硬件外圍設(shè)備之間對高速數(shù)據(jù)采集、數(shù)字圖像捕獲、軟件等應(yīng)用所需的緊湊、低成本、低引腳數(shù)、高性能連接解決方案的需求- 定義無線電和數(shù)字通信。

目前,有兩個 Digilent SYZYGY 模塊可供使用:一個雙通道、14 位、每秒 100 兆采樣 (Msps) 模數(shù)轉(zhuǎn)換器 (ADC),以及一個相應(yīng)的雙通道 14 位數(shù)字轉(zhuǎn)模擬轉(zhuǎn)換器(DAC)。這些模塊可以單獨購買,也可以與 Eclypse Z7 捆綁購買。

但等等,還有更多,因為強大的 Eclypse Z7 硬件由創(chuàng)新的軟件架構(gòu)支持,允許軟件開發(fā)人員涉足 FPGA 領(lǐng)域。

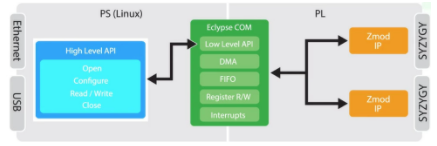

在 Zynq-7020 SoC FPGA 中,器件的編程系統(tǒng) (PS) 部分——即雙核 32 位 Arm Cortex-A9 處理器——連接到系統(tǒng)的可編程邏輯 (PL) 部分使用高速 AXI 總線。這意味著在 PL 中實現(xiàn)的外圍功能和硬件加速器可以輕松地與在 PS 上運行的軟件進行通信。

Eclypse Z7 軟件架構(gòu)

Eclypse Z7 的軟件架構(gòu)包括預(yù)構(gòu)建的 Linux 映像以及軟件開發(fā)人員可以使用熟悉的編程語言訪問的高級 API。這使開發(fā)人員能夠利用 FPGA 硬件加速的優(yōu)勢,而不必直接與 FPGA 本身進行交互。

我只能說,對于想要享受 FPGA 提供的優(yōu)勢而無需真正了解 FPGA 的嵌入式軟件開發(fā)人員來說,這是一個激動人心的時刻。更令人興奮的是,Digilent 正在向我們征求我們認為下一步應(yīng)該將哪些外圍功能實現(xiàn)為 Zmod 模塊的建議。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603029 -

嵌入式

+關(guān)注

關(guān)注

5082文章

19110瀏覽量

304841 -

API

+關(guān)注

關(guān)注

2文章

1499瀏覽量

61969

發(fā)布評論請先 登錄

相關(guān)推薦

MSPDebugStack開發(fā)人員指南

正點原子fpga開發(fā)板不同型號

ARM開發(fā)板與FPGA的結(jié)合應(yīng)用

用戶手冊 | 全志T113-S3開發(fā)板——SDK編譯指南

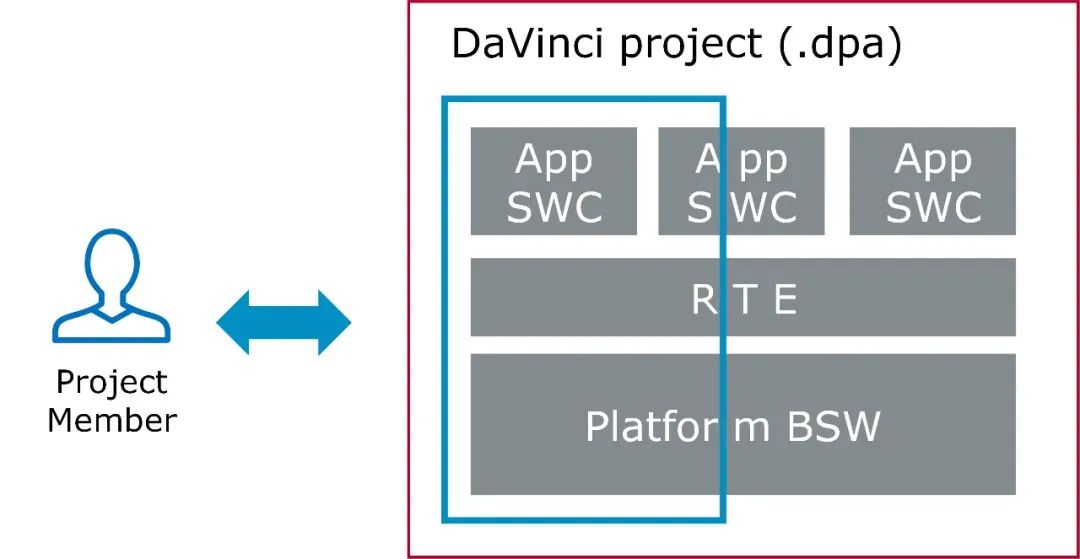

Vector DaVinci Team解決方案實現(xiàn)AUTOSAR Classic ECU軟件開發(fā)

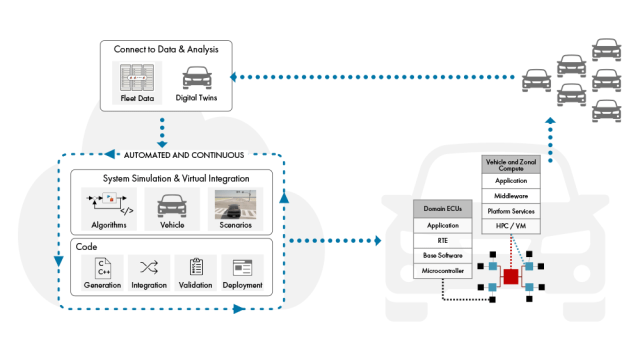

使用MATLAB、Simulink和Polyspace加速軟件定義汽車開發(fā)

《軟件開發(fā)珠璣》+60條戒律

FPGA核心板 Xilinx Artix-7系列XC7A100T開發(fā)平臺,米爾FPGA工業(yè)開發(fā)板

fpga開發(fā)板是什么?fpga開發(fā)板有哪些?

FRDM-MCXA153開發(fā)板的開箱體驗

Eclypse Z7開發(fā)板讓軟件開發(fā)人員了解FPGA

Eclypse Z7開發(fā)板讓軟件開發(fā)人員了解FPGA

評論