業(yè)界正在接受嵌入式現(xiàn)場(chǎng)可編程門陣列 (eFPGA),因?yàn)樵摷夹g(shù)已在多個(gè)流行工藝節(jié)點(diǎn)的硅片中可用并得到驗(yàn)證。eFPGA 正在以多種方式集成到芯片中,包括作為可重新配置的 I/O 處理器或加速器,在數(shù)據(jù)路徑或控制路徑中。這種方法的好處是它通過(guò)不將加速器綁定到固定功能來(lái)提供靈活性。

為此,芯片設(shè)計(jì)人員可以創(chuàng)建從 eFPGA 到 ARM 架構(gòu)的高級(jí)外圍總線 (APB)、AMBA 高性能總線 (AHB) 和 AMBA 高級(jí)可擴(kuò)展接口 (AXI) 總線的連接,從最簡(jiǎn)單的接口到APB 從機(jī)到最復(fù)雜的 AXI 主機(jī)。

隨著網(wǎng)絡(luò)、深度學(xué)習(xí)和人工智能 (AI) 以及航空航天和國(guó)防等應(yīng)用對(duì)硬件加速的需求不斷增長(zhǎng),對(duì)片上系統(tǒng) (SoC) 和微控制器 (MCU) 設(shè)計(jì)的需求也在不斷發(fā)展。如今,常見(jiàn)的 SoC 具有集成數(shù)字信號(hào)處理 (DSP) 和 FPGA IP 塊,專用于特定 I/O 或處理工作負(fù)載,而主 CPU 內(nèi)核處理通用任務(wù)。這些架構(gòu)支持更高效、更靈活的整體處理解決方案。

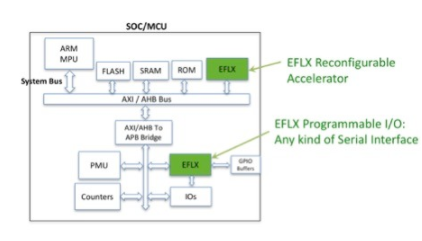

尤其是 eFPGA,由于上述原因,最近越來(lái)越受歡迎。與傳統(tǒng)的 DSP 和 FPGA 不同,eFPGA 可以作為可重新配置的 IP 塊設(shè)計(jì)到芯片中,可以重新編程以處理不同的工作負(fù)載加速任務(wù)或在芯片組的整個(gè)生命周期內(nèi)管理不同的 I/O(圖 1)。

圖 1. Flex Logix 的 EFLX eFPGA IP 可以在 MCU 和 SoC 設(shè)計(jì)中實(shí)現(xiàn)為可重新配置的硬件加速塊或可重新編程的 I/O 塊。]

例如,對(duì)于使用 ARM 架構(gòu)的芯片設(shè)計(jì)人員,eFPGA 可以連接到 APB、AHB 或 AXI 處理器總線以利用這些優(yōu)勢(shì)。但是,考慮到多種組合(主/從 x AXI/AHB/APB x 外部接口邏輯或使用 eFPGA 實(shí)現(xiàn)),應(yīng)仔細(xì)考慮這些設(shè)計(jì)。

eFPGA I/O 資源

為了更好地了解如何使用標(biāo)準(zhǔn)接口將 eFPGA 設(shè)計(jì)成基于 ARM 的 MCU 或 SoC,我們將以 Flex Logix EFLX-2.5K 嵌入式 FPGA IP 內(nèi)核為例。

EFLX-2.5K eFPGA 是一個(gè) 1x1 陣列,由 2,520 個(gè)具有 632 個(gè)輸入和 632 個(gè)輸出的六輸入查找表 (LUT) 組成。它在 16 nm 工藝中的工作頻率約為 1 GHz,在 28 nm 工藝中優(yōu)于 500 MHz。因此,即使是最小的 eFPGA 也具有足以連接到最寬、最快的 ARM 總線的 I/O 資源和速度。

(注意:最大 7x7 的更大數(shù)組是可能的,每個(gè)增加的數(shù)組大小的 I/O 數(shù)量計(jì)算為 NxM 數(shù)組中的 N*632 輸入和 N*632 輸出。增加數(shù)組大小的 LUT 數(shù)量類似計(jì)算為 N*M*2520。)

eFPGA 作為 APB 從機(jī)

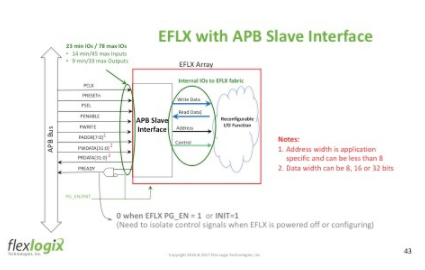

配置為 APB 從機(jī)的 eFPGA 通常會(huì)實(shí)現(xiàn)為可重新配置的 I/O 功能。例如,多種串行接口中的一種可以包括 UART、I2C 和 SPI。

在這種配置中,多個(gè)模塊連接到 APB 總線,該總線一次在一個(gè)模塊上運(yùn)行(圖 2)。每個(gè)塊都有內(nèi)存映射的地址空間(例如 128 個(gè)寄存器的 8 位),而總線上的數(shù)據(jù)可以是 8、16 或 32 位。8 位地址空間和 32 位數(shù)據(jù)需要 45 個(gè)輸入和 33 個(gè)輸出,而 16 位總線使用更少的 16 個(gè)輸入和 16 個(gè)輸出。

圖 2.配置為 APB 從機(jī)的 eFPGA 通常實(shí)現(xiàn)為包含多個(gè)存儲(chǔ)器映射塊的可配置 I/O 功能。APB 總線在每一個(gè)上同步運(yùn)行。

APB 從接口快速、簡(jiǎn)單,可以在外部實(shí)現(xiàn),也可以在 eFPGA 的邏輯中實(shí)現(xiàn)。例如,在此配置中,EFLX eFPGA 需要少于 10 個(gè) LUT。如圖 3 所示,APB 從接口 Verilog 代碼和狀態(tài)圖也很簡(jiǎn)短。

圖 3.當(dāng) eFPGA 配置為 APB 從接口時(shí),Verilog 代碼和狀態(tài)圖很簡(jiǎn)單。

eFPGA 作為 AXI 主機(jī)

AXI 總線由三個(gè)版本組成:AXI4、AXI4 Stream 和 AXI4 Lite。

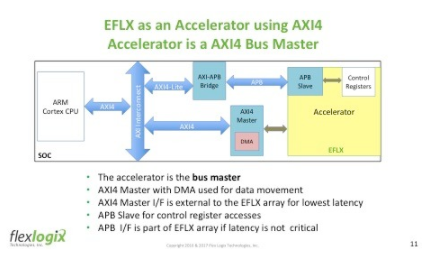

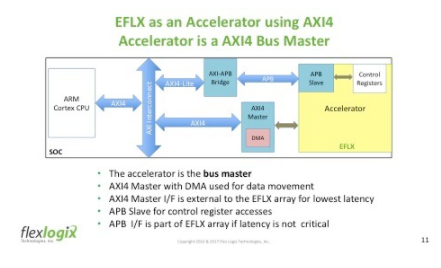

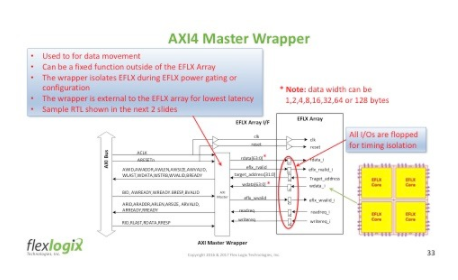

圖 4 顯示了具有在 eFPGA 外部實(shí)現(xiàn)的包裝器的 AXI4 主設(shè)備。AXI 主包裝器的功能是處理所有總線協(xié)議,管理數(shù)據(jù)流控制,并在配置期間將 EFLX FPGA 與 AXI 總線隔離。

在這里,EFLX Reconfigurable Accelerator 充當(dāng)總線主控器,因此 CPU 不需要向內(nèi)存?zhèn)鬏敂?shù)據(jù)和從內(nèi)存?zhèn)鬏敂?shù)據(jù)。這可以將 CPU 卸載到可以與 EFLX 加速器并行運(yùn)行的其他任務(wù)上。

圖 4.配置為 AXI 主設(shè)備的 EFLX 可重配置加速器可以減輕 CPU 的總線管理任務(wù)負(fù)擔(dān)。

EFLX eFPGA 能夠支持窄或非常寬(128 字節(jié))的 AXI 數(shù)據(jù)寬度,具體取決于加速器功能所需的帶寬。EFLX 陣列中的控制寄存器和 APB 從屬邏輯在 EFLX 陣列中實(shí)現(xiàn)并通過(guò) APB 總線進(jìn)行控制。圖 2 所示的 APB 從接口示例可以實(shí)現(xiàn)控制寄存器接口。

圖 5 顯示了 AXI 總線架構(gòu)的高級(jí)圖,說(shuō)明了主從連接。在將 eFPGA 實(shí)現(xiàn)為 AXI 主設(shè)備時(shí),應(yīng)始終翻轉(zhuǎn) eFPGA 以簡(jiǎn)化關(guān)閉、定時(shí)、輸入和輸出到/輸出。數(shù)據(jù)總線寬度可以是 1、2 或 4 字節(jié)等,最多 128 字節(jié)。

圖 5.為了簡(jiǎn)化 AXI 總線中的主從連接,建議對(duì) eFPGA 進(jìn)行翻轉(zhuǎn)。

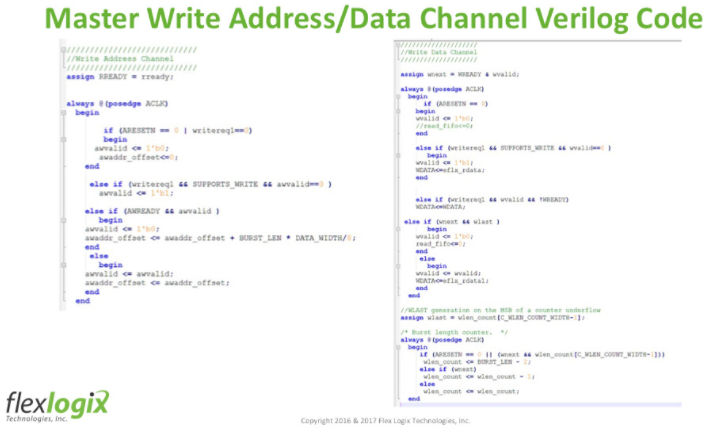

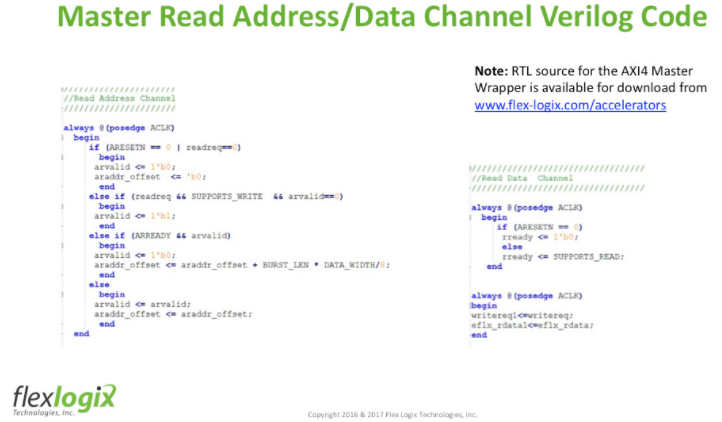

即使對(duì)于復(fù)雜的總線主控,Verilog 代碼也相對(duì)簡(jiǎn)單(圖 6)。

圖 6.使用 eFPGA 作為 AXI 總線主控器時(shí),Verliog 代碼仍然相對(duì)簡(jiǎn)單。

eFPGA 通過(guò)單獨(dú)的從接口

除了作為加速器或 I/O 處理器的陣列操作的總線連接之外,EFLX 等 eFPGA 還提供了一個(gè)單獨(dú)的從接口,用于加載配置位以根據(jù)需要進(jìn)行重新配置。外部 AXI 從包裝器也可用于與配置端口連接。

例如,使用 EFLX,配置位通常存儲(chǔ)在與 ARM 處理器代碼相同的閃存中。處理器啟動(dòng)后,它使用直接存儲(chǔ)器訪問(wèn) (DMA) 通過(guò)配置從接口將配置位訪問(wèn)到 eFPGA。

結(jié)論

隨著現(xiàn)代處理解決方案對(duì)靈活性和性能的需求日益增長(zhǎng),eFPGA 可以使用少量高速邏輯輕松連接到任何類型和寬度的 ARM 總線。經(jīng)過(guò)多年的復(fù)雜性和成本挑戰(zhàn),基于 eFPGA 技術(shù)的可重構(gòu)加速器和 I/O 處理器已成為任何基于 ARM 的 SoC 或 ASIC 架構(gòu)師的易于使用的資源。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19312瀏覽量

230038 -

asic

+關(guān)注

關(guān)注

34文章

1202瀏覽量

120528 -

寄存器

+關(guān)注

關(guān)注

31文章

5355瀏覽量

120517

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ARM架構(gòu)嵌入式主板特點(diǎn)

ARM嵌入式通信協(xié)議及應(yīng)用

ARM嵌入式編程高效技巧

歐時(shí)推介微芯嵌入式控制解決方案

嵌入式系統(tǒng)設(shè)計(jì)參考解決方案

嵌入式常用總線有哪些

ARM MCU嵌入式開(kāi)發(fā) | 基于國(guó)產(chǎn)GD32F10x芯片+嵌入的開(kāi)始

【「ARM MCU嵌入式開(kāi)發(fā) | 基于國(guó)產(chǎn)GD32F10x芯片」閱讀體驗(yàn)】+書籍整體概況

ARMxy ARM嵌入式計(jì)算機(jī)支持Ubuntu OS快速部署AIoT解決方案

ARMxy ARM嵌入式計(jì)算機(jī)搭載 1 TOPS NPU支持深度學(xué)習(xí)

嵌入式FPGA與ARM總線連接支持整體處理解決方案

嵌入式FPGA與ARM總線連接支持整體處理解決方案

評(píng)論